设计题目:多功能数字钟设计

设计要求:由振荡器输出稳定的高频脉冲信号作为时间基准,经分频振荡器输出标准的秒脉

冲,秒计数器满60向分计数器进位,分计数器满60向小时进位,小时计数器按“12翻1”规律计数,

计数器经译码器送到显示器;计数出现误差可用校时电路进行校时、校分、校秒。并具有可整

点报时与定时闹钟的功能。

设计方案:

1.用555定时器构成多谐振荡器,输出稳定的调频脉冲,作为时间基准。如下图

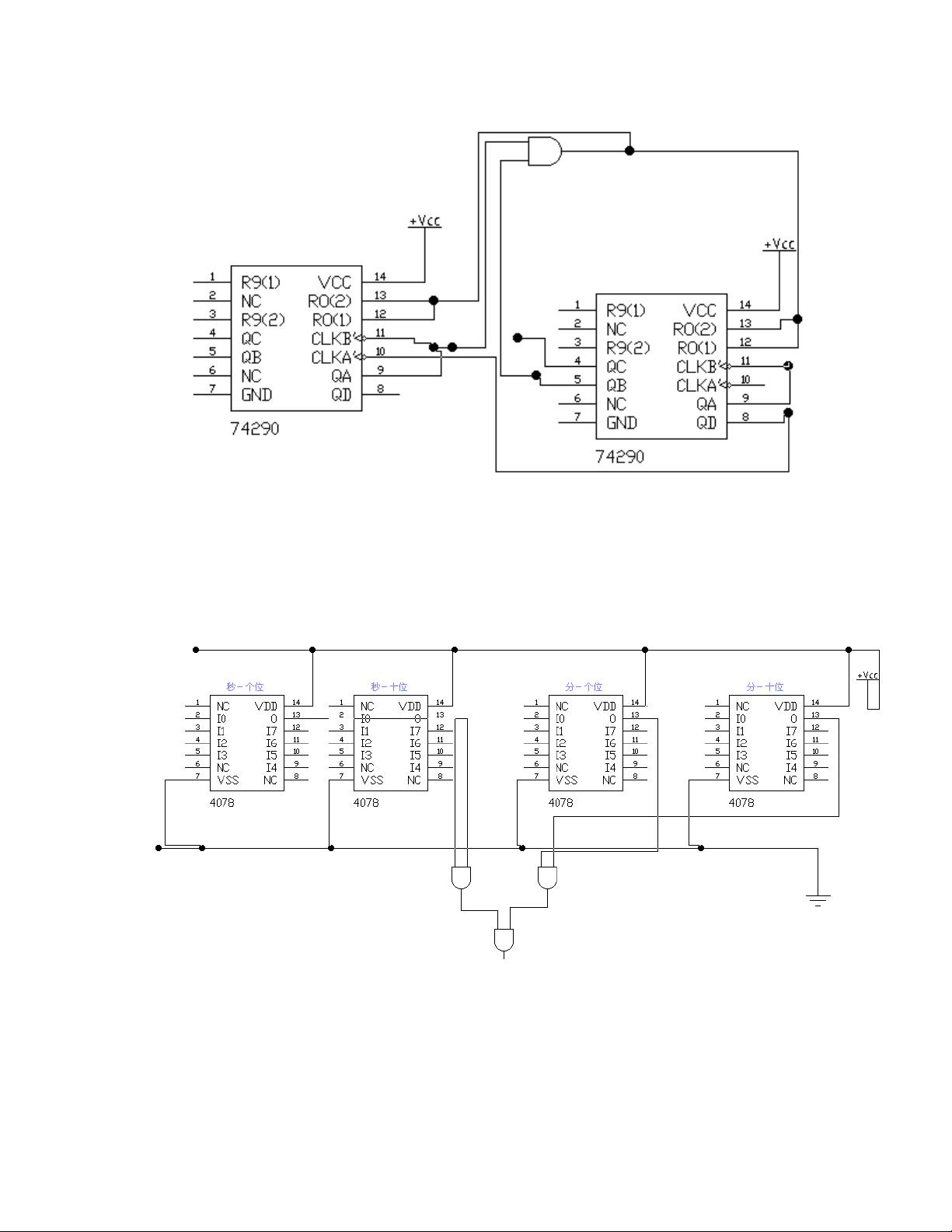

2.利用两片74290组成60进制递增计数器

利用两片74290组成的60进制计数器如下图所示,输入计数脉冲CP加在CLKA’端,把QA与

与CPLB’从外部连接起来,电路将对CP按照8421BCD码进行异步加法计数。通过反馈端,控制

清零端清零,其中个位接成十进制形式,十位接成六进制形式。

秒和分计数均由60进制递增计数器来完成。

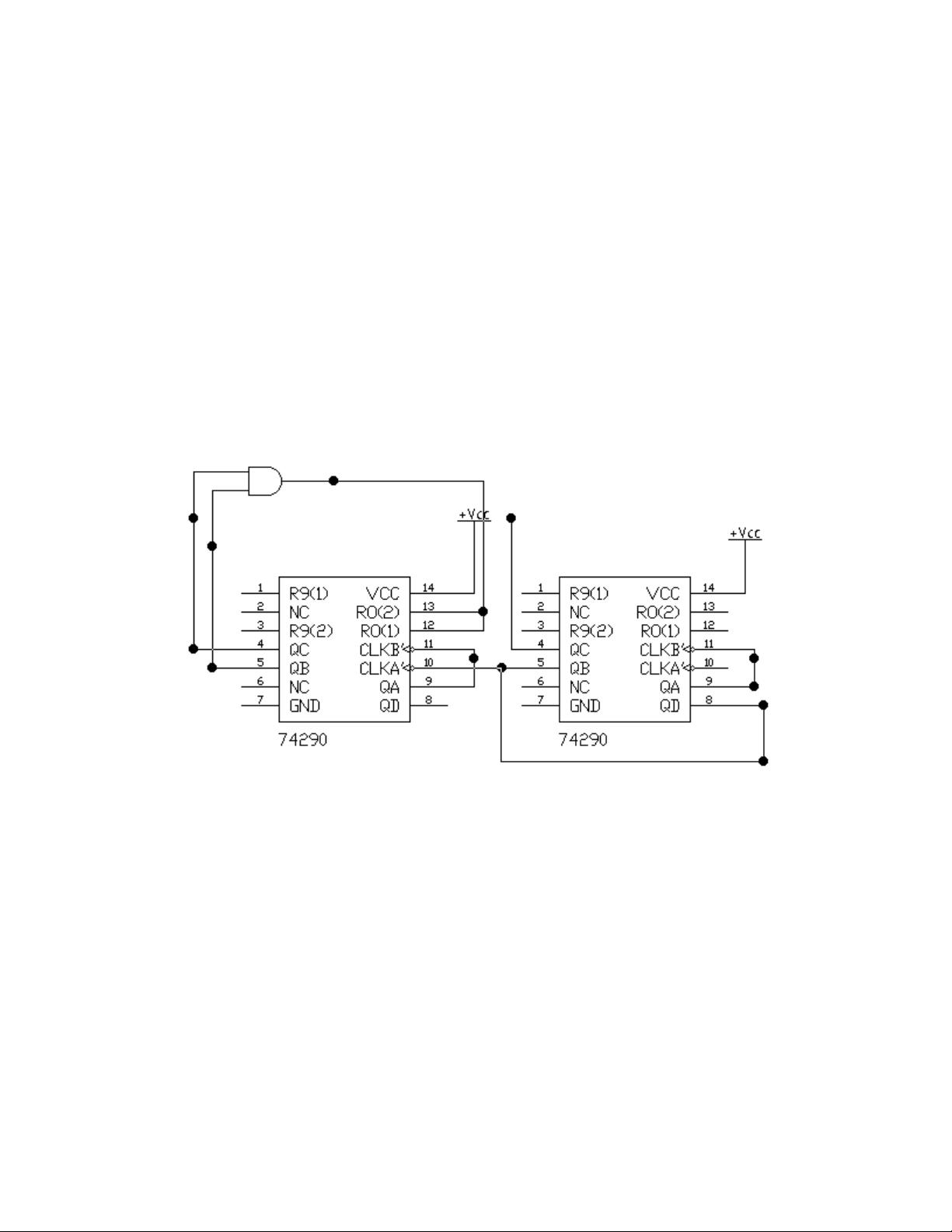

3.再用两片74290组成12进制递增计数器

个位同样接成十进制形式,十位通过QA与CLKB'外部连接,向显示屏间隔地输出“0”与“1”,

组成12进制递增计数器。如下图