72 Example 24

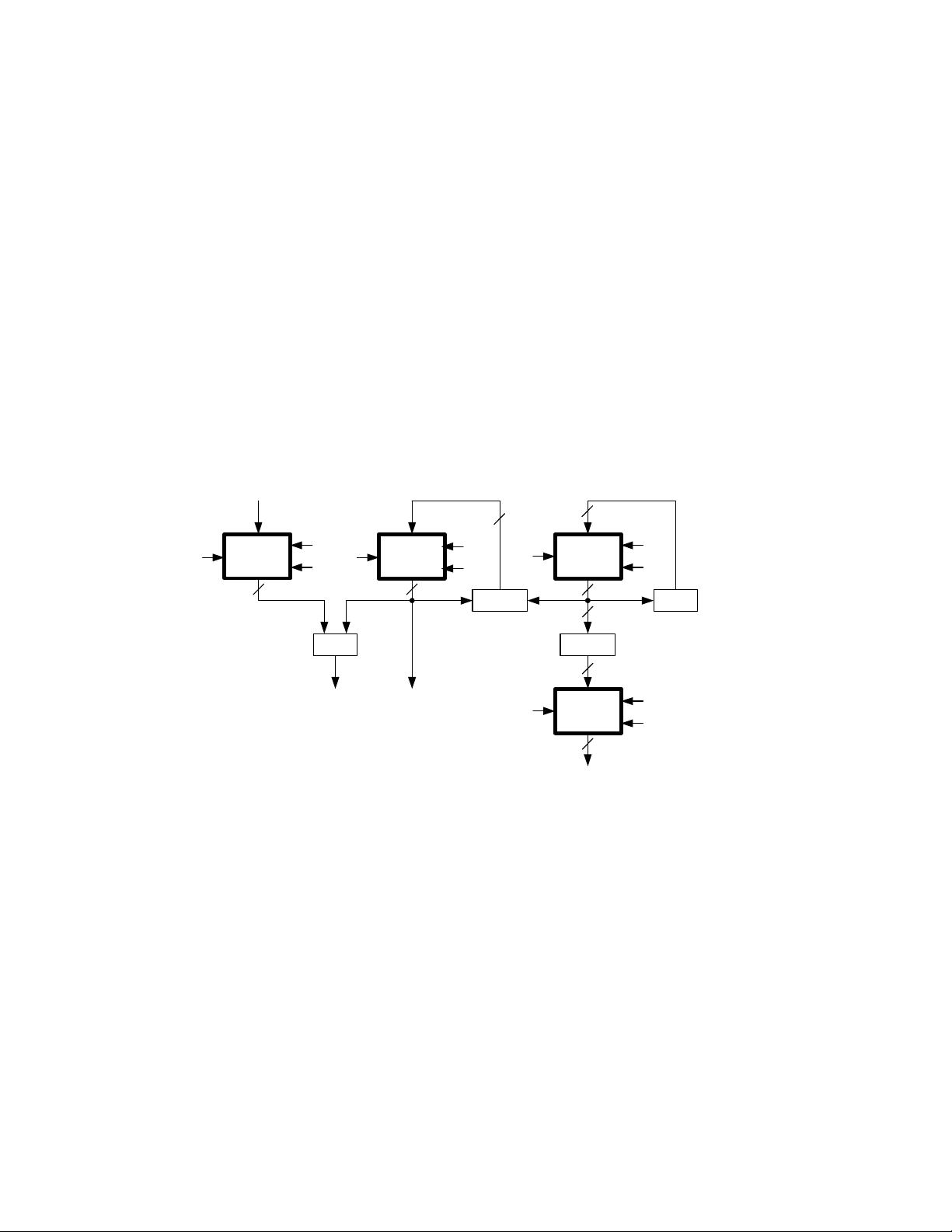

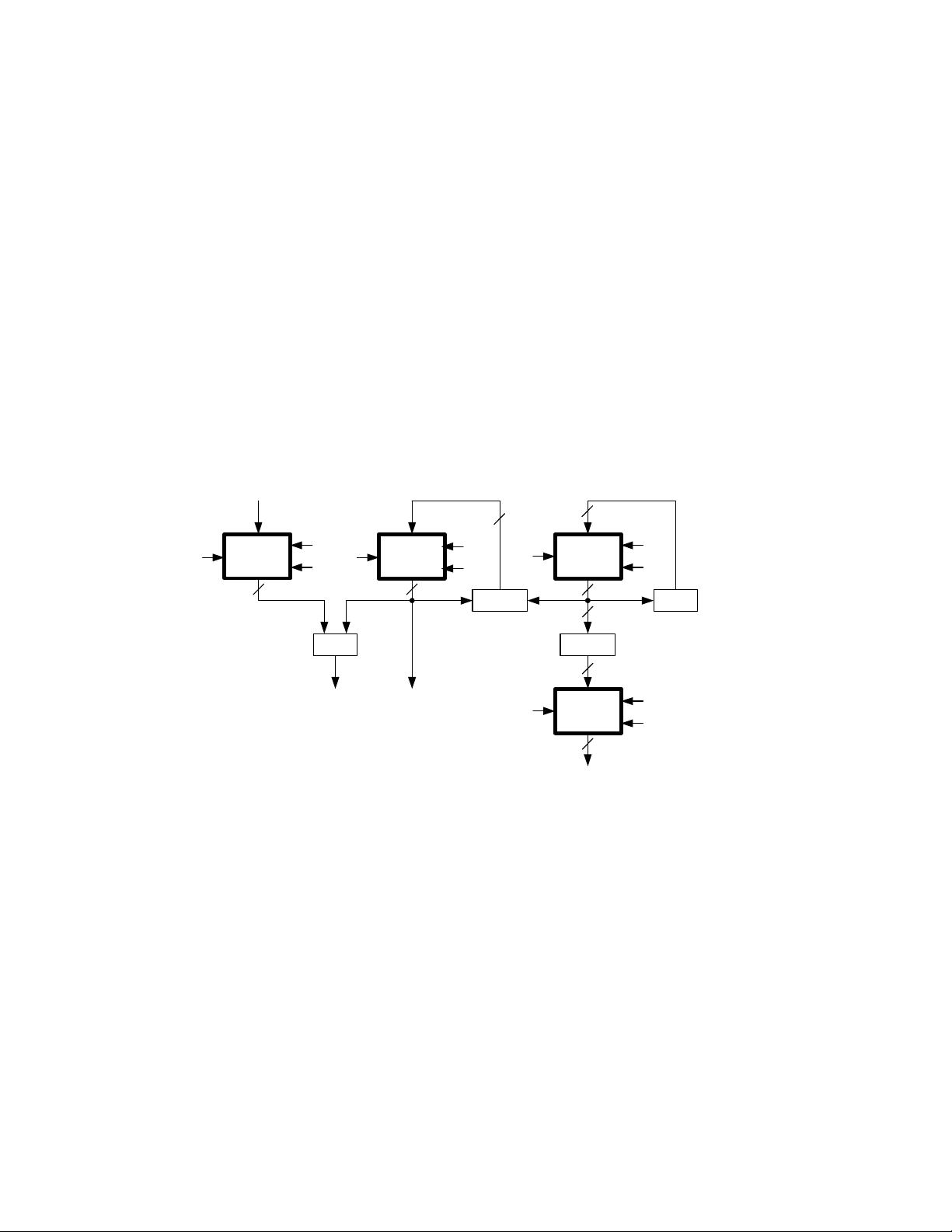

aReg sqReg delReg

outReg

<=

minus1

plus2

adder8

reset

clk

clr

clk

reset

clk

clr

clk

outld

ald sqld

dld

lteflg

root[3:0]

sw[7:0]

4

589

9

del[4:1]

4

5

4

square[7:0]

a[7:0]

square[7:0]

sq[8:0]

s[8:0]

del[4:0]

del2[4:0]

outin[3:0]

Our goal is to implement this algorithm in hardware using the same method that

we used in Example 23. The datapath for this square root algorithm is shown in Fig. 2.9.

We will limit the input value a[7:0] to eight bits so we can connect them to the eight

switches sw[7:0]. Thus, the register aReg will be an 8-bit register. From Table 2.1 the

maximum value of delta will be 33. This suggests that the size of the delta register

should be 6 bits. However, when we are done the final value of delta is divided by 2 and

then 1 is subtracted from this result. If the value is 33 but we only use a 5-bit register for

delta then the value in delta will be 1. When we divide this by 2 we will get 0, and when

we subtract 1 from 0 we get 11111, the lower four bits of which are equal to 15 – the

correct result. Thus, we can get by with a 5-bit register for delta. However, from Table

2.1 the maximum value of square in the algorithm will be 256, and therefore the square

register must be 9 bits wide. The maximum square root value will be 15 and thus the

output will be stored in a 4-bit register.

In addition to the four registers aReg, sqReg, delReg, and outReg, this datapath

contains four combinational modules. The output, lteflg, of the <= module will be 1 if

square (the output of sqReg) is less than or equal to a (the output of aReg).

The Verilog program in Listing 2.5 implements the complete datapath shown in

Fig. 2.9. The four registers have different bus widths and are initialized to different

values. The generic register described in the Verilog file regr2.v shown in Listing 2.6 is

used to instantiate all four registers in Listing 2.5. The two parameters BIT0 and BIT1 are

used to set the lower two bits of the generic register on reset. Note in Listing 2.5 that the

value of sqReg is initialized to 1 and the value of delReg is initialized to 3. In Listing 2.5

the combinational modules adder8, plus2, and minus1 are implemented with assign

statements, and the module lte

is implemented by a separate always block.

The output signal lteflg in Fig. 2.9 is sent to the control unit. The control unit will

then provide the datapath with the load signals for all of the registers. The design of the

control unit will be described next.

Figure 2.9 Datapath for square root algorithm

- 1

- 2

前往页