基于VHDL的数字时钟设计.doc

2.虚拟产品一经售出概不退款(资源遇到问题,请及时私信上传者)

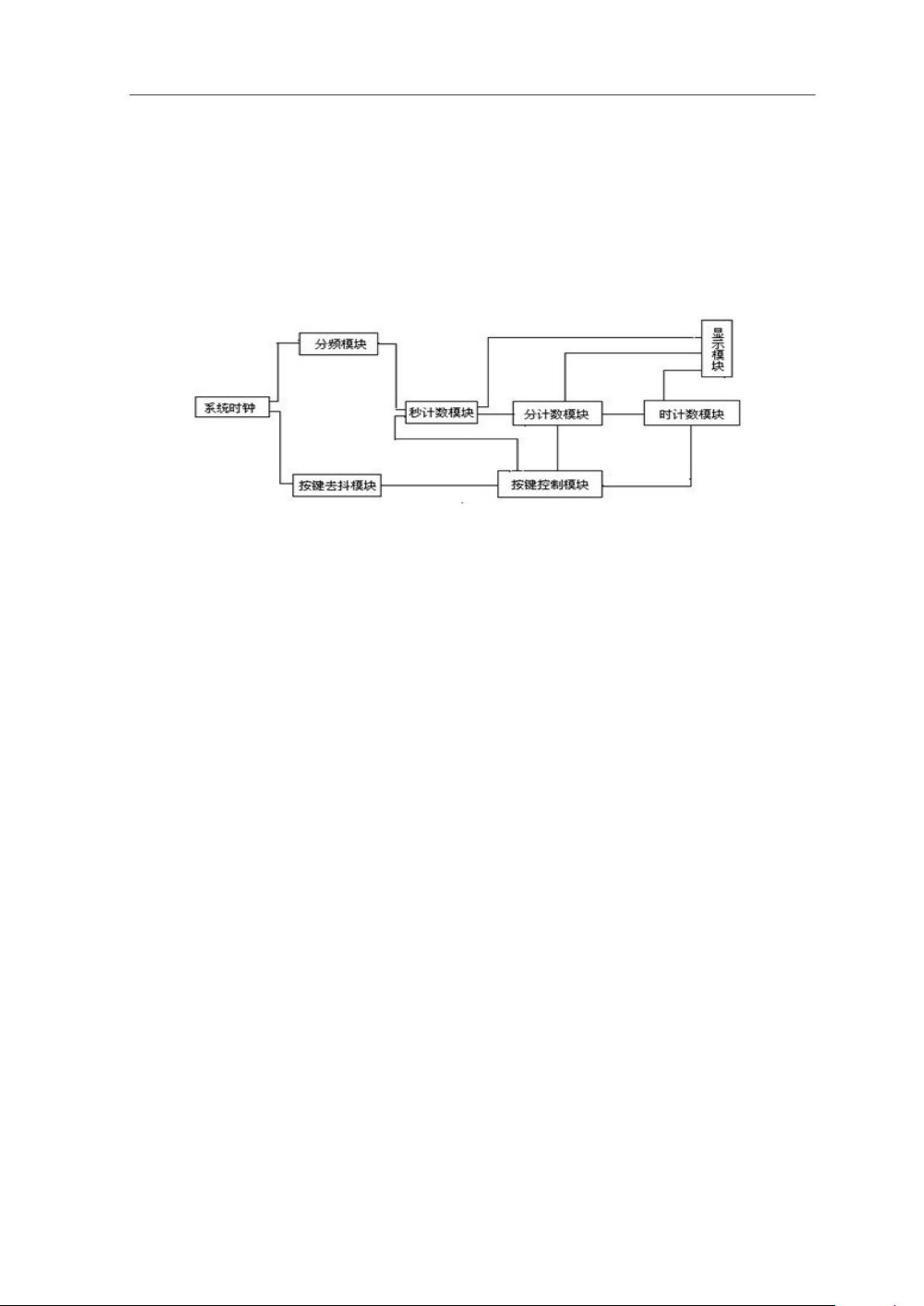

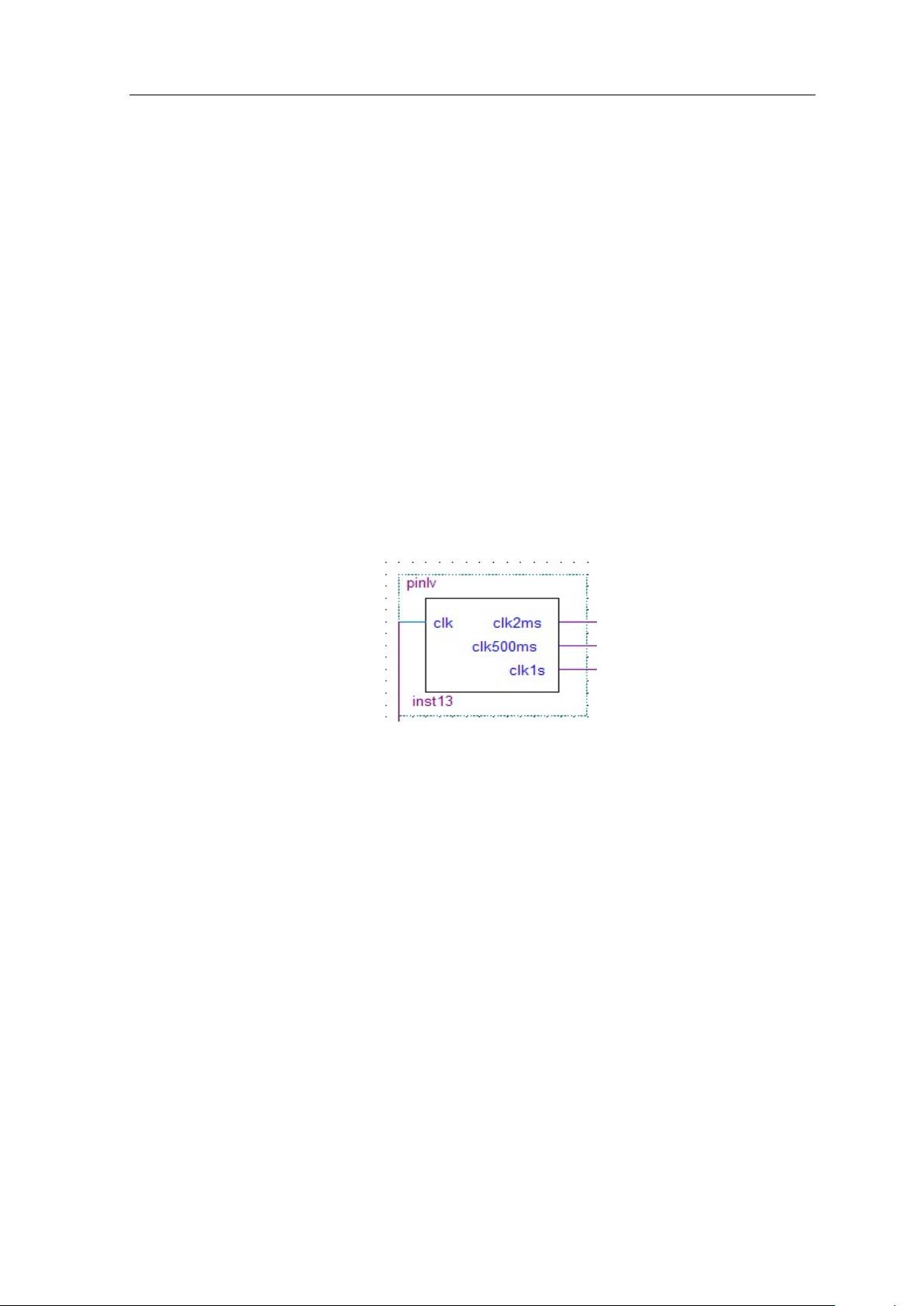

在数字电子技术领域,基于VHDL的数字时钟设计是一项常见的实践项目,它利用硬件描述语言VHDL来实现数字时钟的功能。VHDL是一种用于电子设计自动化(EDA)的标准化编程语言,它允许工程师用软件的方式描述和设计数字系统,包括逻辑门、触发器、计数器等基本电路元素。 1.1 数字时钟的工作原理 数字时钟的核心是计数器,它的工作基于计数和进位的概念。通常,数字时钟由三个主要部分构成:秒计数器、分计数器和小时计数器。秒计数器接收1Hz的时钟信号,这个信号通常由高频率的晶体振荡器分频得到。每当这个1Hz的时钟脉冲到来,秒计数器就会加1。当秒计数器达到59后,它会产生一个进位信号,这个信号会传递给分计数器,使得分计数器加1。同样的过程发生在分计数器达到59后,进位信号将使小时计数器加1。小时计数器通常设计为24进制,当达到23时,再次进位会导致所有计数器复位,重新开始计时。 1.2 设计任务 设计基于VHDL的数字时钟,需要完成以下关键模块的设计: - 分频模块:将高频率的时钟信号(如50MHz)转换为1Hz的秒计数时钟。 - 按键去抖动模块:处理用户输入的按键信号,消除因机械接触产生的抖动,确保稳定可靠的计时控制。 - 按键控制模块:根据用户按键操作,实现时间的设定和停止等功能。 - 六十进制计数模块:设计能够处理60进制计数的电路,用于秒、分的计数。 - 时计数模块:24进制计数器,用于小时的计数。 - 组合逻辑模块:将秒、分、时的计数值组合,形成完整的时钟显示。 - 数码管显示模块:将计算出的时间以7段数码管的形式显示出来。 2. 系统总体方案设计 整体设计中,首先需要确定系统架构,包括各个模块的接口定义和功能划分。然后,使用VHDL编写各个模块的代码,实现相应的逻辑功能。每个模块应独立且可复用,方便后期的验证和修改。 3. VHDL模块电路设计 - 分频模块(pinlv):采用递减计数器或模运算实现,将高频时钟分频至1Hz。 - 按键去抖动模块(qudou):使用延时线或寄存器实现,滤除连续的按键脉冲,确保稳定的计数信号。 - 按键控制模块(self1):处理按键输入,实现时钟的启动、停止、设置等功能。 - 六十进制计数模块(cantsixty):使用计数器和译码器,实现秒和分的六十进制转换。 - 时计数模块(hourtwenty):设计24进制计数器,处理小时的计数。 - 组合逻辑模块:将上述计数器的输出进行组合,生成完整的时间信号。 - 数码管显示模块:根据时间数据驱动7段数码管,显示当前时间。 3.2 数字时钟的顶层设计原理图 顶层设计是整个系统的总览,它将各个子模块连接在一起,形成一个完整的数字时钟系统。原理图中应清晰地表示出各模块间的信号流向和相互作用。 3.3 系统仿真与调试 在设计完成后,使用EDA工具进行仿真,验证各个模块和整个系统的行为是否符合预期。通过仿真可以发现潜在的错误和问题,然后进行调试和优化。 结束语 基于VHDL的数字时钟设计不仅锻炼了设计者的逻辑思维能力,也加深了对数字系统和VHDL语言的理解。通过实际操作,可以提高硬件设计的技能,并为后续的FPGA或ASIC设计打下坚实的基础。 参考文献 这里列出相关的技术资料、教程、标准文档等,作为设计和学习的参考。 致谢 感谢指导教师、同学以及相关资源的支持,使得设计工作得以顺利完成。 附录 源程序代码 附录中包含所有VHDL源代码,包括分频模块、按键处理模块、计数器模块以及显示模块等,这些代码是实现数字时钟功能的关键。 基于VHDL的数字时钟设计涵盖了数字逻辑设计的多个方面,包括计数、分频、译码、组合逻辑和时序逻辑等,是理解和应用数字系统设计的重要实践。通过这样的设计,学生能深入理解数字电路的工作原理,并掌握硬件描述语言的应用技巧。

剩余25页未读,继续阅读

- 粉丝: 97

- 资源: 2万+

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 质量安全排查报告.docx

- 职业中专技工学校专业评估表.docx

- 质量控制资料核查表:建筑保温工程.docx

- 质量目标统计数据表.docx

- 质量内审方案.docx

- 中国古今地名对照表.docx

- 智力残疾评定标准一览表.docx

- 中央造林补助实施方案小班一览表.docx

- 肘关节功能丧失程度评定表.docx

- 重要神经及血管损伤评定.docx

- 自建房安全整治和农村住房建设考评内容和评分标准.docx

- 走访服务企业登记表.doc

- 智能车开发技术的多领域深度解析及应用

- 西红柿叶片图像目标检测数据【已标注,约700张数据,YOLO 标注格式】

- 蓝桥杯开发技术的全面解析与备赛建议

- 相当于去中心化的QQ版本了

信息提交成功

信息提交成功