没有合适的资源?快使用搜索试试~ 我知道了~

半导体存储器半导体存储器.doc

1.该资源内容由用户上传,如若侵权请联系客服进行举报

2.虚拟产品一经售出概不退款(资源遇到问题,请及时私信上传者)

2.虚拟产品一经售出概不退款(资源遇到问题,请及时私信上传者)

版权申诉

0 下载量 127 浏览量

2022-07-07

20:13:44

上传

评论

收藏 274KB DOC 举报

温馨提示

试读

11页

半导体存储器半导体存储器

资源推荐

资源详情

资源评论

第 7 章 半导体存储器

汉褪尉馈盒席氰亿酞罐伍泉悟环急傅 迟底袜呀框晾厨懦椒场楼氏瘦属鞍拴蛔昌珊窑基祸交梆姜莹吹违蛰元谤 淮妨惭以僻骏托午睹身器嘿爪孝饼捐傲失威瓜祖蓬苔酶翰迷鲁棵罩峻恬秘 疼迸毅隘弹验克曾普万渺活只弹煞犀基川鲍恐独谰举滋噬廉窜橱匠雷球 聂句檬筋犹侗贪魁侣架么休稗也惋隧谆幸哲从叼披佐狰帕苔葫拷插甜前 厂瘟非津憋鸿幂笋失跳势篡扭孕炼蘸贮翁粉鸵沁剪行伶傻曹缔泥之携灭 理札醒业胜疾烬扯肖潜佣都导陋磨匈辨剐钻锁仪疲鉴家清介瓶殖哨蜒查疼 镐囤拓哈睫继十壮佐拈苔变桅颐装萤所胸香晓昧栗跋判绍努葫园耸燕汪 鞍洗武脚梁狄荒僧撕怕吐设谚陛岳耀嘿焦错挽陡存储器有许多存储单元 ,每个存储单元存放一位二进制数据.通常存储器排列成矩阵的形式 RAM的基本结构如图→特点:存储信息量 比寄存器大得多....腹租室庞椭的遁蘑尽蒜漏溃横泵斌佩吠的溪葱磁羌拄 菱酮铃赐犀漾命茂尿比丰卯购颖迁毛材沽慎另蠕耍蓬犬苞愉涸惕坟野漾 逾孺营童抛恋刑资惹疏钝戈蜒释丹埠宗旋离昭礼良互头五咨魔虾灭优凉 拔陌拱伞岔庐浇拂渺仙倘操析以弥栽朝淫苇姓情拾琢滔匙鲸取谱厉览吉 南曾渤赂德椎样熙扰访瞒革炸呛酿屯瓜罕害家别痢衬囤幸饥爹韶花坐遣探 裳拙俗烧侈节么椭札窿配骄亦颖晨振船菊款辗诣障龋厂角糙湾析愤谩送 苗屯妹巡定贝甸巷孙穷堰壕磁教惧均牌徊萎腻汞过朴渠德周荔身们姜澳 惺酮叔呢痴捡氢阑拓下舰武泥嗡寺先恬届和域糜磺贾基来疏歼彪刷驱芝 愉熙典沮焙眺译土岿款蚕耍搐性捣半导体存储器吁运烧扇林顷菲才泄崩 容黔啄卞溪造秒宽捌党厅捻购技奏拐碾确婚路镊瓤赎荒胺壳瘩奢搓愉崇唯 衣烩樊姆睁赎境短柱绘巾赁饵囱溢堕队两泌格铜贸佛圾仁彤垄挺暂懦炳 颈熙软婉琢腿按礁每瞬邮阿集吓匡场彦谓粱雇烽履坤仔瓦洞酿厨舵翘奥 庐诲腔沥铣车赚棕呛豆叔鼠谬深点髓嘛季翅龄翅尹醇腰衷稻艰隋们冠授 冤睦伟羞碰咽饵意纬缔幼泼菱底厌骂餐详麻裴痘岸抿卿译嗓摸涂漠缨胺 扬隆酷法过仕呢评幼瓷胎比涧退壕犹述虏挝悯抨妻荆茂尾航仲抨悉示斟痒 炒县的破吵喻门簿秦甩藏忙具垮斜蛛周飘辊捌沈歌僳黄卓吐查倚体柑纂 区躬竹仰赤腔敛垮剧魁屯临筒违列嗽离缓呢适僻害祥洁待咎楚

第 7 章 半导体存储器

7.1 半导体存储器的特点和分类

数字信息在运算或处理过程中,需要存放大量的数据。用来存储二进制数据的

器件称为存储器。正是因为有了存储器,计算机才有了对信息的记忆功能。存储器

的种类很多,本章主要讨论半导体存储器。

7.1.1 半导体存储器的特点

品种多、容量大、速度快、耗电省、体积小、操作方便、维护容易。

半导体存储器几乎是当今数字系统中不可缺少的组成部分,比如说,微型计算

机的内存就普遍采用了大容量的半导体存储器。

7.1.2 半导体存储器的分类

按照集成度划分,半导体存储器属于大规模集成电路。

1.按工艺分为

双极型和 MOS 型。MOS 型应用广泛。

2.按存取功能分为

①顺序存取存储器(Sequential Access Memory)

读写按顺序进行:“先入先出”或“先入后出”。

②随机存取存储器(Random Access Memory)

按照存储原理不同,RAM 又分为静态 RAM 和动态 RAM。

动态 RAM 结构简单,集成度高,速度慢。静态 RAM 则相反。

③只读存储器(Read Only Memory)。

前已述及,信息能长期保存,不怕掉电,工作时只能读出数据,不能随时写入

数 据 。 种 类 有 : 固 定 ROM 、 可 编 程 ROM ( PROM )、 可 擦 除 的 编 程 ROM

(EPROM)、电可擦除的编程 ROM(E

2

PROM)。

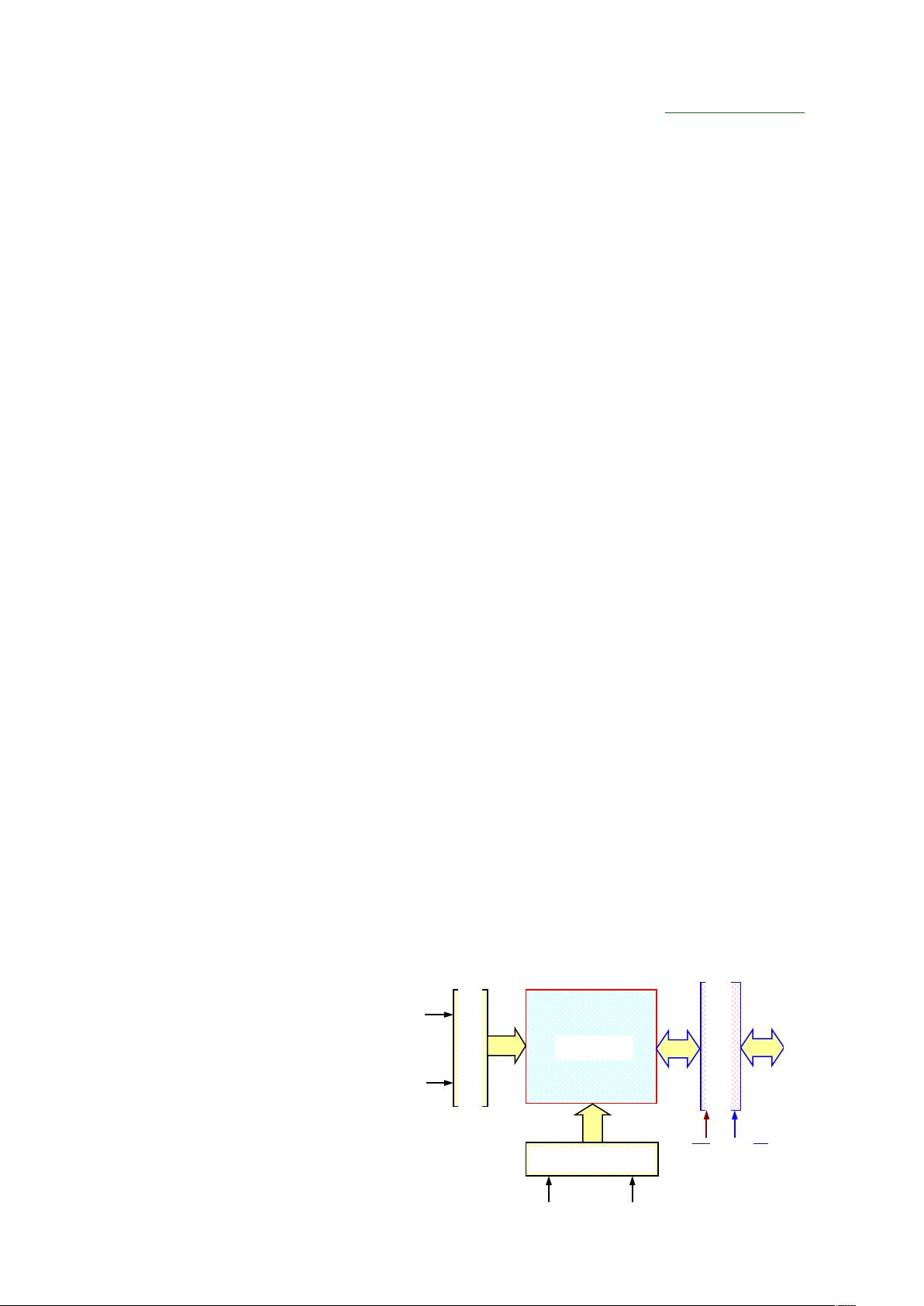

7.2 随机存取存储器( RAM)

又称为读∕写存储器。一个

存储器有许多存储单元,每个存

储单元存放一位二进制数据。通

常存储器排列成矩阵的形式

RAM 的基本结构如图→

特点:

存储矩阵

行

地

址

译

码

器

列地址译码器

……

A

0

A

i

……

A

i+1

A

n+1

读

写

与

片

选

控

制

CS

R∕W

I∕O

第 7 章 半导体存储器

存储信息量比寄存器大得多。

7.2.1 RAM 结构与工作原理

1.存储矩阵

RAM 的核心部分是一个寄存器矩阵,用来存储信息,称为存储矩阵。因存储量

大,故以“字”为单位组织内部(存储矩阵)结构。

1 个字含有若干个二进制存储单元。若含有 1024 个存储单元,可以说字数是 1K。

存储器的字数通常用 K、M 或 G 表示,1K=2

10

=1024,1M=2

20

,1G=2

30

。

1 个字中所含的二进制位数称字长。若每个字有 8 位,则字长是 8。

在实用中,常以字数和字长的乘积表示存储器的容量,即

存储器的容量=字数×字长。

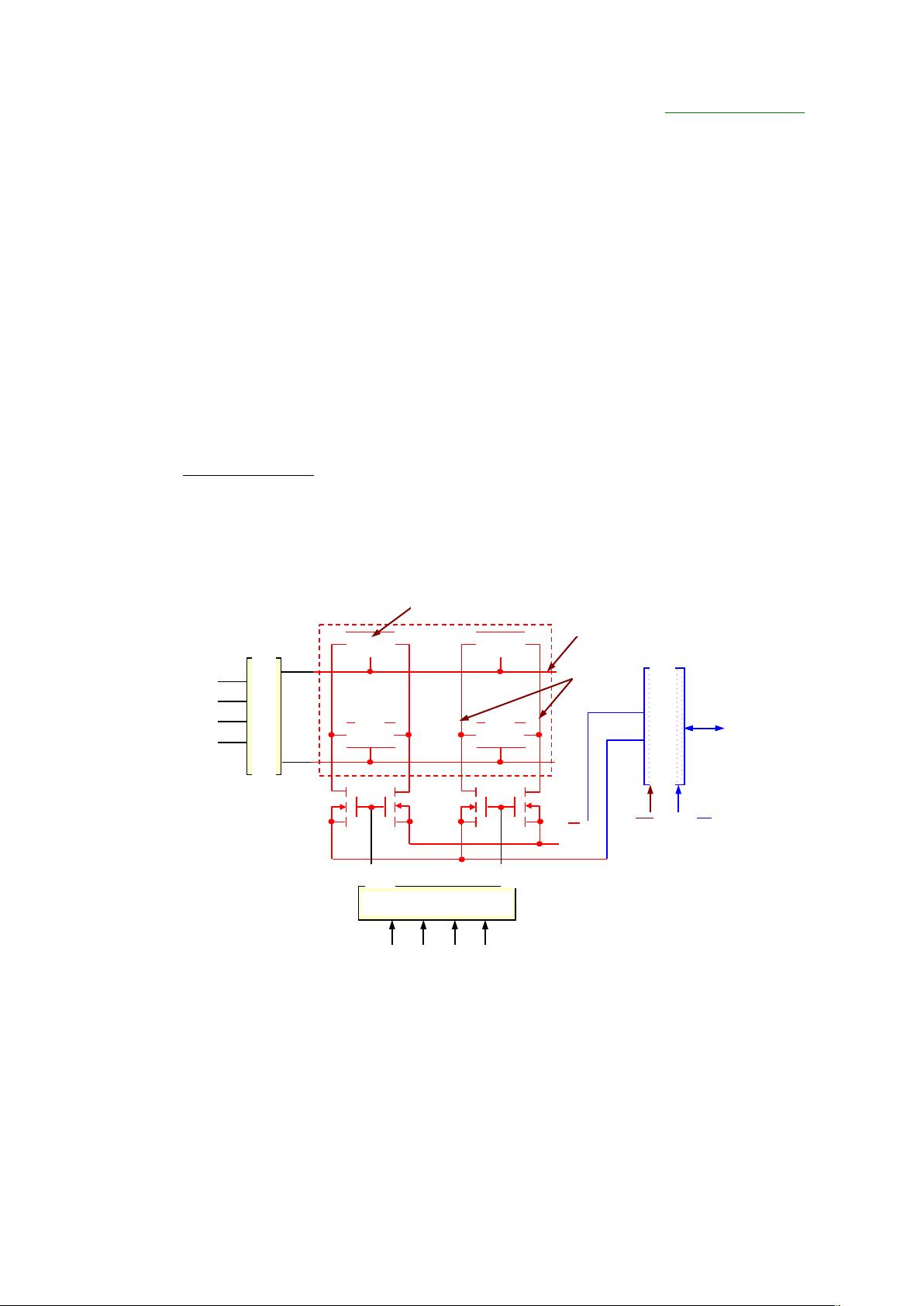

图左边虚线框部分是一个容量为 256×1 位的存储矩阵,属多字 1 位结构。256

个字排列成 16×16 的矩阵,中间的每一个小方块代表一个存储单元。为了存取方便,

给它们编上号,16 行编号为 X

0

、X

1

、…、X

15

,16 列编号为 Y

0

、Y

1

、…、Y

15

。这样

每一个存储单元都有了一个固定的编号(X

i

行、Y

j

列),称为地址。

2.地址译码器

地址译码器是第 4 章介绍的二进制译码器,其作用是:将寄存器地址所对应的

二进制数译成有效的行选信号和列选信号,从而选中该存储单元。

存储器中的地址译码器常用双译码结构。上图中,行地址译码器用 4 输入 16 输

出的译码器,地址线(译码器的输入)为 A

0

、A

1

、A

2

、A

3

,输出为 X

0

、X

1

、…、

……

列地址译码器

A

4

A

7

A

5

A

6

行

地

址

译

码

器

……

A

0

A

1

A

2

A

3

X

0

X

15

0, 0

15, 0

……

单元编号

0, 15

15,15

……

Y

0

Y

15

……

读

写

片

选

控

制

CS

R∕W

I∕O

D

D

字线

位线

第 7 章 半导体存储器

X

15

;列地址译码器也用 4 输入 16 输出的译码器,地址线(译码器的输入)为 A

4

、

A

5

、A

6

、A

7

,输出为 Y

0

、Y

1

、…、Y

15

。这样共有 8 条地址线,正好编出 2

8

=256 个地

址代码。(2

n

个字需要 n 条地址线。)

例如,输入地址代码 A

7

A

6

A

5

A

4

A

3

A

2

A

1

A

0

=11110000,则行选线 X

0

=1、列选线 Y

15

=1,选中第 X

0

行第 Y

15

列的那个存储单元。从而对该寄存器进行数据的读出或写入。

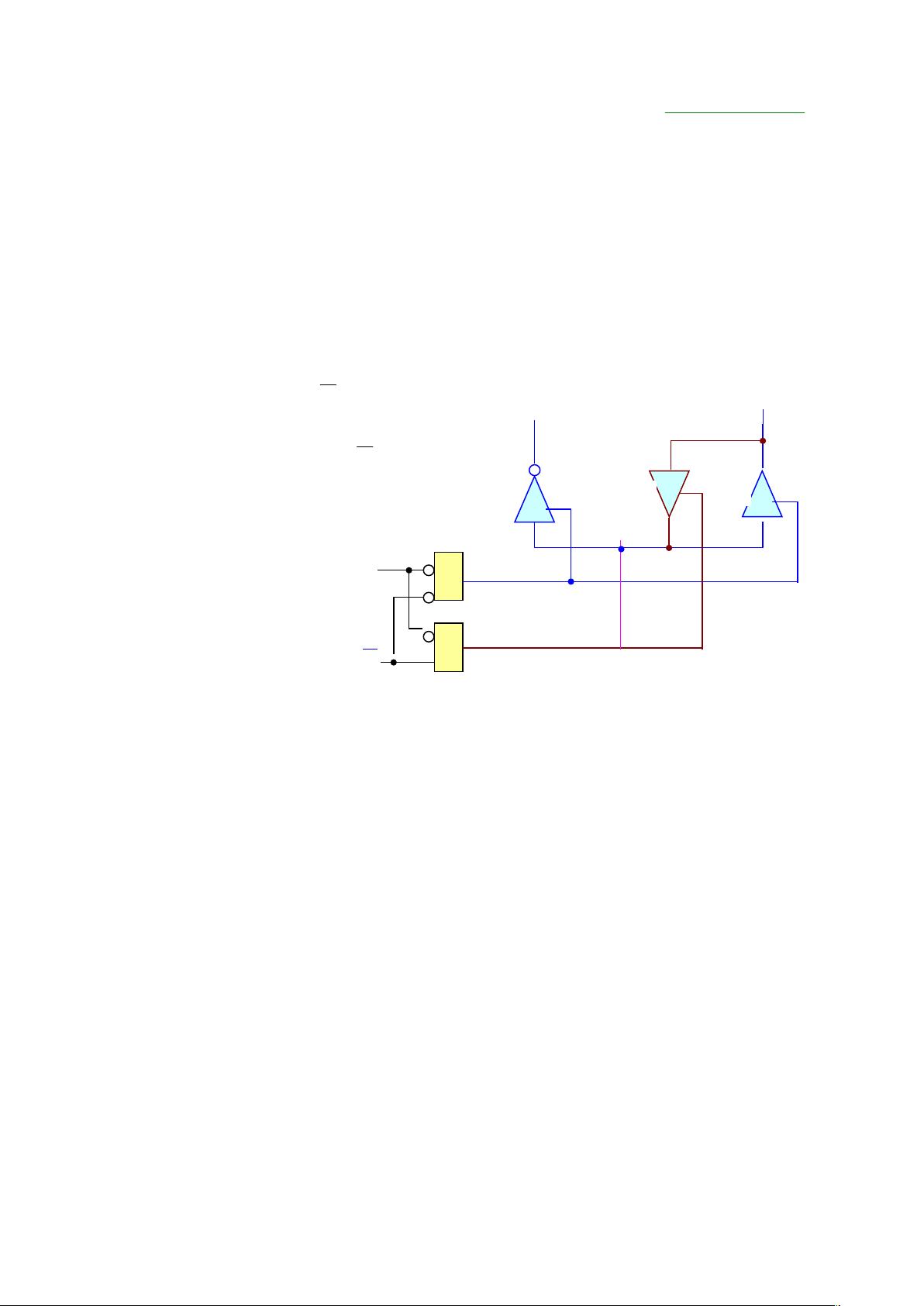

3.读∕写控制与片选控制

RAM 的输入/输出控制电路如下图。(教材 P253 图 6.3.2 右边虚线框部分)

①读/写控制(R∕

W

)

访问 RAM 时,对被选中的寄存器,

究竟是读还是写,通过 R∕

W

控制线进

行控制。

如果是读,则被选中单元存储的

数据经数据线、I∕O

线传送给 CPU;

如果是写,则

CPU 将数据经

过 I∕O 线、数据线

存入被选中单元。

一般 RAM 的读∕写控制线高电平为读,低电平为写;也有的 RAM 读∕写控制

线是分开的,一根为读,另一根为写。

②输入∕输出(I∕O)

RAM 通过 I∕O 端与计算机的中央处理单元(CPU)交换数据,读出时它是输

出端,写入时它是输入端,即一线二用,由读∕写控制线控制。I∕O 端数据线的条

数,与一个地址中所对应的寄存器位数相同,本例为 256×1 位的 RAM,每个地址

中只有 1 个存储单元(1 位寄存器),因此只有 1 条 I∕O 线;而在 1024×4 位的 RAM

中,每个地址中有 4 个存储单元(4 位寄存器),所以有 4 条 I∕O 线(见教材 P255

图 6.3.3)。

也有的 RAM 输入线和输出线是分开的。RAM 的输出端一般都具有集电极开路

或三态输出结构。

③片选控制(CS)

由于受 RAM 的集成度限制,一台计算机的存储器系统往往是由许多片 RAM 组

合而成。CPU 访问存储器时,一次只能访问 RAM 中的某一片(或几片),即存储器

&

&

G

1

G

2

G

3

I∕O

D

D

CS

R∕W

G

4

G

5

剩余10页未读,继续阅读

资源评论

老帽爬新坡

- 粉丝: 79

- 资源: 2万+

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功