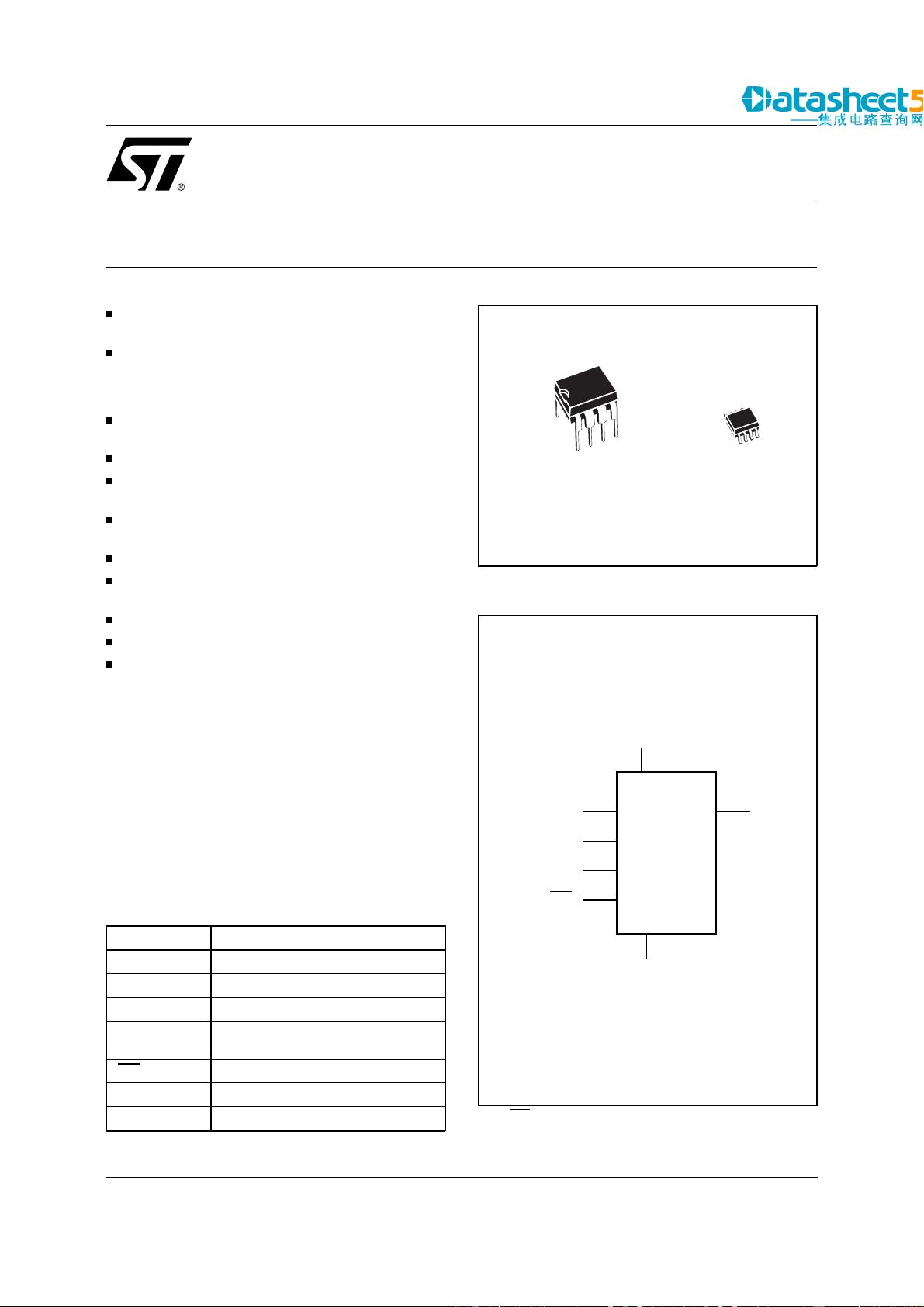

### 24C08 EEPROM 数据手册解析 #### 概述 本文档是对ST24C08 EEPROM数据手册的详细解析。该手册为英文版,涵盖了ST24C08与ST25C08这两款EEPROM(电可擦除可编程只读存储器)产品的技术细节。此外,手册还提供了关于ST24W08和ST25W08这两个硬件写保护版本的相关信息。这些芯片均具有8Kbit的容量,并支持用户自定义块写保护功能。 #### 主要特性 - **高耐用性**: 支持100万次擦写周期,确保数据保留长达40年。 - **单电源电压范围**: - 对于ST24x08系列,电压范围为3V至5.5V; - 对于ST25x08系列,电压范围为2.5V至5.5V。 - **硬件写控制版本**: 提供了ST24W08和ST25W08版本,具备硬件写保护机制。 - **兼容I²C总线**: 使用两线串行接口,完全兼容I²C总线标准。 - **写操作模式**: 支持字节写、多字节写(最多8字节)、页写(最多16字节)等操作。 - **读取模式**: 包括字节读、随机读和顺序读等多种模式。 - **自动地址递增**: 在进行连续写或读操作时,可以自动递增地址。 - **增强的ESD/闩锁性能**: 提高了静电放电和闩锁效应的抵抗能力。 #### 封装与引脚 - **封装形式**: 提供塑料双列直插式封装(PSDIP8)和小型封装(SO8)两种选项。 - **引脚定义**: - `E` (Chip Enable Input): 芯片使能输入,用于选择特定的EEPROM芯片。 - `SDA` (Serial Data Address Input/Output): 串行数据地址输入/输出引脚。 - `SCL` (Serial Clock): 串行时钟信号引脚。 - `MODE/WC*`: 多字节/页写模式(ST24x08)或写控制(ST25W08)。 - `VCC`: 电源电压输入。 - `VSS`: 接地端。 - `PRE`: 写保护启用(仅在硬件写控制版本中可用)。 #### 功能描述 ST24/25x08系列EEPROM产品由STMicroelectronics制造,采用了先进的CMOS技术。每款芯片均具有4个256x8位的数据块组织结构,共8K位的容量。这些EEPROM芯片具备以下特点: - **存储单元组织**: 组织为4个256x8位的数据块。 - **兼容I²C总线标准**: 采用双向数据总线和串行时钟,符合I²C标准。 - **设备识别码**: 内置一个4位的唯一设备识别码(1010),符合I²C总线定义。 - **芯片选择**: 通过一个芯片使能输入(E)进行芯片选择,允许最多两个8K位的设备连接到同一I²C总线上并单独选通。 - **从属设备行为**: 在I²C协议中作为从属设备,所有内存操作都由串行时钟同步。 - **启动条件**: 读写操作由总线主控器产生的启动条件初始化。 #### 总结 ST24C08和ST25C08是高性能的EEPROM解决方案,适用于需要高可靠性和长时间数据保存的应用场景。其强大的耐用性、灵活的读写操作以及与I²C总线的兼容性使得它们成为许多电子设计中的首选。无论是用于消费电子产品还是工业应用,这些芯片都能够提供稳定的数据存储功能,满足不同领域的应用需求。

剩余15页未读,继续阅读

「已注销」2013-09-20学习学习还是不错的。

「已注销」2013-09-20学习学习还是不错的。

- 粉丝: 3

- 资源: 49

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 01-【管理制度】-55-公司员工培训手册管理人力资源管理制度.docx

- 01-【管理制度】-59-人力资源管理制度汇编.doc

- 01-【管理制度】-60-人力资源管理制度汇编.doc

- 02-【管理流程】-01-人力资源管理流程图.docx

- 02-【管理流程】-04-招聘录用流程图.docx

- 02-【管理流程】-02-人力资源管理流程.doc

- 02-【管理流程】-03-HR工作流程图.docx

- 02-【管理流程】-05-招聘流程图.docx

- 02-【管理流程】-06-员工入职流程图.docx

- 02-【管理流程】-07-员工入职流程图.docx

- 02-【管理流程】-10-员工转正流程图.docx

- 02-【管理流程】-08-入职流程图.docx

- 02-【管理流程】-09-新员工入职培训流程图.docx

- 02-【管理流程】-11-试用期转正流程图.docx

- 02-【管理流程】-13-员工晋升流程图.docx

- 02-【管理流程】-12-晋升管理流程图.docx

信息提交成功

信息提交成功