《EDA技术实用教程(第四版)》

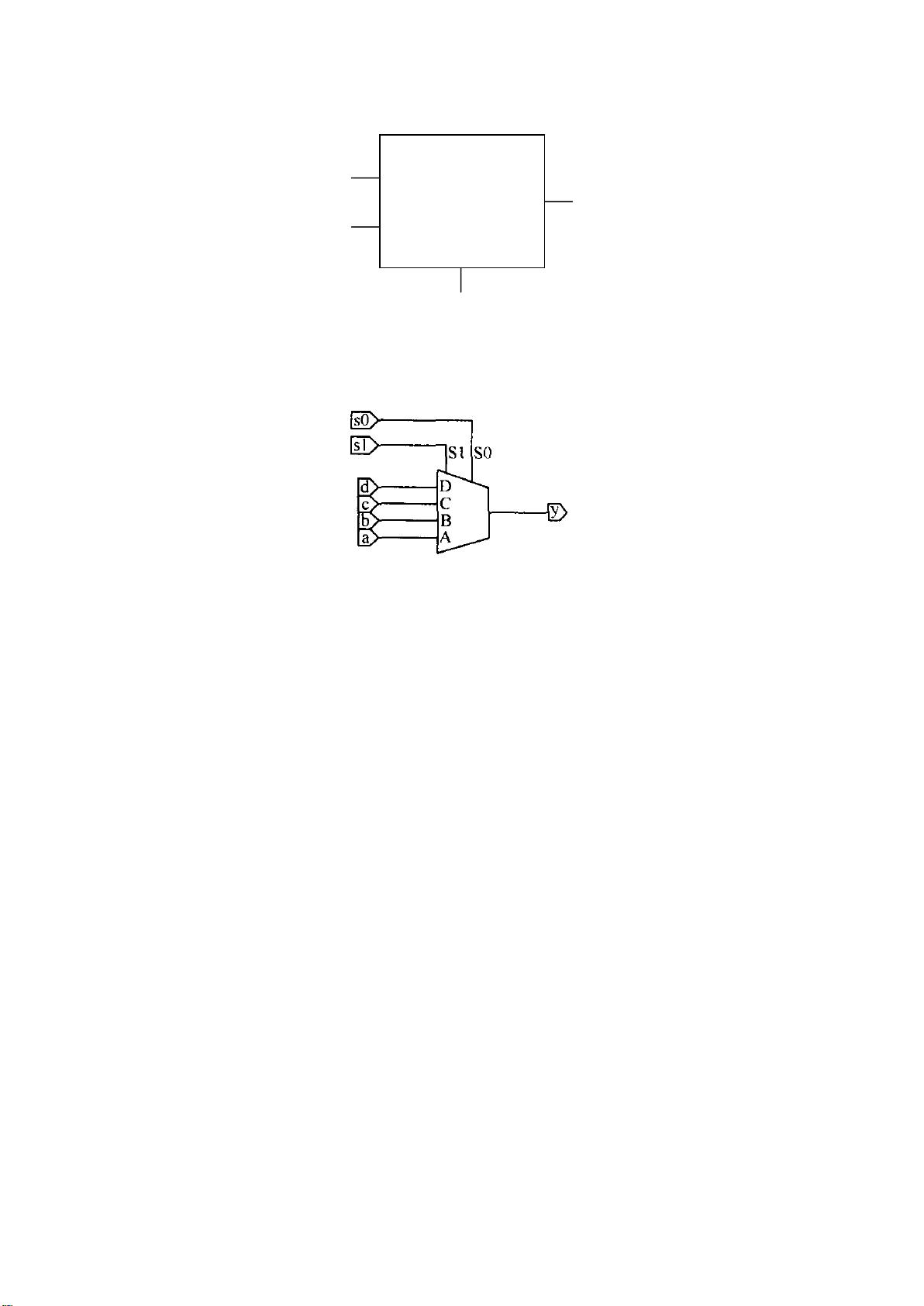

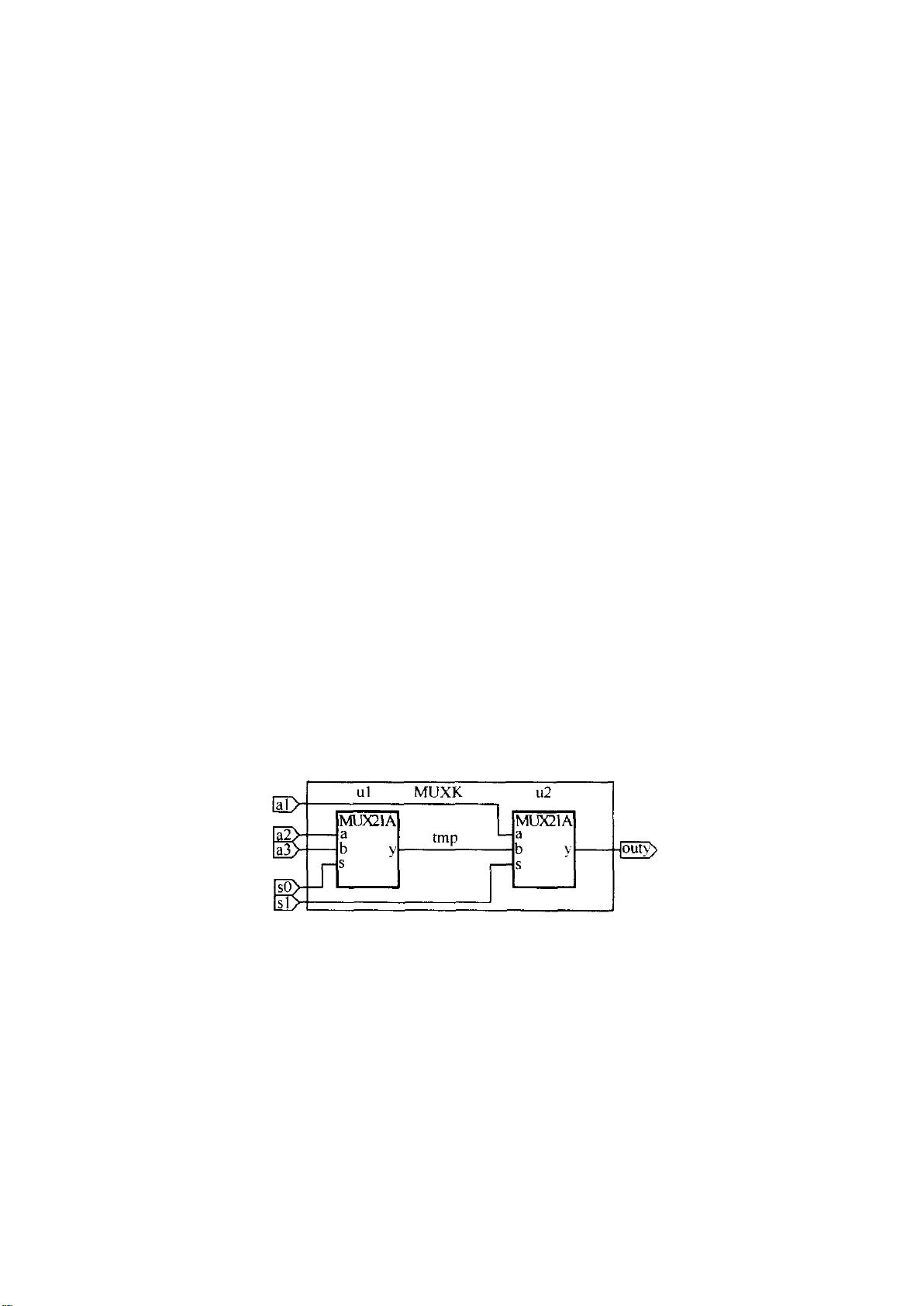

### EDA技术与ASIC设计和FPGA开发的关系 #### 1-1 EDA技术与ASIC设计和FPGA开发的关系 **EDA技术**(Electronic Design Automation,电子设计自动化)是一种广泛应用于集成电路(IC)设计和验证的技术集合。它通过一系列软件工具帮助工程师进行硬件设计、仿真、测试等过程。EDA技术在现代电子工程中发挥着至关重要的作用。 **ASIC**(Application-Specific Integrated Circuit,专用集成电路)是针对特定应用定制的集成电路。ASIC设计往往需要经过多个阶段,包括需求分析、逻辑设计、物理设计、验证和制造等步骤。EDA技术在ASIC设计过程中扮演着核心角色,尤其是在逻辑设计和验证阶段。例如,使用EDA工具可以进行逻辑合成、布局布线、时序分析等工作,从而确保ASIC能够满足性能要求。 **FPGA**(Field-Programmable Gate Array,现场可编程门阵列)是一种高度灵活的集成电路,其内部包含大量的可编程逻辑资源,可以在生产后通过软件重新配置来实现不同的功能。FPGA在ASIC设计中的用途主要体现在以下几个方面: 1. **原型验证**:FPGA可以用来快速实现和验证新的设计想法,减少ASIC设计的风险。 2. **预生产验证**:在ASIC进入大规模生产之前,可以通过FPGA进行系统级的功能验证。 3. **小批量生产替代方案**:对于那些产量较小或者市场需求不确定的应用场景,FPGA可以直接作为最终产品使用,避免了ASIC高昂的初始投资成本。 ### VHDL的特点 #### 1-2 VHDL的特点 **VHDL**(Very High Speed Integrated Circuit Hardware Description Language,超高速集成电路硬件描述语言)是一种用于描述数字逻辑系统的硬件描述语言。与软件描述语言相比,VHDL具有以下特点: 1. **形式化描述**:VHDL能够清晰地描述硬件结构和行为,使得设计意图明确无误。 2. **层次化设计**:支持自顶向下的设计方法,便于大型项目的管理和维护。 3. **可综合性和可模拟性**:VHDL代码既可以用作仿真模型,也可以被综合成实际的硬件电路。 4. **跨平台兼容性**:由于VHDL是一种标准的语言,因此可以在不同的EDA工具和平台上运行。 ### 综合的概念及其在电子设计自动化中的地位 #### 1-3 综合及其在电子设计自动化中的地位 **综合**是指将高级别的抽象设计转换为具体的硬件实现的过程。在这个过程中,设计师使用硬件描述语言(如VHDL或Verilog)来描述电路的行为或结构,然后通过综合工具将其转换为较低级别的表示形式,例如门级网表或可编程逻辑设备(如FPGA)中的配置比特流。 综合在电子设计自动化中的地位十分重要: 1. **简化设计流程**:综合过程使得设计师能够专注于高层的设计,而不需要关心底层细节。 2. **提高设计效率**:通过自动化的综合过程,可以极大地提高设计的效率和质量。 3. **优化资源利用**:综合工具可以根据目标硬件平台的特性进行资源优化,以实现最佳的性能、功耗和面积。 ### 自顶向下的设计方法的重要性 #### 1-4 自顶向下的设计方法的重要性 自顶向下的设计方法是一种从高层次的系统级视图开始,逐步细化到低层次的具体实现的设计方法。这种方法在EDA技术中有以下重要意义: 1. **提高设计效率**:通过先定义系统的需求和总体架构,然后再逐步细化具体模块的设计,可以有效地组织和管理复杂的设计项目。 2. **易于修改和扩展**:在自顶向下的设计方法中,各部分相对独立,这使得后续的修改和扩展变得更加容易。 3. **便于团队协作**:在大型项目中,不同的团队可以负责不同的模块,通过统一的接口规范来进行协作。 ### IP核的意义 #### 1-5 IP核的意义 **IP核**(Intellectual Property Core)是指预先设计好且经过验证的电子设计模块,这些模块可以是逻辑电路、存储器或其他功能单元。在EDA技术的应用和发展中,IP核的意义重大: 1. **加速设计周期**:设计师可以直接复用已有的IP核,避免从头开始设计每个模块,大大缩短了产品的开发时间。 2. **降低风险**:经过验证的IP核可以显著减少设计错误,提高了产品的可靠性。 3. **促进标准化**:IP核通常遵循一定的标准和接口协议,有助于不同组件之间的互操作性。 ### FPGA/CPLD设计流程及EDA工具的作用 #### 1-6 FPGA/CPLD设计流程及EDA工具的作用 FPGA/CPLD设计流程主要包括以下几个阶段: 1. **设计输入**:使用硬件描述语言(如VHDL或Verilog)编写设计。 2. **综合**:将设计转化为可由目标器件实现的形式。 3. **布局与布线**:根据FPGA/CPLD的物理结构对设计进行布局和布线。 4. **验证**:包括静态时序分析、功能仿真等,确保设计符合规格要求。 5. **编程与配置**:将设计加载到FPGA/CPLD上,使其按照预期工作。 在这个过程中,EDA工具发挥了关键作用: - **设计输入工具**:支持VHDL或Verilog等硬件描述语言的编辑器。 - **综合工具**:将高级别的设计转换为具体的硬件实现。 - **布局与布线工具**:优化设计的物理布局,确保满足性能要求。 - **验证工具**:提供仿真环境,进行功能验证和时序分析。 - **编程与配置工具**:用于将设计下载到FPGA/CPLD上。 ### 输出逻辑宏单元(OLMC)的功能 #### 2-1 OLMC的功能 **输出逻辑宏单元**(Output Logic Macro Cell,OLMC)是可编程逻辑器件(如GAL)中的一种基本逻辑单元,主要用于实现可编程的输出逻辑功能。OLMC通常包含一个可编程的组合逻辑部分和一个可编程的触发器部分,用于实现复杂的输出逻辑。 在GAL中,OLMC通过可编程逻辑阵列实现可编程组合电路和时序电路。组合电路部分可以通过编程实现不同的逻辑函数,而时序电路部分则通过触发器实现状态记忆功能。 ### 基于乘积项的可编程逻辑结构 #### 2-2 基于乘积项的可编程逻辑结构 **基于乘积项的可编程逻辑结构**是指逻辑电路中的逻辑函数是由可编程的与门(AND)和或门(OR)组成的。这种结构通常用于可编程逻辑器件(PLDs),特别是早期的PLDs如PAL(Programmable Array Logic)和GAL(Generic Array Logic)。 在基于乘积项的可编程逻辑结构中,用户可以通过编程改变与门和或门之间的连接,从而实现所需的逻辑功能。这种结构非常适合实现复杂的组合逻辑电路。 ### 基于查找表的可编程逻辑结构 #### 2-4 基于查找表的可编程逻辑结构 **基于查找表的可编程逻辑结构**是另一种常见的可编程逻辑结构,尤其在现代FPGA中非常普遍。在这种结构中,逻辑函数是通过查找表(Look-Up Table,LUT)实现的。LUT本质上是一个存储单元,它可以被编程来实现任意的布尔函数。 基于查找表的可编程逻辑结构具有更高的灵活性和性能,因为它可以更容易地适应各种复杂的逻辑功能。此外,LUT还可以通过级联形成更复杂的逻辑结构,以满足更高层次的设计需求。 ### FPGA系列器件中的LAB #### 2-3 FPGA系列器件中的LAB **LAB**(Logic Array Block)是FPGA中的一个重要组成部分,它是FPGA的基本逻辑构建块之一。每个LAB通常包含若干个可编程逻辑单元(如LUTs)和相关的触发器,用于实现复杂的逻辑功能。LAB的设计旨在提供足够的灵活性和高性能,以满足不同的设计需求。 ### 编程与配置的概念 #### 2-5 编程与配置的概念 **编程**与**配置**是两个在可编程逻辑器件中经常使用的术语。 - **编程**通常指的是将设计数据写入非易失性存储器中的过程,这种过程通常是永久性的,一旦编程完成,除非通过特殊手段重写,否则不会改变。 - **配置**则是指将设计数据加载到易失性存储器中的过程,这种过程是非永久性的,每次上电或重启时都需要重新加载。 对于FPGA而言,通常采用配置的方式,因为FPGA中的可编程资源(如LUTs和触发器)都是易失性的,需要在每次上电时重新配置。 ### APEX系列和MAXII系列的分类 #### 2-6 APEX系列和MAXII系列的分类 基于乘积项的可编程逻辑结构通常被归类为**CPLD**(Complex Programmable Logic Device,复杂可编程逻辑器件),而基于查找表的可编程逻辑结构则通常被归类为**FPGA**。 - **APEX系列**:根据题目描述,APEX系列属于基于查找表的可编程逻辑结构,因此可以将其归类为FPGA。 - **MAXII系列**:根据题目描述,MAXII系列属于基于乘积项的可编程逻辑结构,因此可以将其归类为CPLD。 这种分类主要是基于它们内部使用的逻辑结构。APEX系列中的逻辑单元使用查找表实现逻辑功能,而MAXII系列则使用基于乘积项的逻辑结构。 ### VHDL程序设计实例 #### 3-2 图3-16所示的4选1多路选择器的VHDL程序设计 下面展示了两种实现图3-16所示的4选1多路选择器的方法,一种使用IF_THEN语句,另一种使用CASE语句。 1. **使用IF_THEN语句实现** ```vhdl LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; ENTITY mux41 IS PORT (a, b, c, d : IN STD_LOGIC; s0 : IN STD_LOGIC; s1 : IN STD_LOGIC; y : OUT STD_LOGIC); END ENTITY mux41; ARCHITECTURE if_mux41 OF mux41 IS SIGNAL s0s1 : STD_LOGIC_VECTOR(1 DOWNTO 0); BEGIN s0s1 <= s1 & s0; PROCESS (s0s1, a, b, c, d) BEGIN IF s0s1 = "00" THEN y <= a; ELSIF s0s1 = "01" THEN y <= b; ELSIF s0s1 = "10" THEN y <= c; ELSE y <= d; END IF; END PROCESS; END ARCHITECTURE if_mux41; ``` 2. **使用CASE语句实现** ```vhdl LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; ENTITY mux41 IS PORT (a, b, c, d : IN STD_LOGIC; s0 : IN STD_LOGIC; s1 : IN STD_LOGIC; y : OUT STD_LOGIC); END ENTITY mux41; ARCHITECTURE case_mux41 OF mux41 IS SIGNAL s0s1 : STD_LOGIC_VECTOR(1 DOWNTO 0); BEGIN s0s1 <= s1 & s0; PROCESS (s0s1, a, b, c, d) BEGIN CASE s0s1 IS WHEN "00" => y <= a; WHEN "01" => y <= b; WHEN "10" => y <= c; WHEN "11" => y <= d; WHEN OTHERS => NULL; END CASE; END PROCESS; END ARCHITECTURE case_mux41; ``` 这两种方法都可以实现同样的功能,即根据选择信号s1和s0的不同组合选择a、b、c或d中的一个作为输出y。IF_THEN语句适用于条件较少的情况,而CASE语句则更适合处理更多或更复杂的条件。

剩余35页未读,继续阅读

水上老实人2015-01-10不错,答案刚好适合!!

水上老实人2015-01-10不错,答案刚好适合!!

- 粉丝: 0

- 资源: 4

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

信息提交成功

信息提交成功