Introduction Power Semiconductor Applications

Philips Semiconductors

1.2.9 Understanding the Data Sheet: PowerMOS

All manufacturers of power MOSFETs provide a data sheet

for every type produced. The purpose of the data sheet is

primarily to give an indication as to the capabilities of a

particular product. It is also useful for the purpose of

selecting device equivalents between different

manufacturers. In some cases however data on a number

of parameters may be quoted under subtly different

conditions by different manufacturers, particularly on

second order parameters such as switching times. In

addition the information contained within the data sheet

does not always appear relevant for the application. Using

data sheets and selecting device equivalents therefore

requires caution and an understanding of exactly what the

data means and how it can be interpreted. Throughout this

chapter the BUK553-100A is used as an example, this

device is a 100 V logic level MOSFET.

Information contained in the Philips data

sheet

The data sheet is divided into 8 sections as follows:

* Quick reference data

* Limiting values

* Thermal resistances

* Static characteristics

* Dynamic characteristics

* Reverse diode limiting values and characteristics

* Avalanche limiting value

* Graphical data

The information contained within each of these sections is

now described.

Quick reference data

This data is presented for the purpose of quick selection. It

lists what is considered to be the key parameters of the

device such that a designer can decide at a glance whether

the device is likely to be the correct one for the application

or not. Five parameters are listed, the two most important

are the drain-source voltage V

DS

and drain-source on-state

resistance, R

DS(ON)

. V

DS

is the maximum voltage the device

will support between drain and source terminals in the

off-state. R

DS(ON)

is the maximum on-state resistance at the

quoted gate voltage, V

GS

, and a junction temperature of

25 ˚C. (NB R

DS(ON)

is temperature dependent, see static

characteristics). It is these two parameters which provide

a first order indication of the devices capability.

A drain current value (I

D

) and a figure for total power

dissipation are also given in this section. These figures

should be treated with caution since they are quoted for

conditions that are rarely attainable in real applications.

(See limiting values.) For most applications the usable dc

current will be less than the quoted figure in the quick

reference data. Typical power dissipations that can be

tolerated by the majority of designers are less than 20 W

(for discrete devices), depending on the heatsinking

arrangement used. The junction temperature (T

J

) is usually

given as either 150 ˚C or 175 ˚C. It is not recommended

that the internal device temperature be allowed to exceed

this figure.

Limiting values

This table lists the absolute maximum values of six

parameters. The device may be operated right up to these

maximum levels however they must not be exceeded, to

do so may incur damage to the device.

Drain-source voltageand drain-gate voltage havethe same

value. The figure given is the maximum voltage that may

be applied between the respective terminals. Gate-source

voltage, ±V

GS

, gives the maximum value that may be

allowed between the gate and source terminals. To exceed

this voltage, even for the shortest period can cause

permanent damage to the gate oxide. Two values for the

dc drain current, I

D

, are quoted, one at a mounting base

temperature of 25 ˚C and one at a mounting base

temperature of 100 ˚C. Again these currents do not

represent attainable operating levels. These currents are

the values that will cause the junction temperature to reach

its maximum value when the mounting base is held at the

quoted value. The maximum current rating is therefore a

function of the mounting base temperature and the quoted

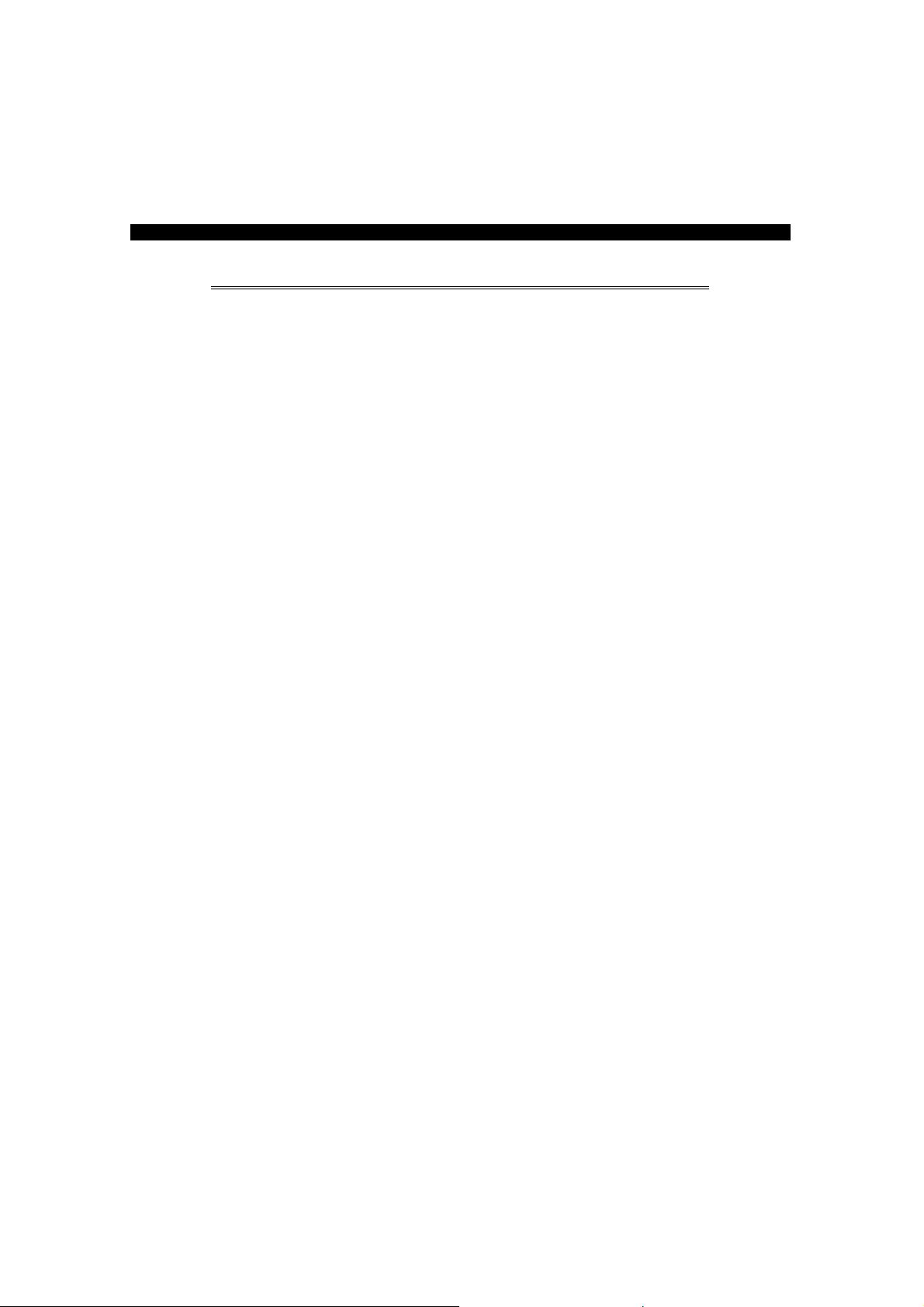

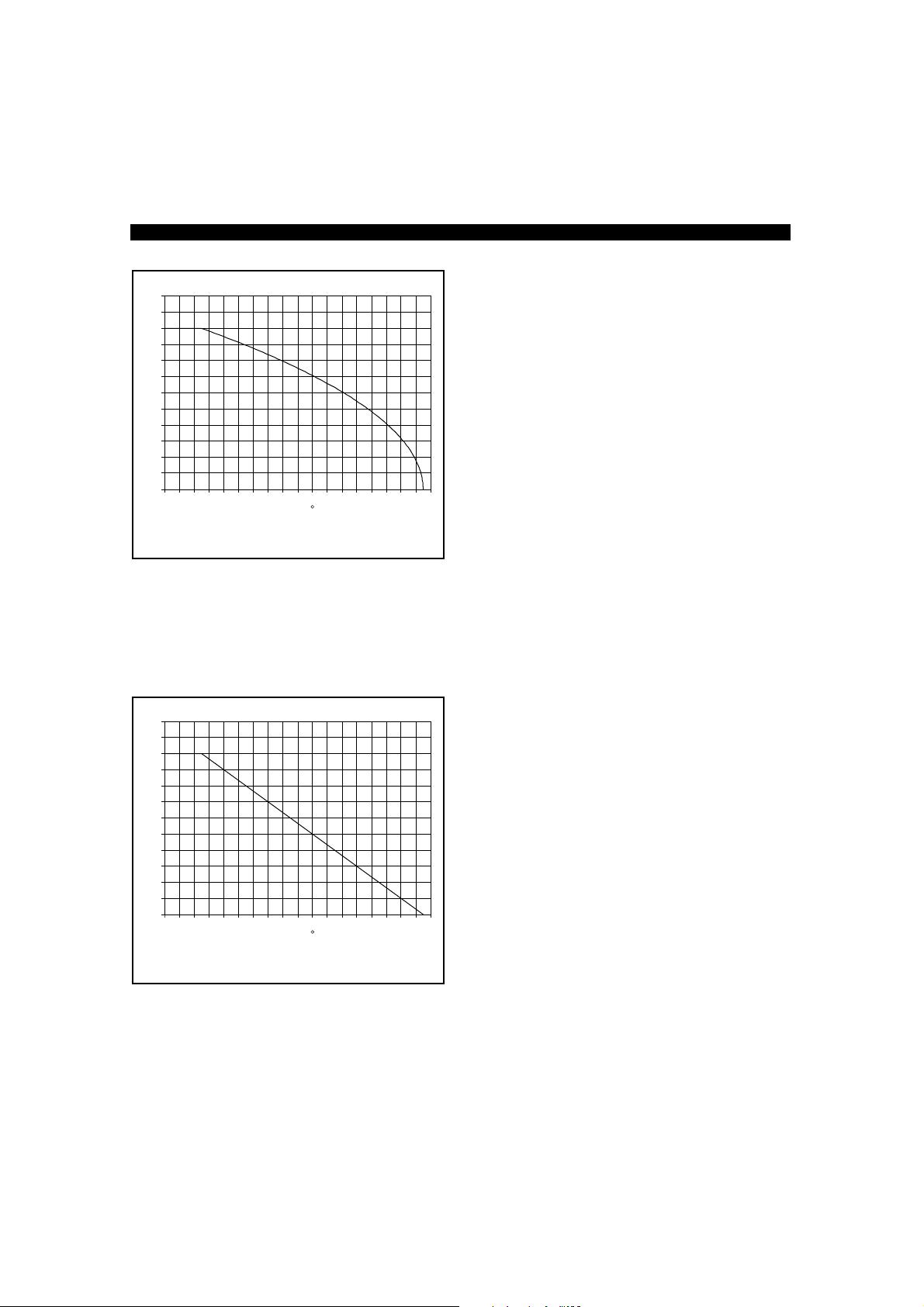

figures are just two points on the derating curve ,see Fig.1.

The third current level quoted is the pulse peak value, I

DM

.

PowerMOS devices generally speaking have a very high

peak current handling capability. It is the internal bond wires

which connect to the chip that provide the final limitation.

The pulse width for which I

DM

can be applied depends upon

the thermal considerations (see section on calculating

currents.) The total power dissipation, P

tot

, and maximum

junction temperature are also stated as for the quick

reference data. The P

tot

figure is calculated from the simple

quotient given in equation 1 (see section on safe operating

area). It is quoted for the condition where the mounting base

temperature is maintained at 25 ˚C. As an example, for the

BUK553-100A the P

tot

figure is 75 W, dissipating this

amount of power while maintaining the mounting base at

25 ˚C would be a challenge! For higher mounting base

temperatures the total power that can be dissipated is less.

69

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜

信息提交成功

信息提交成功