基于ISE14.7的FPGA设计流程

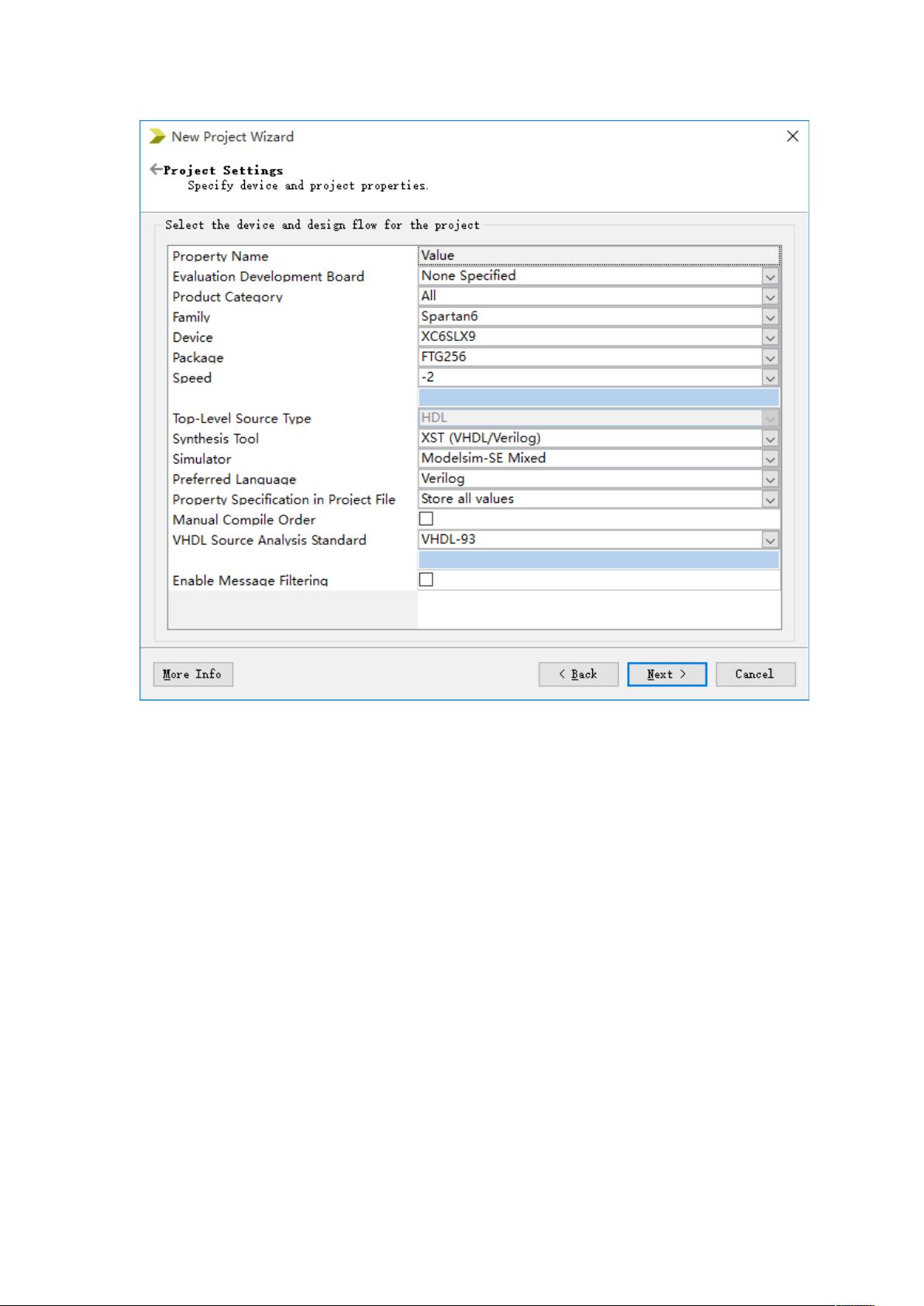

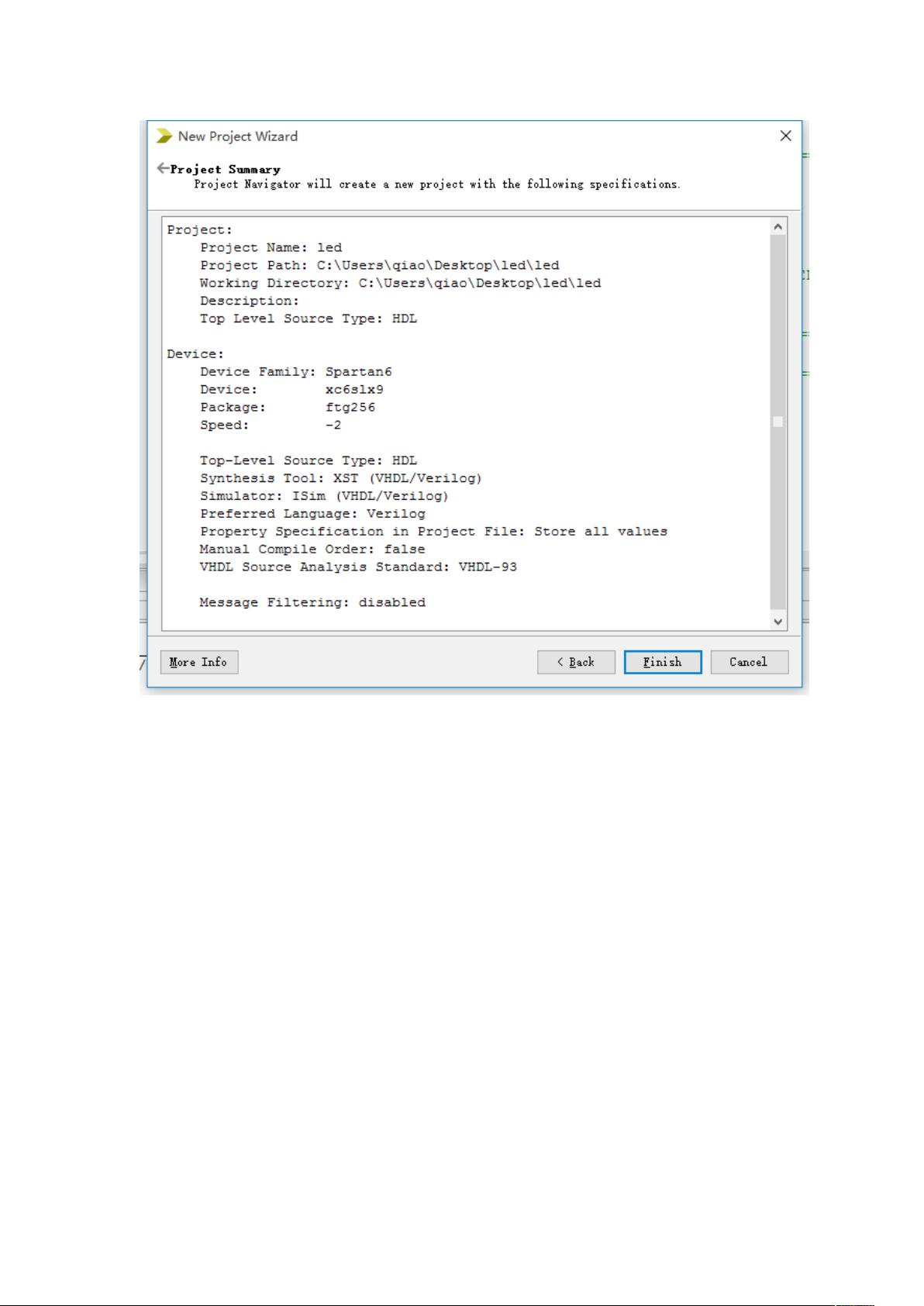

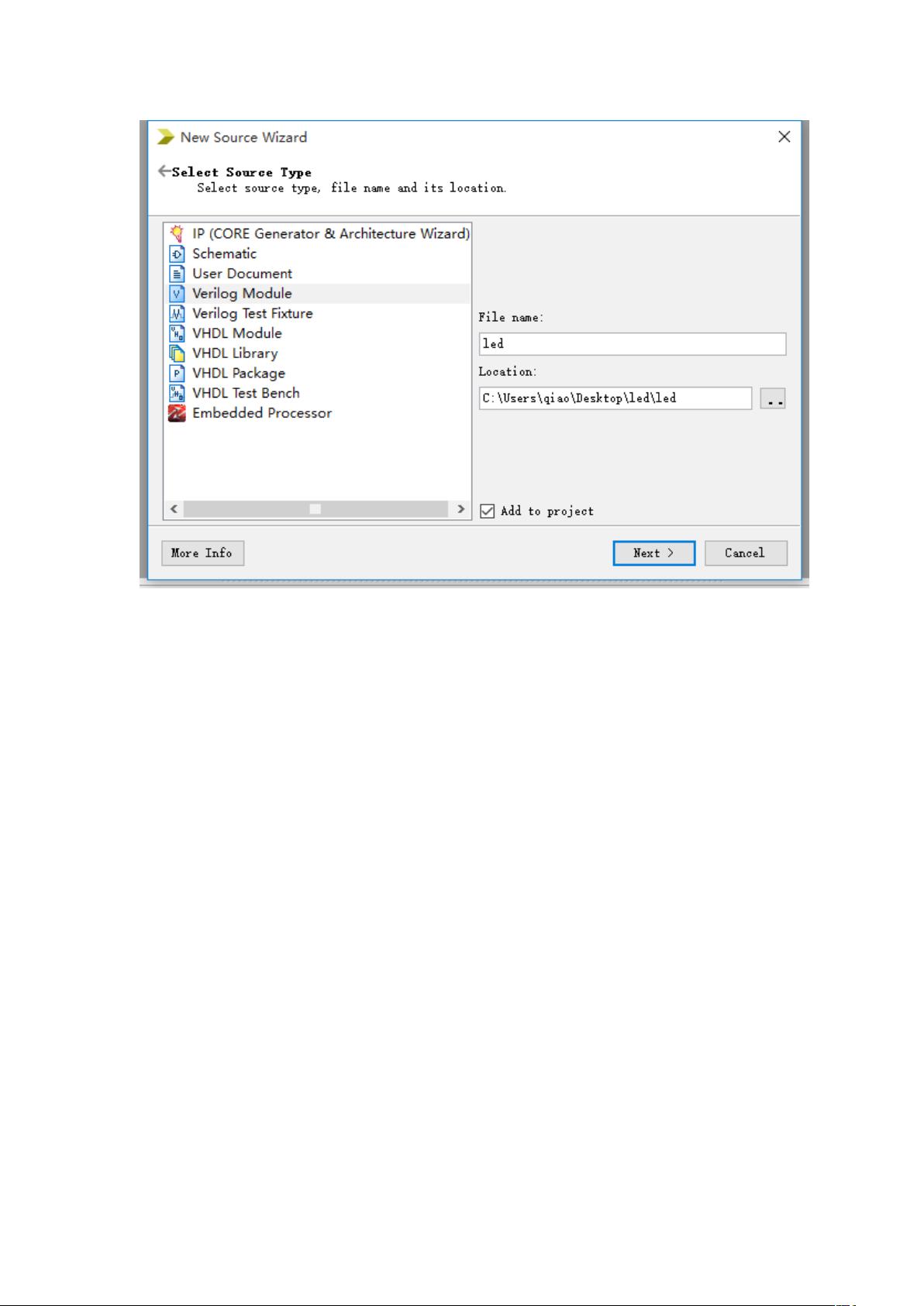

### 基于ISE14.7的FPGA设计流程详解 #### 一、设计源代码 在开始基于ISE 14.7的FPGA设计流程之前,首先需要创建一个新的项目。具体步骤如下: 1. **打开ISE软件**:启动ISE 14.7软件。 2. **创建新项目**:在ISE主窗口中选择`File` > `New Project`命令,打开新建工程智能向导。 3. **输入项目信息**:在向导中输入项目的名称(例如`led_project`)以及项目存放的位置。 4. **选择FPGA器件**:点击`Next`进入器件属性界面,选择所需的FPGA器件型号。例如,可以选择`xc6slx9`系列的FPGA芯片。 5. **总结项目信息**:点击`Next`进入工程总结页面,确认所有信息无误后,直接点击`Finish`完成新工程的创建。 接下来,需要创建源代码文件,通常采用Verilog HDL语言进行设计。 1. **创建Verilog Module**:在主窗口中选择`Project` > `New Source`打开新建源代码向导,选择`Verilog Module`源代码。 2. **定义模块端口**:点击`Next`进入模块端口定义页面,根据设计需求添加端口名及其位宽。例如,可以添加输入端口`clk`(时钟)、`reset`(复位),以及输出端口`leds`(LED控制信号)。 3. **完成模块创建**:点击`Next`进入新建源代码总结页面,然后点击`Finish`完成新建源代码过程。此时可以在`led.v`文件中添加相应的Verilog代码。 #### 二、功能仿真(行为仿真) 完成设计源代码之后,需要对其进行功能验证。这一步通常采用Modelsim SE工具来实现。 1. **配置Modelsim SE**:如果使用的是Modelsim SE而非ISE自带的仿真工具,则需要进行一些额外的设置,以确保Modelsim能够访问ISE的仿真库文件。 2. **设置仿真库路径**:在ISE中,切换到`Simulation`模式,并选择`Behavioral`模式。接着,选中`led.v`文件,右键选择`Simulate Behavioral Model`后点击`Process Properties...`。 3. **编辑设置**:在弹出的“Process Properties”设置窗口中,填写编译库时设置的已编译库的路径,例如`C:\software\ISE14.7\Xilinx_lib`。 4. **编写测试激励文件**:在主窗口中选择`Project` > `New Source`打开新建源代码向导,选择`Verilog Test Fixture`,文件命名为`led_tb`。 5. **关联待仿真的模块**:点击`Next`关联需要仿真的模块`led.v`。 6. **生成测试激励模板**:点击`Next`进入总结界面,最后点击`Finish`生成相应的测试激励模板文件。 7. **添加测试向量**:在`initial...end`模块中的“//Add stimulus here”后面添加测试向量生成代码,例如循环改变输入信号以观察LED的状态变化。 8. **启动仿真**:选中`led_tb.v`文件,然后双击`Simulation Behavioral Model`,随后Modelsim将被调用,启动仿真。 9. **观察仿真结果**:弹出Modelsim后,可以通过`Wave`视图观察LED的状态变化,验证设计的功能正确性。 #### 三、综合并添加时序约束 1. **进行综合**:在功能仿真正确后,选择`Implementation`,选中`led.v`文件,在`Processes`窗口中双击`XST`进行综合。 2. **查看综合报告**:综合完成后,检查综合报告,了解资源使用情况及是否满足时序要求。 3. **添加时序约束**:使用鼠标选中`led.v`,在`Processes`面板中双击`Create Timing Constraints`选项会自动弹出一个对话框,创建一个用户约束文件`led.ucf`,并在其中添加时序约束条件。 #### 四、实现(Implement) 1. **进行实现**:选中`led.v`文件,在`Processes`面板中双击`Implement Design`进行实现。 2. **检查实现结果**:实现完成后,检查实现结果是否符合预期,特别是在资源使用和时序方面。 #### 五、后仿真(时序仿真) 1. **配置后仿真**:在`Simulation`模式下选择`Post-Route`模式,选中`led_tb.v`文件,双击`Simulate Post-Place&Poute Model`启动后仿真。 2. **观察时序结果**:通过观察波形,验证设计是否满足时序要求。 #### 六、加载配置与下载调试 1. **生成配置文件**:在`Processes`面板中双击`Generate Programming File`选项即可完成。 2. **下载调试**:将生成的`.bit`文件下载到FPGA硬件上进行实际测试。 通过以上步骤,可以全面掌握使用ISE 14.7进行FPGA设计的整个流程,从源代码设计到最终的硬件测试,每一步都至关重要。

剩余25页未读,继续阅读

- 粉丝: 20

- 资源: 3

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

信息提交成功

信息提交成功