SpyGlass

®

DFT

Rules Reference Guide

Version L-2016.06, June 2016

Copyright Notice and Proprietary Information

©2016 Synopsys, Inc. All rights reserved. This Synopsys software and all associated

documentation are proprietary to Synopsys, Inc. and may only be used pursuant to the

terms and conditions of a written license agreement with Synopsys, Inc. All other use,

reproduction, modification, or distribution of the Synopsys software or the associated

documentation is strictly prohibited.

Destination Control Statement

All technical data contained in this publication is subject to the export control laws of the

United States of America. Disclosure to nationals of other countries contrary to United

States law is prohibited. It is the reader's responsibility to determine the applicable

regulations and to comply with them.

Disclaimer

SYNOPSYS, INC., AND ITS LICENSORS MAKE NO WARRANTY OF ANY KIND, EXPRESS

OR IMPLIED, WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO,

THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR

PURPOSE.

Trademarks

Synopsys and certain Synopsys product names are trademarks of Synopsys, as set forth

at http://www.synopsys.com/Company/Pages/Trademarks.aspx.

All other product or company names may be trademarks of their respective owners.

Third-Party Links

Any links to third-party websites included in this document are for your convenience

only. Synopsys does not endorse and is not responsible for such websites and their

practices, including privacy practices, availability, and content.

Synopsys, Inc.

690 E. Middlefield Road

Mountain View, CA 94043

www.synopsys.com

v

Synopsys, Inc.

Contents

Preface........................................................................................25

About This Book.................................................................................... 25

Contents of This Book ........................................................................... 26

Typographical Conventions ................................................................... 27

Understanding the SpyGlass DFT Product ...................................29

Key Concepts ........................................................................................ 30

RTL Design for Test..............................................................................31

SpyGlass DFT Design Constraints...........................................................39

Operating Modes .................................................................................48

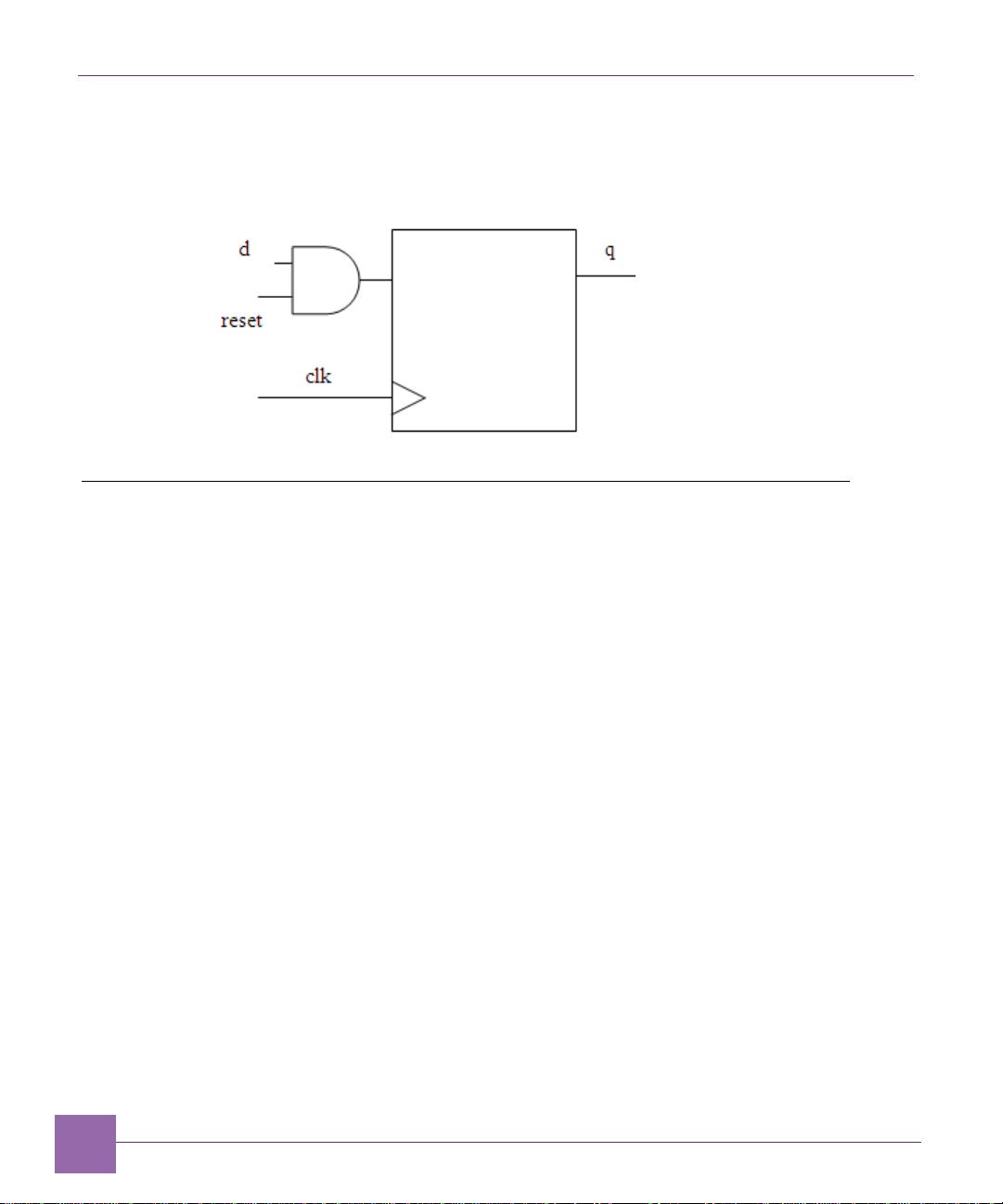

Types of Flip-Flops...............................................................................53

Types of Latches..................................................................................55

Identifying Clock Gating Cells................................................................60

Types of Faults....................................................................................72

Support for Multi-Bit Flip-Flop Cells........................................................79

Support For Clock Shaper with Scannable Flip- Flops................................80

Using AutoFix and Selective AutoFix.......................................................82

Identifying Test Points To Reduce Random Resistance ...............................84

Design Impact....................................................................................... 86

Scannability........................................................................................86

Improvements to Fault and Test Coverage...............................................87

Detecting Structures Leading to Non-Robust Tests....................................95

Suggested SpyGlass DFT Operation....................................................... 96

Use of Design Constraints.....................................................................97

Making the RTL scan ready ...................................................................99

Comply with SpyGlass DFT Best Practices .............................................102

Adding Test Points .............................................................................103

Identifying Testclocks.........................................................................104

Working with Scan Chains...................................................................105

Checking Block-level Test Requirements................................................108

Making the RTL Ready for Atspeed Test.................................................108