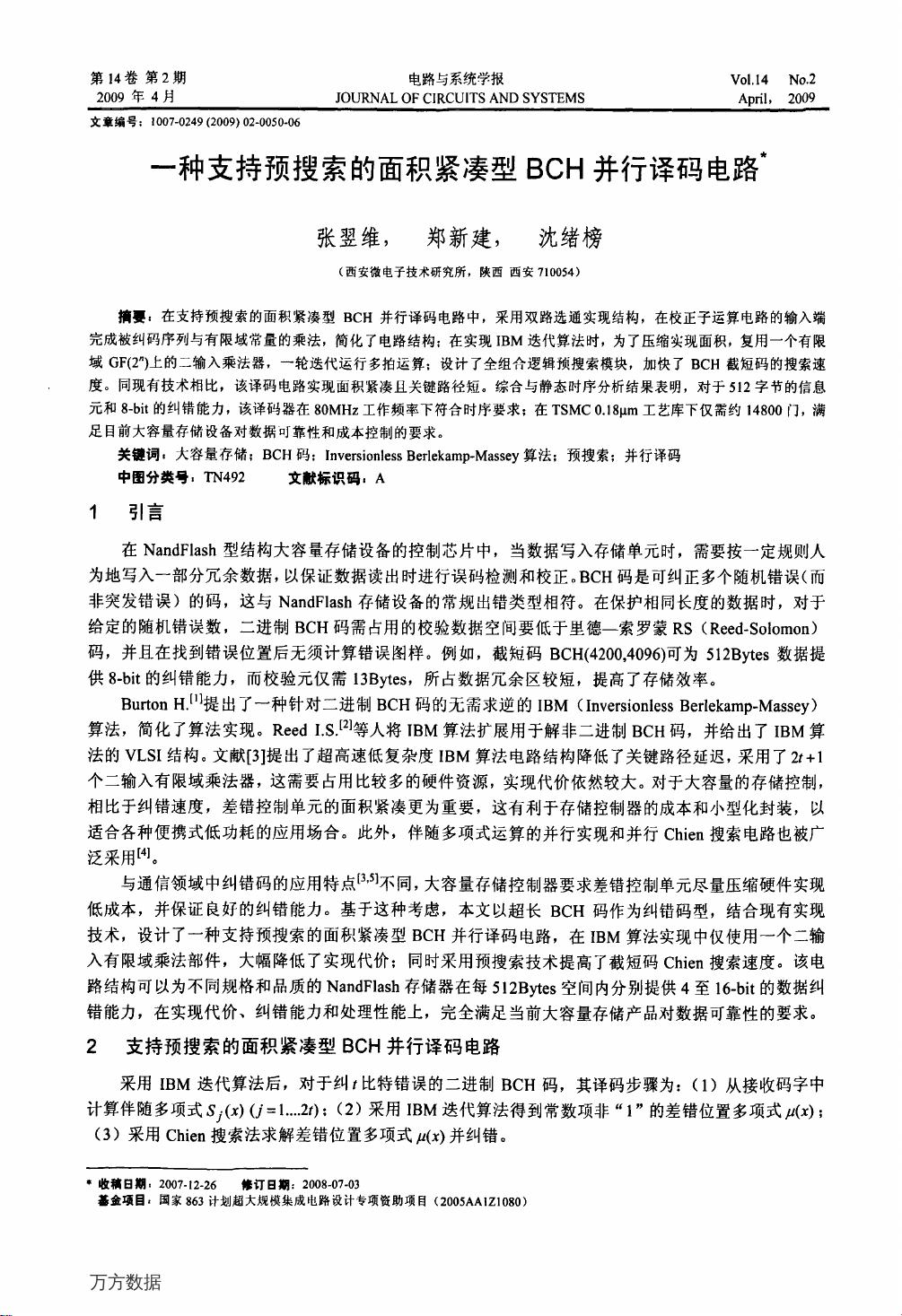

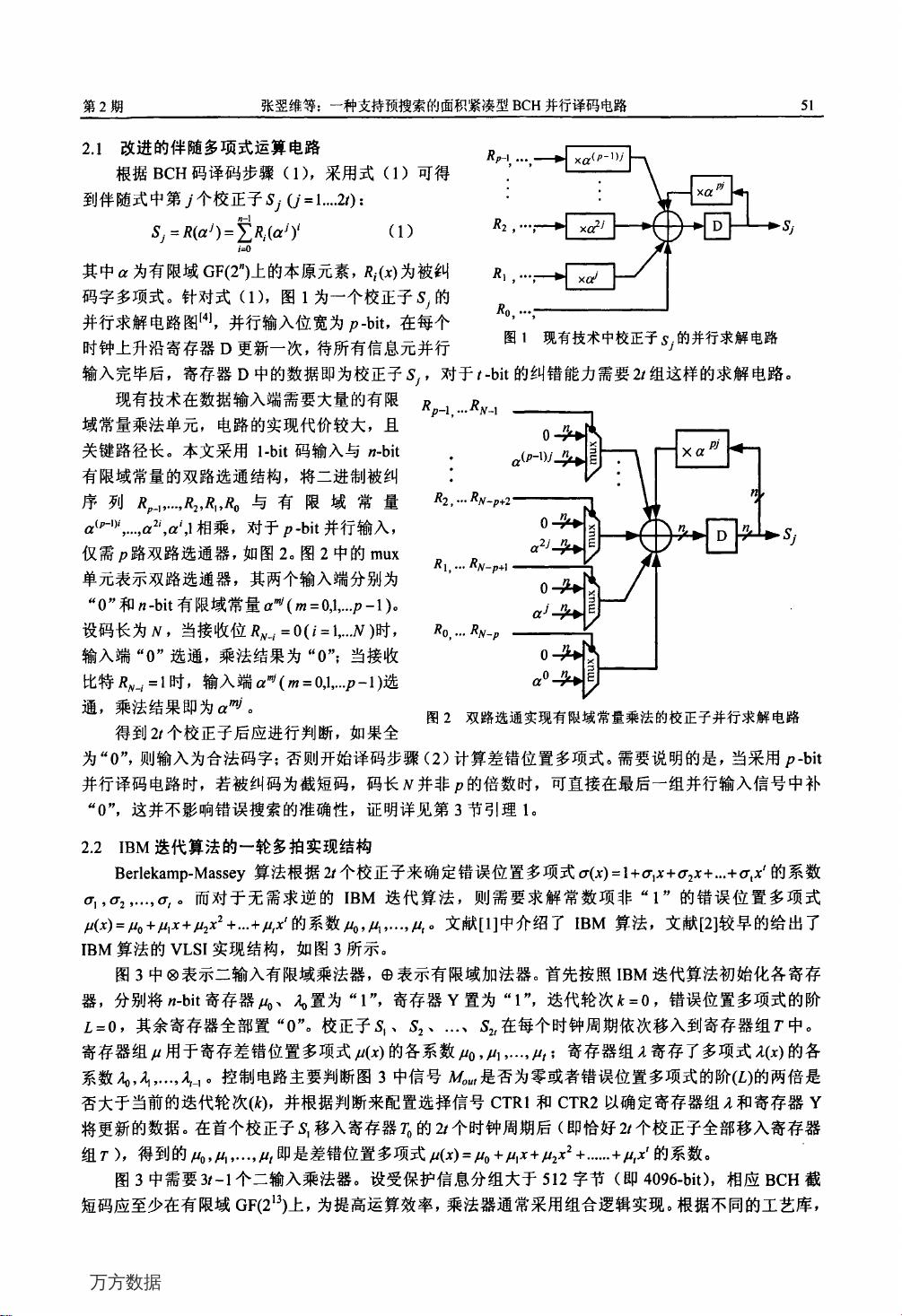

### 支持预搜索的面积紧凑型BCH并行译码电路详解 #### 一、引言 在当今数字化时代,大容量存储设备如Nand Flash已成为数据存储的关键技术之一,尤其是在便携式低功耗应用中发挥着至关重要的作用。然而,数据的可靠性和准确性是这类存储设备面临的重大挑战,尤其是考虑到存储单元可能发生的随机错误。因此,高效且可靠的错误检测和校正技术成为了确保数据完整性的核心。 BCH(Bose-Chaudhuri-Hocquenghem)码作为一种能够纠正多个随机错误的编码方式,因其在找到错误位置后无需额外计算错误图样的特性,成为大容量存储设备的理想选择。相较于其他编码方式,如Reed-Solomon码,BCH码在保护相同长度的数据时,对于给定的随机错误数,所需的校验数据空间更少,从而提高了存储效率。例如,截短码BCH(4200,4096)能够为512Bytes的数据提供8-bit的纠错能力,而校验元仅需13Bytes,显著减少了数据冗余。 #### 二、BCH并行译码电路设计要点 在设计BCH并行译码电路时,主要目标是实现面积紧凑的同时保证高效纠错能力。这通常涉及到几个关键技术点: 1. **预搜索技术**:预搜索技术可以显著提高截短码Chien搜索的速度,这对于实时或高吞吐量应用至关重要。通过预先确定可能的错误位置,可以在实际纠错过程中快速定位并纠正错误,从而提升整体性能。 2. **双路选通实现结构**:在校正子运算电路的输入端完成被纠码序列与有限域常量的乘法,这种方法简化了电路结构,减少了硬件资源的消耗,使得电路设计更加紧凑。 3. **有限域乘法器复用**:在实现IBM(Inversionless Berlekamp-Massey)迭代算法时,为了进一步压缩电路面积,采用复用一个有限域GF(2^m)上的二输入乘法器。这种方法通过多拍运算来实现迭代过程,虽然可能会稍微增加处理时间,但极大地节约了硬件资源。 4. **全组合逻辑预搜索模块**:设计全组合逻辑预搜索模块,不仅可以加速BCH截短码的搜索速度,还能减少电路中的延迟,进而缩短关键路径,提高整个系统的运行效率。 #### 三、技术细节与实现优势 在具体实现中,如文章所述,该译码电路采用IBM迭代算法,对于纠f比特错误的二进制BCH码,其译码步骤包括计算伴随多项式、使用IBM迭代算法得到差错位置多项式以及采用Chien搜索法求解并纠错。其中,改进的伴随多项式运算电路通过并行求解电路图来提高计算效率,同时通过双路选通和有限域乘法器的复用来降低硬件成本。 该电路设计在80MHz工作频率下,对于512字节的信息元和8-bit的纠错能力,不仅符合时序要求,而且在TSMC 0.18μm工艺库下只需约14800门,满足了大容量存储设备对数据可靠性和成本控制的双重需求。 #### 四、结论 支持预搜索的面积紧凑型BCH并行译码电路的设计与实现,为大容量存储设备提供了一种高效、可靠且成本效益高的数据纠错解决方案。通过优化电路结构和算法实现,该电路在保持高性能的同时,显著降低了硬件资源消耗,为便携式低功耗应用场合提供了理想的存储控制技术。 此设计充分体现了在追求更高数据存储密度和可靠性的同时,如何平衡硬件成本和性能优化,为未来大容量存储设备的发展奠定了坚实的基础。

剩余6页未读,继续阅读

- 粉丝: 0

- 资源: 1

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 没用333333333333333333333333333333

- 基于Vue和SpringBoot的企业员工管理系统2.0版本设计源码

- 【C++初级程序设计·配套源码】第2期-基本数据类型

- 基于Java和Vue的kopsoftKANBAN车间电子看板设计源码

- 影驰战将PS3111 东芝芯片TT18G23AIN开卡成功分享,图片里面画线的选项很重要

- 【C++初级程序设计·配套源码】第1期-语法基础

- 基于JavaScript、CSS、HTML的简易DOM版飞机游戏设计源码

- 基于Java开发的日程管理FlexTime应用设计源码

- SM2258XT-BGA144-4BGA180-6L-R1019 三星KLUCG4J1CB B0B1颗粒开盘工具 , EC, 3A, 94, 43, A4, CA 七彩虹SL300这个固件有用

- GJB 5236-2004 军用软件质量度量

信息提交成功

信息提交成功