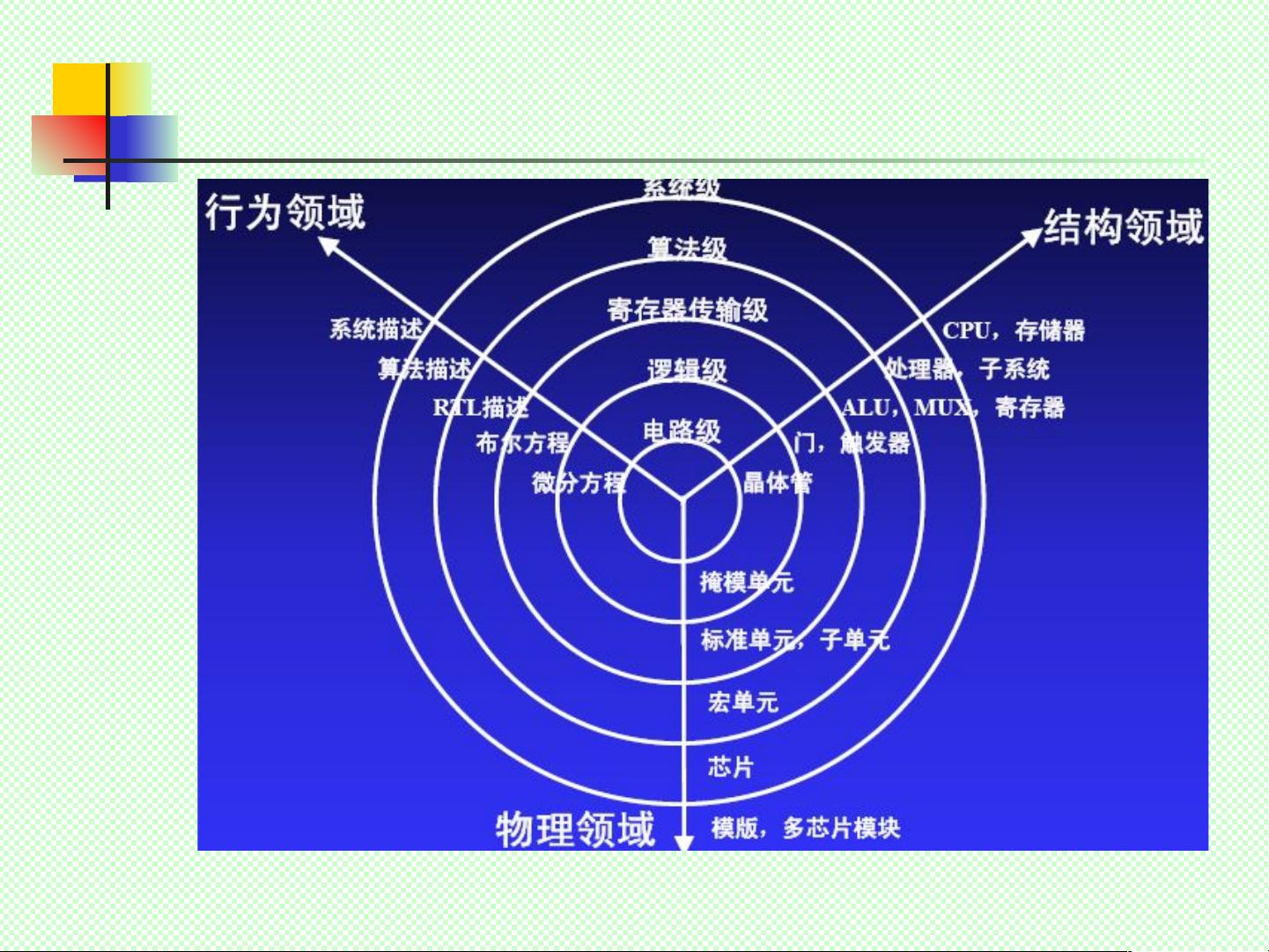

EDA技术,即电子设计自动化(Electronic Design Automation),是现代集成电路设计的核心工具,它通过软件工具实现芯片设计的自动化,涵盖了从系统级到门级直至电路级的整个设计过程。这一技术的发展与VHDL(VHSIC Hardware Description Language)等硬件描述语言紧密相关。

VHDL是一种用于数字系统的硬件描述语言,它允许工程师以行为、结构和混合级别对系统进行建模。自1987年IEEE Std VHDL 1076-1987标准发布以来,VHDL经历了多次更新,如1993年的修订版,以及与其他语言如Verilog HDL和SystemC的竞争与共同发展。Verilog HDL在功能建模方面与VHDL相当,但在美国的应用率略高于VHDL,大约为60%对40%。

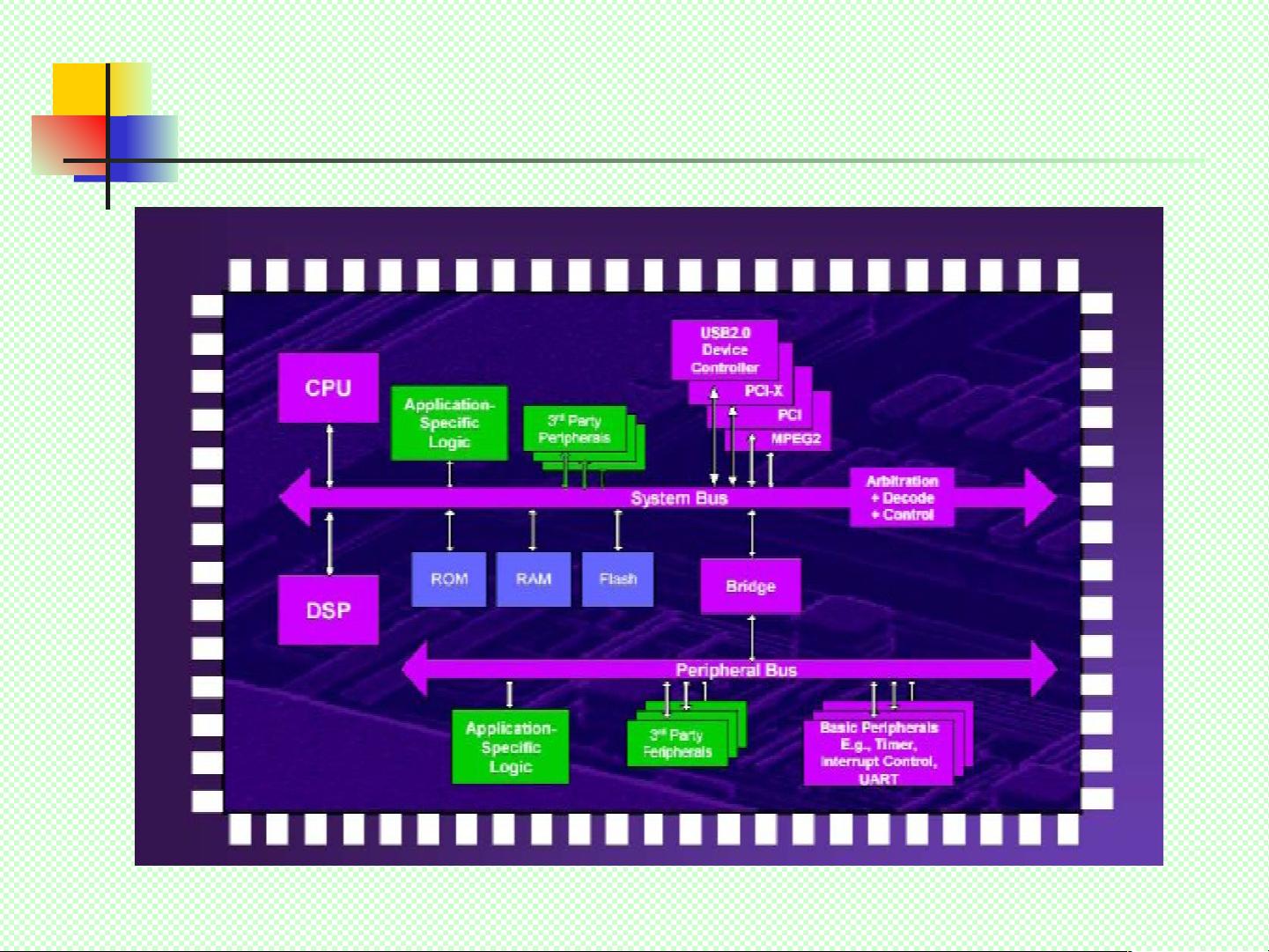

EDA技术的进步显著缩短了集成电路(IC)的设计周期,提高了设计效率。随着摩尔定律的推进,集成电路上的晶体管数量每18个月翻一番,IC工艺指标如光刻精度和晶圆尺寸也在不断演进。例如,从350纳米到现在的28纳米甚至更小,这使得在单个芯片上实现System-on-a-Chip(SoC)成为可能,即在一个芯片上集成完整的系统。

在ASIC(Application Specific Integrated Circuits)设计中,有全定制和半定制两种方法。全定制设计虽然速度快、功耗低,但设计周期长、成本高昂,适合大批量生产。而半定制设计,如门阵列MPGA、标准单元CBIC、PLD/CPLD和FPGA,提供了更快的设计周期和更低的成本,牺牲了一部分性能和功耗。其中,FPGA(Field Programmable Gate Array)因其可编程性,允许设计者根据需求进行配置,广泛应用于原型验证和快速原型开发。

设计流程通常包括高层次的系统级描述,然后逐步细化到寄存器传输级、逻辑门级,最后到开关电路级。VHDL和Verilog等HDL工具在这一过程中扮演着关键角色,它们使设计者能够采用自顶向下的设计方法,将复杂系统分解为可管理的模块,每个模块都可以独立验证和优化,最终组合成完整的设计。这种模块化方法提高了设计的可重用性和可移植性,降低了因工艺或结构变化带来的设计风险。

综合是EDA流程中的重要步骤,它将高级语言描述转化为逻辑门级的网络列表,以便于布局和布线。综合流程可以包括功能综合、时序优化和物理综合等步骤,以满足性能、面积和功耗等目标。

EDA技术是现代电子设计的基石,它通过VHDL等HDL工具和先进的设计方法,实现了从概念到芯片的高效自动化设计。随着技术的不断发展,EDA将继续推动集成电路设计的创新,满足不断增长的计算和通信需求。