taojishuang

- 粉丝: 37

- 资源: 3

最新资源

- 智能能源管理系统市场报告:未来几年年复合增长率CAGR为7.1%

- SDL2-2.30.1.tar.gz

- 实验六、Linux RPM与YUM软件包管理实验.doc

- 新冠病毒图像分类数据集【已标注,约19,000张数据】

- 电气数据137节点配电网数据

- Ubuntu环境下编译与安装fswebcam-图像捕捉工具详解

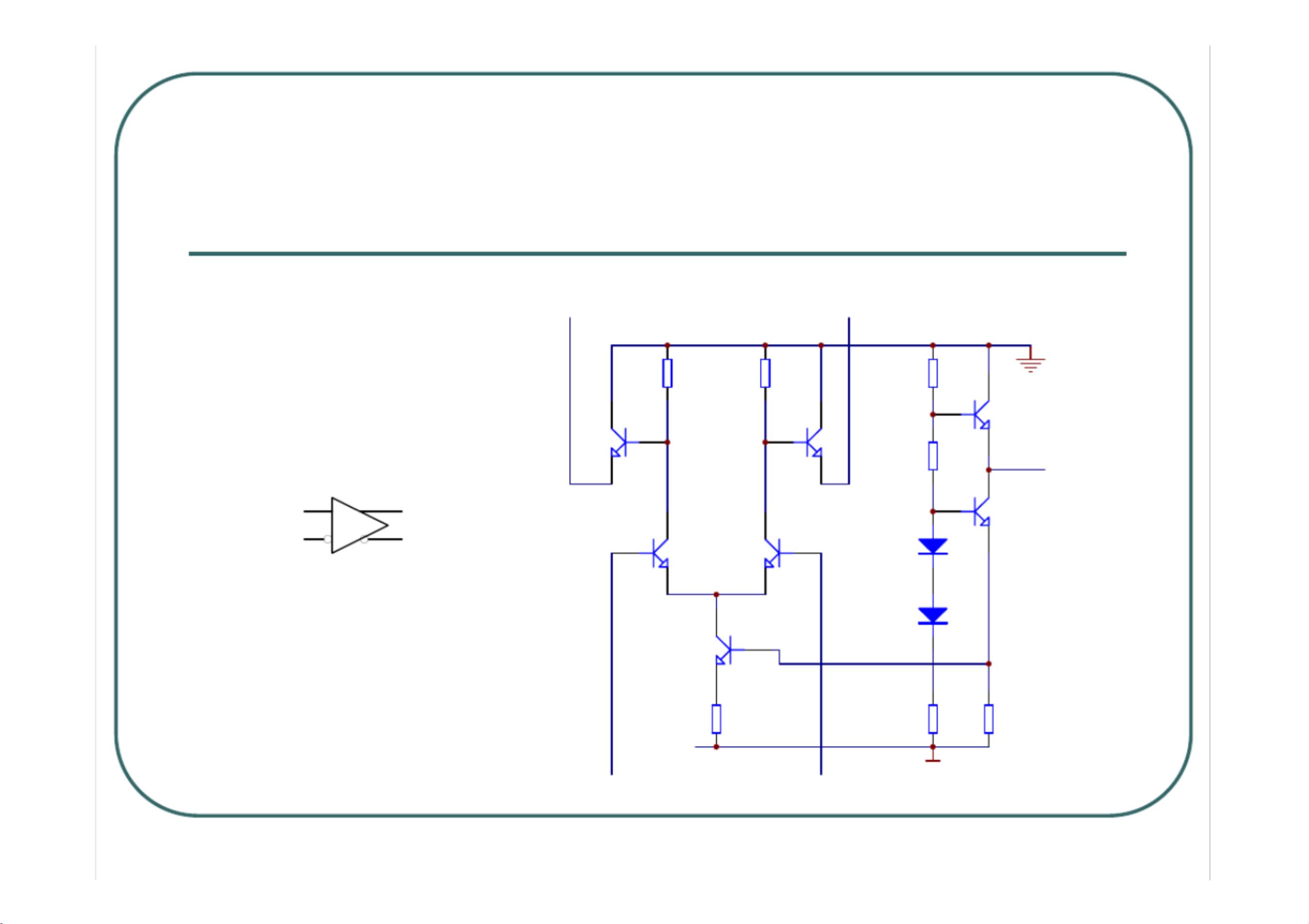

- simplorer与Maxwell电机联合仿真,包含搭建好的Simplorer电机场路耦合主电路与控制算法(矢量控制SVPWM),包含电路与算法搭建的详细教程视频 仿真文件可复制,可将教程中的电机模

- NC Cloud-环境-NCC常用数据表

- fswebcam-20140113.orig.tar.xz

- 电气数据85节点配电网数据

- BLDC无刷直流电机仿真 双闭环 PWM PI控制 无刷直流电机仿真 sinulink 双闭环调速系统 整理好的文档,资料很详细 有详细的参数说明

- deeplabv3+街景图片语义分割,无需训练模型,看不懂也没有影响,直接使用,cityscapes数据集

- Thinkphp响应式电器使用说明书网站模板+前后端源码

- 实验七、Linux gcc源码编译实验.doc

- 一个使用 HTML 构建界面,JavaScript 实现逻辑的简易计算器源码

- NC Cloud-档案-单表开发

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈