freescale单片机

需积分: 0 91 浏览量

更新于2011-11-15

收藏 2.53MB PDF 举报

**freescale单片机DP256B的存储空间分布与锁相环工作原理**

在深入了解freescale单片机DP256B的存储空间分布与锁相环工作原理之前,我们先来概述一下这款单片机的核心特点。freescale DP256B是一款高性能的微控制器,它提供了丰富的存储资源和先进的锁相环技术,使其成为工业自动化、汽车电子及其它复杂应用的理想选择。

### 存储空间分布

#### Flash存储器

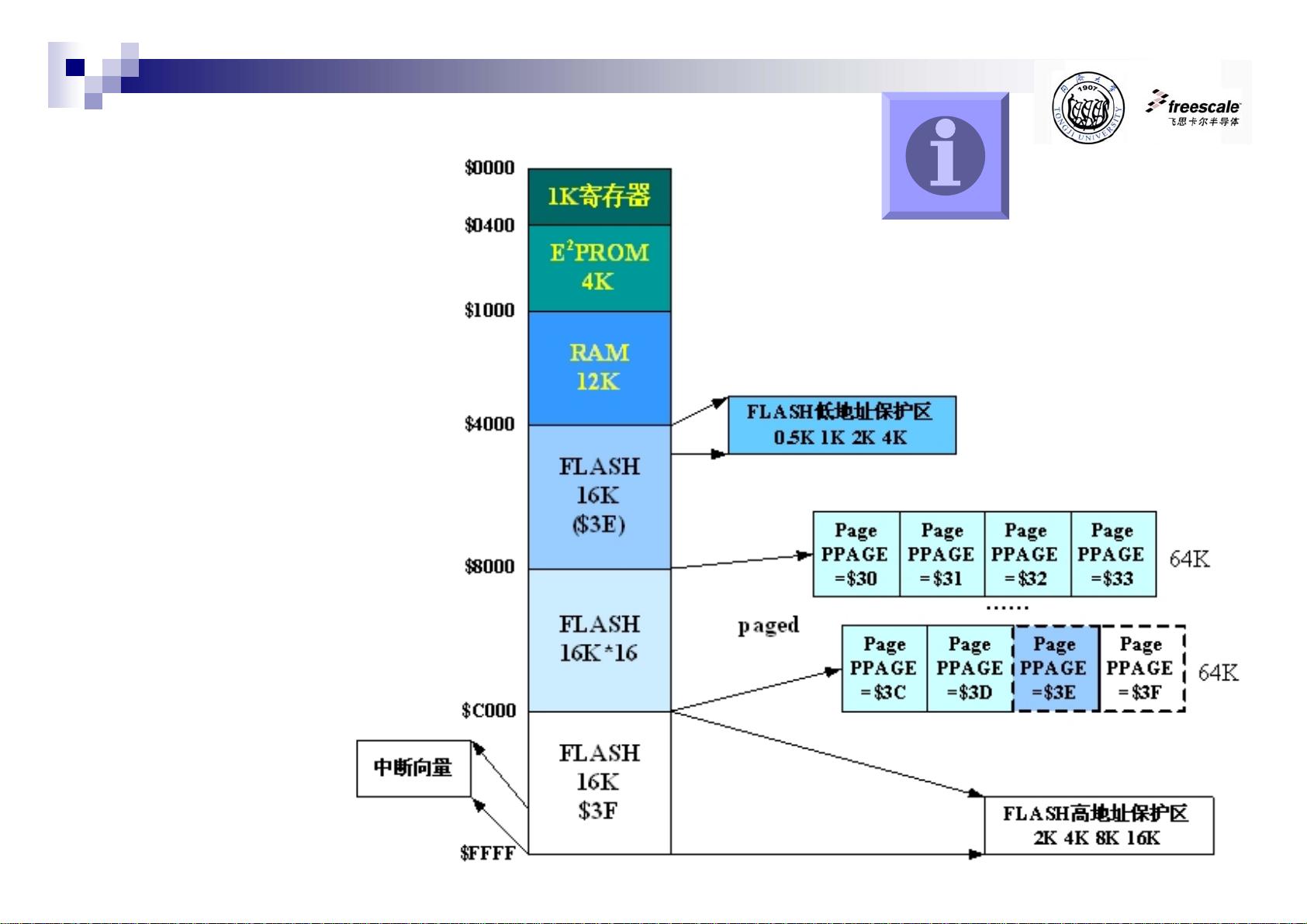

DP256B内建了256KB的Flash存储器,用于存储程序代码和非易失性数据。Flash被划分为多个区域,包括不可分页和可分页的部分。不可分页的Flash位于地址$4000-$7FFF和$C000-$FFFF,可分页的Flash位于$8000-$BFFF,可通过分页寄存器PPGAE进行管理,其值在0x30到0x3F之间。此外,$FF00-$FFFF区域包含256字节的中断向量表,对于处理中断事件至关重要。

#### RAM与E2PROM

该单片机还配备了12KB的RAM,用于临时数据存储,其默认地址范围为$1000-$3FFF,可根据需要重新定位。4KB的E2PROM用于存储需持久化的配置数据,其默认地址范围为$0000-$0FFF,同样支持重新定位。

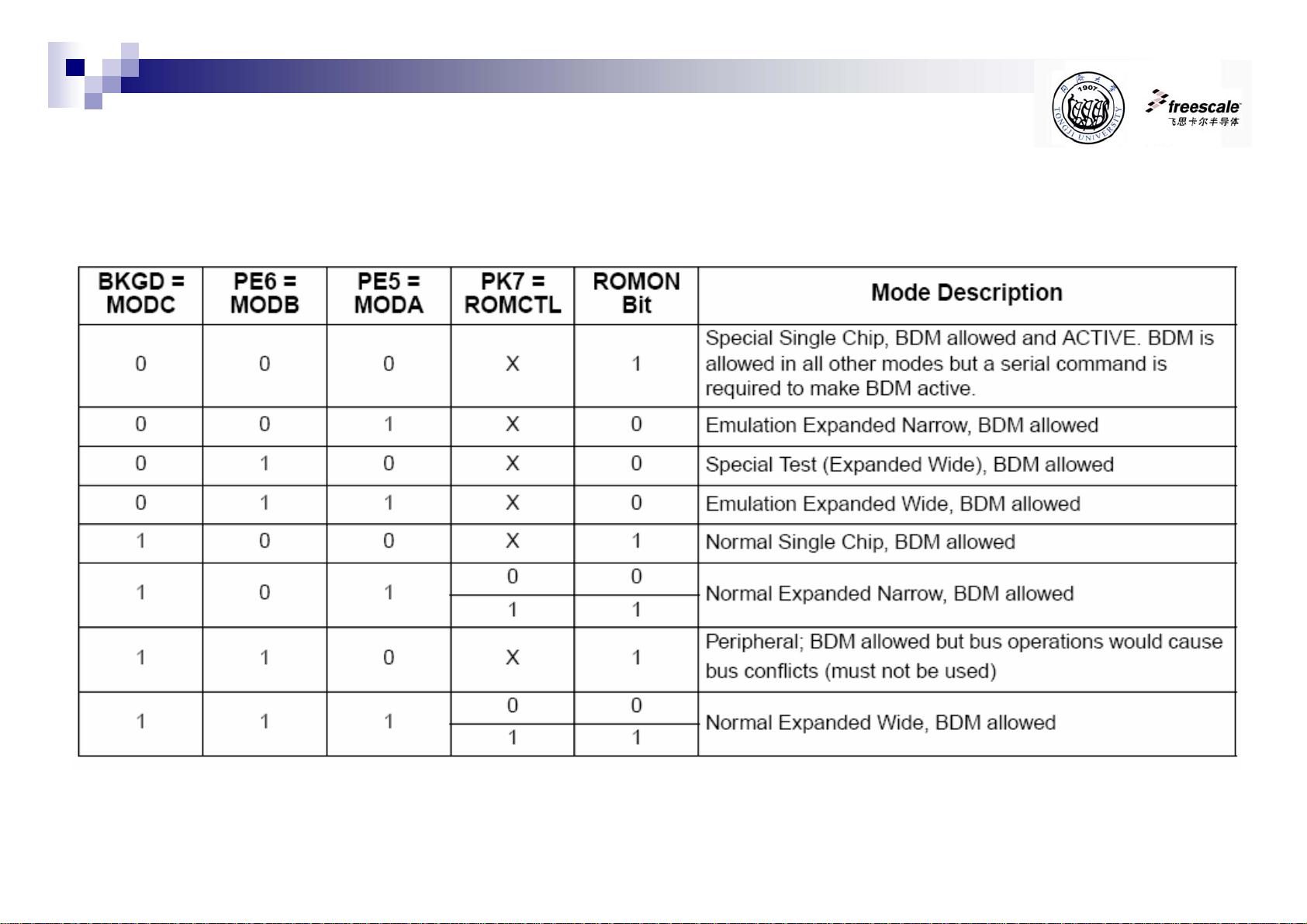

#### 工作模式下的存储空间配置

DP256B支持多种工作模式,包括单片模式、窄扩展模式、宽扩展模式、仿真窄扩展模式和仿真宽扩展模式。在单片模式下,系统将直接跳转至后台调试模式,而不加载复位向量或执行应用程序。其他模式则涉及不同的总线控制功能和系统控制信号,特别是仿真模式下,某些功能会受到限制。

### 寄存器配置

单片机的寄存器空间分配于$0000-$03FF,其中包含了模块寄存器、配置寄存器和保留字节。这些寄存器可定位在前32KB内存中的任何1KB位置,具体位置由INITRG寄存器决定。类似地,E2PROM和RAM的空间定位分别由INITEE和INITRM寄存器控制。

### 锁相环(PLL)工作原理

锁相环是DP256B的一个关键特性,用于时钟信号的生成和调整,以确保系统运行的稳定性和准确性。PLL的基本组成部分包括基准频率源、鉴相器、低通滤波器、压控振荡器和分频器。其工作原理可以概括为通过比较输入参考频率与输出频率的相位差,调整压控振荡器的频率,最终使输出频率稳定并精确地锁定在目标频率上。

#### PLL的配置与模式切换

PLL可以通过配置SYNR和REFDV寄存器来调整输出频率。例如,若晶振频率为16MHz,欲得到32MHz的PLL时钟,只需将这两个寄存器设为0即可。PLL的工作模式有获取模式和跟踪模式,前者用于系统启动或受到干扰后的频率快速锁定,后者则用于保持已锁定频率的稳定性。通过手动或自动切换模式,可优化频率的精度和稳定性。

#### 初始化设置

为了使PLL正常工作,需要进行一系列初始化设置,包括选择PLL作为系统时钟源、设置PLL控制寄存器等步骤。CLKSEL寄存器用于选择时钟源,而PLLCTL寄存器则用于控制PLL的开关状态、切换模式和选择工作模式。通过合理配置这些寄存器,可以确保DP256B单片机在不同应用场景下高效、稳定地运行。

freescale DP256B单片机的存储空间分布和锁相环工作原理是其性能表现的关键因素。理解并掌握这些特性,将有助于开发者充分利用这款单片机的强大功能,设计出更稳定、更高效的嵌入式系统。

SYH1546601

- 粉丝: 0

- 资源: 1

最新资源

- ASL6328芯片规格说明书

- 基于Matlab实现智能体一阶有领导者仿真(源码+数据).rar

- 独立公众号版本微信社群人脉系统社群空间站最新源码+详细教程

- 森林图像数据集(2700张图片).rar

- 《基于Comsol仿真模拟的岩石损伤研究-水力压裂实验探究》,利用Comsol仿真模拟技术精确预测水力压裂过程中岩石损伤情况,comsol仿真模拟水力压裂岩石损伤 ,关键词:COMSOL仿真;水

- 自由方舟管理后台通用模板-基于TDesign二次优化

- 《学习CRUISE M热管理的视频教程及文档解说,无需模型,轻松入门》,CRUISE M热管理视频教程:无模型,文档解说,轻松学习掌握热管理知识,录的CRUISE M热管理视频,有文档解说,没有模型

- 洛杉矶犯罪数据集概览 (2020年至今),犯罪事件数据集,犯罪影响因素

- 电信客户流失数据集,运营商流失客户数据集

- FinalBurn Neo源代码

- 基于积分型滑模控制器的永磁同步电机FOC转速环设计及仿真模型参考,基于积分型滑模控制器的永磁同步电机FOC转速环设计及仿真模型参考,基于积分型滑模控制器的永磁同步电机FOC 1.转速环基于积分型滑模面

- 智能车辆模拟系统:深度探究多步泊车,平行泊车与垂直泊车的仿真应用,《深入探讨carsim仿真技术下的多步泊车策略:平行泊车与垂直泊车的实现与优化》,carsim仿真多步泊车,平行泊车和垂直泊车 ,核心

- BMS模块Simulink开发基于算法,基于Simulink开发的BMS算法:包含SOC计算、故障处理与状态监测的充放电控制策略图解,BMS Simulink 所有算法基于Simulink开发 BMS

- 犯罪率与社会经济因素数据集,探讨了犯罪率与各种社会经济因素之间的关系,如教育水平、就业率、中位收入、贫困率和人口密度涵盖了1000个地区的数据

- ASL6328芯片原理图-V1.1

- 精品源码Javaweb仓库管理系统项目源码