在数电实验报告中,我们探索了数字电子技术的基础元素,包括译码器、全加器和计数器。这些是构建数字系统的核心组件,它们的工作原理和应用对于理解和设计现代电子设备至关重要。

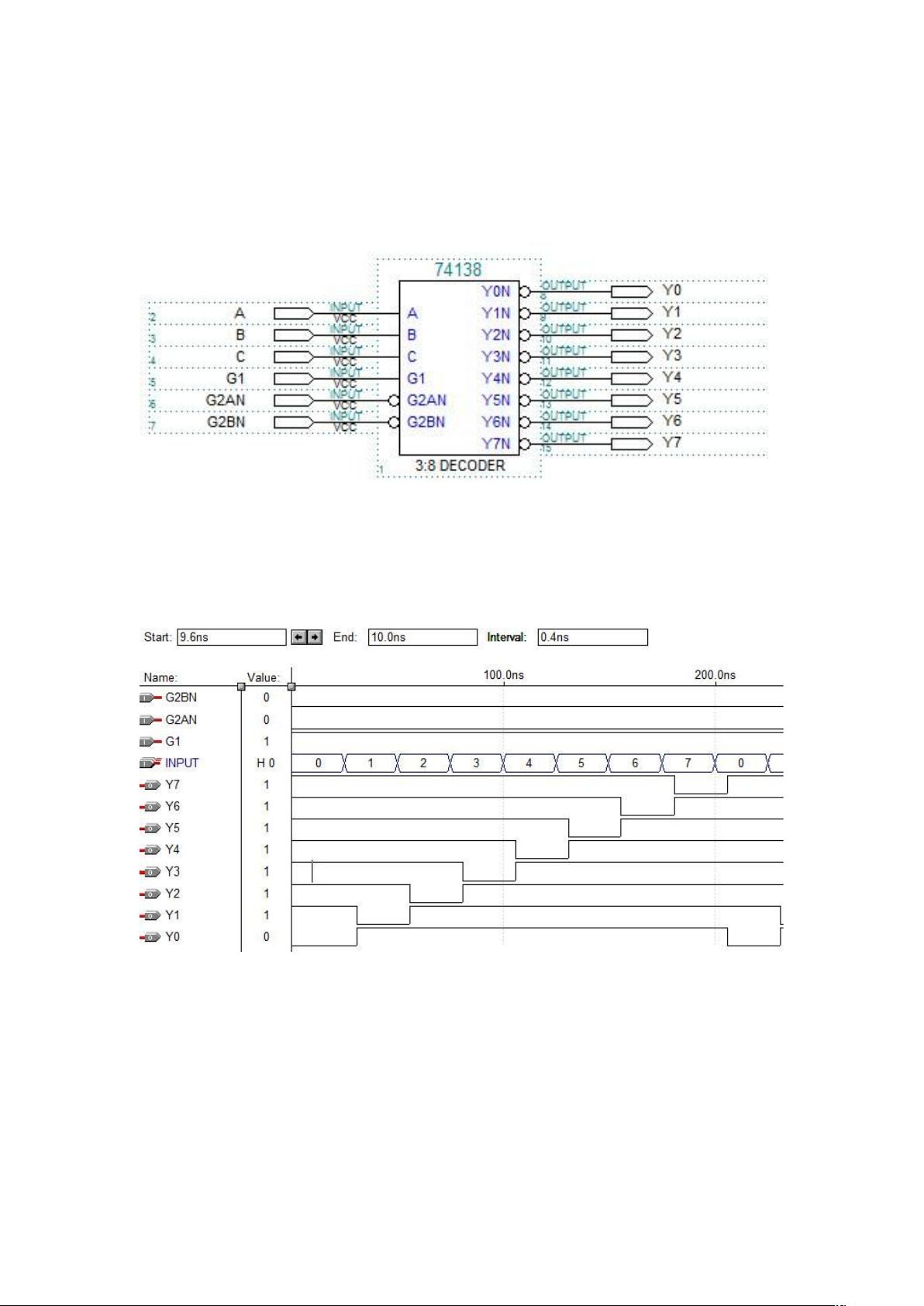

3-8译码器是一种多输入、多输出逻辑器件,它能将一个3位二进制输入转换为8个可能的输出状态中的一个。例如,当输入为000时,译码器的输出Y7-Y0全部为0,表示选择第0个输出;而当输入为111时,只有Y7为1,其余为0,表示选择第7个输出。实验中的波形图展示了随着输入变化,输出状态的动态过程,这有助于我们直观理解译码器的功能。

接着,我们研究了2-4译码器,这是一种稍微简单的译码器,它有两个输入和四个可能的输出。与3-8译码器类似,通过观察输出波形图,我们可以看到如何根据输入状态来激活特定的输出线。

实验三引入了4位二进制全加器,这是一个能同时对四位二进制数进行加法运算的电路。全加器不仅考虑了本位的加法,还处理了来自低位的进位。其原理电路图揭示了如何组合使用半加器和或门、异或门等基本逻辑门实现加法功能。波形图则展示出不同输入组合下,全加器的进位和本位加法结果的变化情况。

然后,D触发器在实验四中用于构建4位二进制计数器。D触发器是一种边沿触发的存储单元,它的输出在时钟脉冲上升沿时更新为输入D的值。通过级联多个D触发器,可以实现二进制计数器,每个触发器代表一位计数值。计数波形图清楚地显示了随着时钟脉冲的增加,计数器的计数值如何逐次递增。

实验五涉及到了模24计时器,这实际上是一个能够计数到23(因为24进位会回到0)的二进制计数器。模24计时器常用于定时任务,例如周期性的信号发生或定时开关控制。原理电路图通常会包含一系列触发器和逻辑门,用于实现计数逻辑。计时波形图则直观地描绘了计数器在每个时钟周期结束时的状态变化。

这些实验报告中的内容为我们提供了丰富的实践经验和理论理解,让我们深入掌握了数字电路的基本组件及其相互作用。通过分析电路图和波形图,我们可以更好地理解数字电子系统的工作原理,这对于进一步学习更复杂的数字系统设计以及未来在硬件工程领域的发展都具有重要意义。