没有合适的资源?快使用搜索试试~ 我知道了~

温馨提示

试读

27页

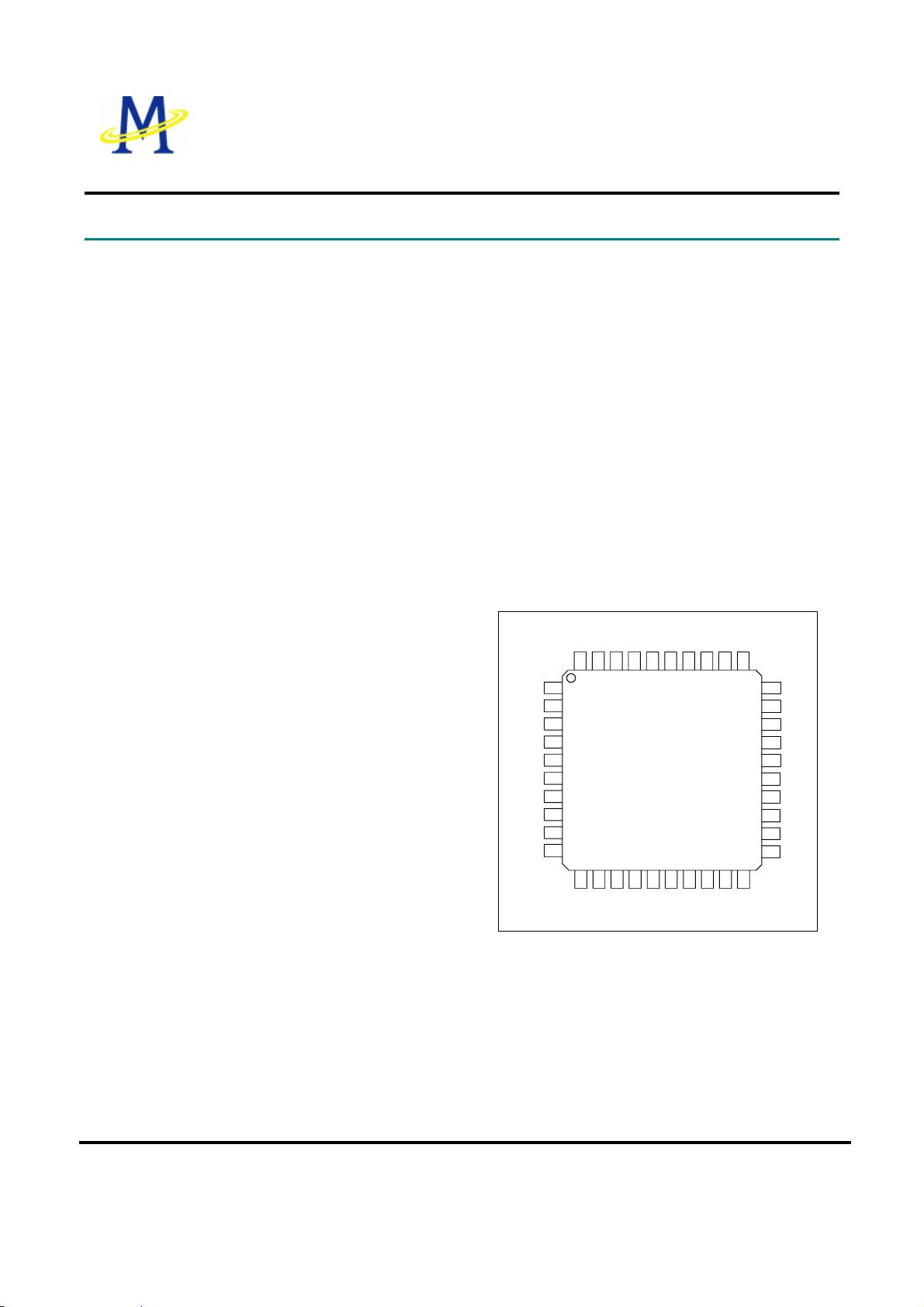

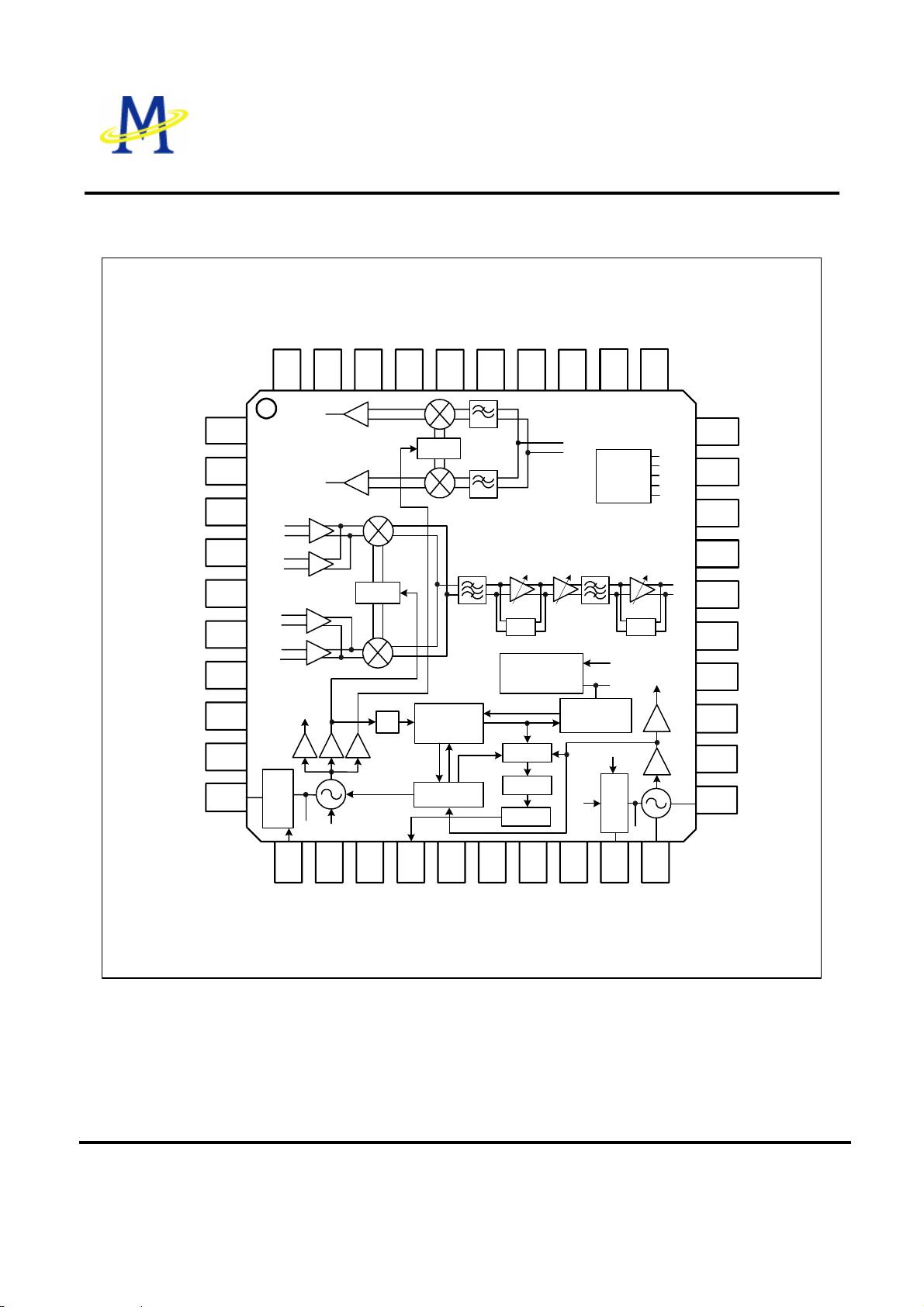

1.3 General Descriptions MT6139 is a highly-integrated RF transceiver IC for the Global Systems for Mobile Communication (GSM850/GSM900), Digital Cellular Communication Systems (DCS1800), and Personal Communication Services (PCS1900) cellular systems. It includes four LNAs, two RF quadrature mixers, a channel filter, a programmable-gain amplifier for the receiver, a high-precision I/Q modulator for the transmitter, a 26 MHz VCXO reference, a fractional-N frequency synthesizer with a fully-integrated LC-tank VCO and three built-in LDO regulators for VCO, VCXO and SDM. It is housed in a 40-pin QFN package with a downset paddle for additional grounding. Figure 1 shows the MT6139 functional block diagram.

资源推荐

资源详情

资源评论

MediaTek Inc.

MT6139 Data Sheet

29 Sep, 2006

V2.0

PRELIMINARY, SUBJECT TO CHANGE WITHOUT NOTICE

1

MTK CONFIDENTIAL, NO DISCLOSURE

MT6139 Data Sheet

MediaTek Inc.

MT6139 Data Sheet

29 Sep, 2006

V2.0

PRELIMINARY, SUBJECT TO CHANGE WITHOUT NOTICE

2

MTK CONFIDENTIAL, NO DISCLOSURE

Revision History

Revision Date Author Comments

0.1 2006/04/05 MH Tsai First draft release for MT6139

2.0 2006/09/29 Charles Chiu First release for MT6139

MediaTek Inc.

MT6139 Data Sheet

29 Sep, 2006

V2.0

PRELIMINARY, SUBJECT TO CHANGE WITHOUT NOTICE

3

MTK CONFIDENTIAL, NO DISCLOSURE

Table of contents

MT6139 Data Sheet................................................................................................................................................................. 1

Revision History...................................................................................................................................................................... 2

1 Introduction ................................................................................................................................................................... 4

1.1 Features.................................................................................................................................................................... 4

1.2 Applications .............................................................................................................................................................. 4

1.3 General Descriptions ................................................................................................................................................ 4

1.4 Functional Block Diagram......................................................................................................................................... 5

1.5 Pin Assignment and Description............................................................................................................................... 6

2 Functional Description ................................................................................................................................................. 7

2.1 Receiver.................................................................................................................................................................... 7

2.2 Transmitter................................................................................................................................................................ 7

2.3 RF Frequency Synthesizer ....................................................................................................................................... 7

2.3.1 Synthesizer System Description......................................................................................................................... 7

2.3.2 Synthesizer Frequency Programming ................................................................................................................ 8

2.3.3 Digital Frequency Calibration Loop .................................................................................................................... 8

2.3.4 Fast-Acquisition Option ...................................................................................................................................... 9

2.4 Voltage-Controlled Crystal Oscillator (VCXO) .......................................................................................................... 9

2.5 Regulator .................................................................................................................................................................. 9

3 MT6139 Hardware Control Pin Descriptions............................................................................................................. 10

4 Electrical Characteristics ........................................................................................................................................... 11

4.1 Absolute Maximum Ratings .................................................................................................................................... 11

4.2 Recommended Operating Range ........................................................................................................................... 11

4.3 DC Specifications ................................................................................................................................................... 12

5 Receiver Specifications.............................................................................................................................................. 13

6 Transmitter Specifications ......................................................................................................................................... 17

7 Frequency Synthesizer Specifications...................................................................................................................... 20

8 VCXO Specifications................................................................................................................................................... 21

9 Regulator Specifications ............................................................................................................................................ 22

9.1 Regulator 1 (SDM) Specifications........................................................................................................................... 22

9.2 Regulator 2 (VCO) Specifications........................................................................................................................... 22

9.3 Regulator 3 (VCXO) Specifications......................................................................................................................... 23

10 Package Dimensions .................................................................................................................................................. 24

11 Application Circuit ...................................................................................................................................................... 25

Bibliography References...................................................................................................................................................... 27

MediaTek Inc.

MT6139 Data Sheet

29 Sep, 2006

V2.0

PRELIMINARY, SUBJECT TO CHANGE WITHOUT NOTICE

4

MTK CONFIDENTIAL, NO DISCLOSURE

1 Introduction

1.1 Features

Receiver

- Direct-conversion architecture with automatic

DC-Offset Correction (DCOC) loops

- Quad-band differential-input LNAs

- Fully-integrated 135 kHz channel filter

- 93 dB gain with 60 dB gain control range

- No IIP2 calibration needed

Transmitter

- High-precision I/Q modulator

- Direct-conversion architecture

Frequency Synthesizer

- Fractional-N architecture with a built-in automatic

frequency calibration loop

- Fully-integrated wide-range VCO

- Semi-integrated loop filter

Voltage-Controlled Crystal Oscillator (VCXO)

- One-pin 26 MHz crystal oscillator

- On-chip programmable capacitor array

- On-chip varactor

Regulators

- Built-in low-noise, Low-DropOut (LDO) regulators

for Sigma-Delta Modulator (SDM), VCO, and

VCXO.

3-wire serial interface

0.35µm BiCMOS process

6x6 mm

2

40-pin Quad Flat No-lead (QFN) package

Lead-free/RoHS-compliant

1.2 Applications

GSM900 / DCS1800 dual-band handsets

GSM850 / PCS1900 dual-band handsets

GSM900 / DCS1800 / PCS1900 tri-band handsets

GSM850 / DCS1800 / PCS1900 tri-band handsets

1.3 General Descriptions

MT6139 is a highly-integrated RF transceiver IC for

the Global Systems for Mobile Communication

(GSM850/GSM900), Digital Cellular Communication

Systems (DCS1800), and Personal Communication

Services (PCS1900) cellular systems. It includes four

LNAs, two RF quadrature mixers, a channel filter, a

programmable-gain amplifier for the receiver, a

high-precision I/Q modulator for the transmitter, a 26

MHz VCXO reference, a fractional-N frequency

synthesizer with a fully-integrated LC-tank VCO and

three built-in LDO regulators for VCO, VCXO and

SDM. It is housed in a 40-pin QFN package with a

downset paddle for additional grounding. Figure 1

shows the MT6139 functional block diagram.

VCCRF

GSM850RF

CREG2

PCS1900RF

DCS1800RFB

GSM900RFB

DCS1800RF

VCCVCXO

REFOUT

XTAL

DATAIN

GPO

ENVCXO

ENRFVCO

VCCD

GNDD

VCCSDM

GSM850RFB

GSM900RF

PCS1900RFB

1

2

3

4

5

6

7

8

9

10

40

39

38

37

36

35

34

33

11

12

13

14

15

16

17

18

19

20

23

22

21

32

31

30

29

28

27

26

25

24

VCCREG2

VCOP

VCCRFVCO

RFTUNE

GNDRFVCO

VCCSYN

RFCPO

GNDSYN

CREG3

VAFC

VCCTXBUF

TXODPCS

TXOGSM

VCCTXMOD

I

IB

Q

QB

ENABLE

CLOCK

MT6139

MT6139 Pin Assignment (Top View)

MediaTek Inc.

MT6139 Data Sheet

29 Sep, 2006

V2.0

PRELIMINARY, SUBJECT TO CHANGE WITHOUT NOTICE

5

MTK CONFIDENTIAL, NO DISCLOSURE

1.4 Functional Block Diagram

VCCRF

GSM850RF

CREG2

PCS1900RF

DCS1800RFB

GSM900RFB

DCS1800RF

VCCVCXO

REFOUT

XTAL

DATAIN

GPO

ENVCXO

ENRFVCO

VCCD

GNDD

VCCSDM

GSM850RFB

GSM900RF

PCS1900RFB

1

2

3

4

5

6

7

8

9

10

40

39

38

37

36

35

34

33

11

12

13

14

15

16

17

18

19

20

23

22

21

32

31

30

29

28

27

26

25

24

PFD

Delta-Sigma

Modulator

Regulator

3-wire

Control

PLL

Calibration

GSM850

Channel Filter and PGA

I

32

31

30

29

28

22

Q

26

24

13

2

3

4

5

6

7

8

9

VCCREG2

VCOP

VCCRFVCO

RFTUNE

GNDRFVCO

VCCSYN

RFCPO

GNDSYN

CREG3

VAFC

VCCTXBUF

TXODPCS

TXOGSM

VCCTXMOD

I

IB

Q

QB

ENABLE

CLOCK

÷

2 /

÷4

38

39

GSM900

DCS1800

PCS1900

14

33

34

35

36

÷

2 /

÷4

CP

VCXO

Regulator

16

23

VCO

Regulator

12

Delta-Sigma

Modulator

27

÷

2

RF Multi-

Modulus

Divider

LPF

33

34

35

36

I

Q

DCOCDCOC

Figure 1 MT6139 Functional Block Diagram

剩余26页未读,继续阅读

资源评论

sunriseye

- 粉丝: 1

- 资源: 35

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功