HDL设计数字UART(中英文翻译).docx

2.虚拟产品一经售出概不退款(资源遇到问题,请及时私信上传者)

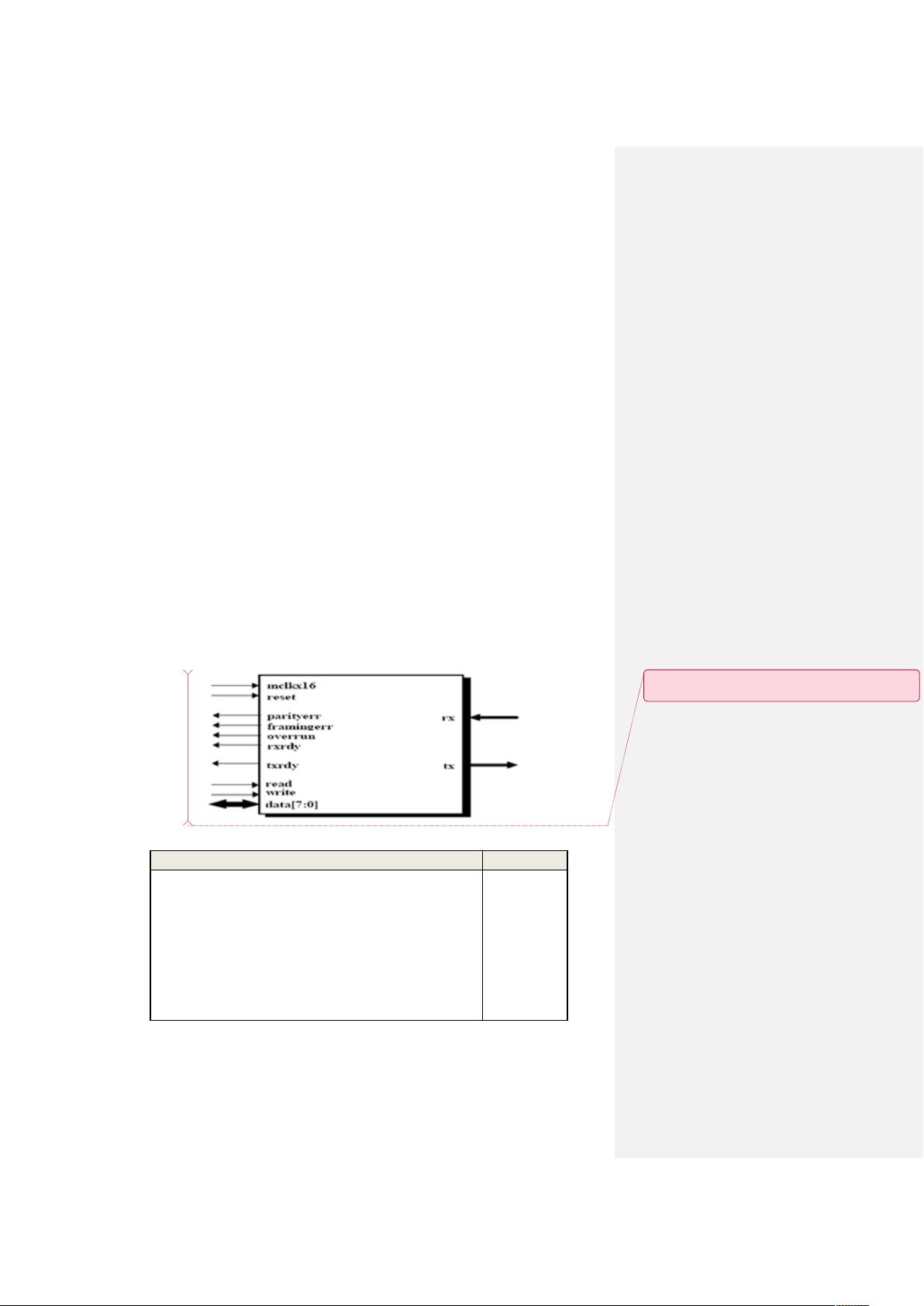

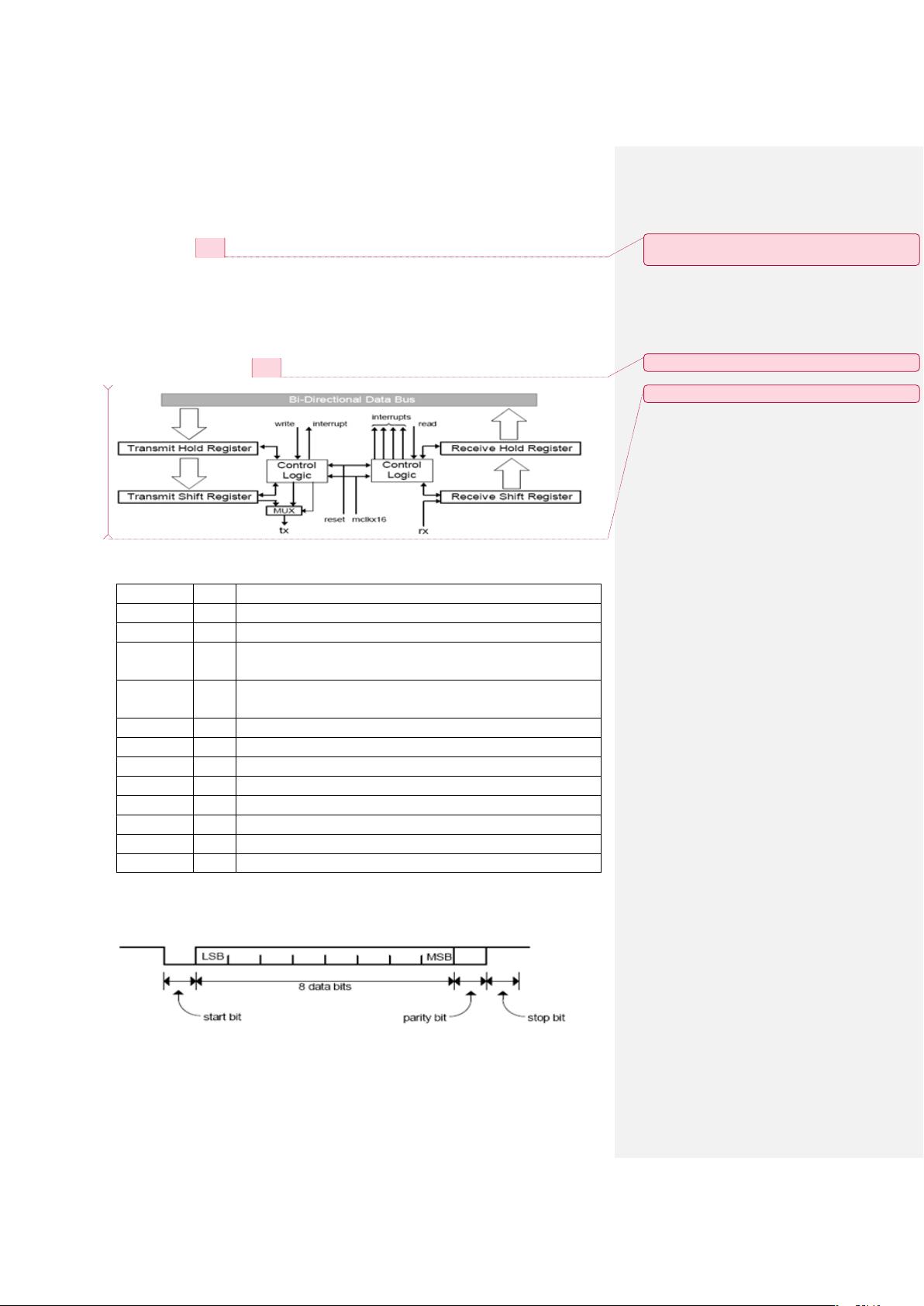

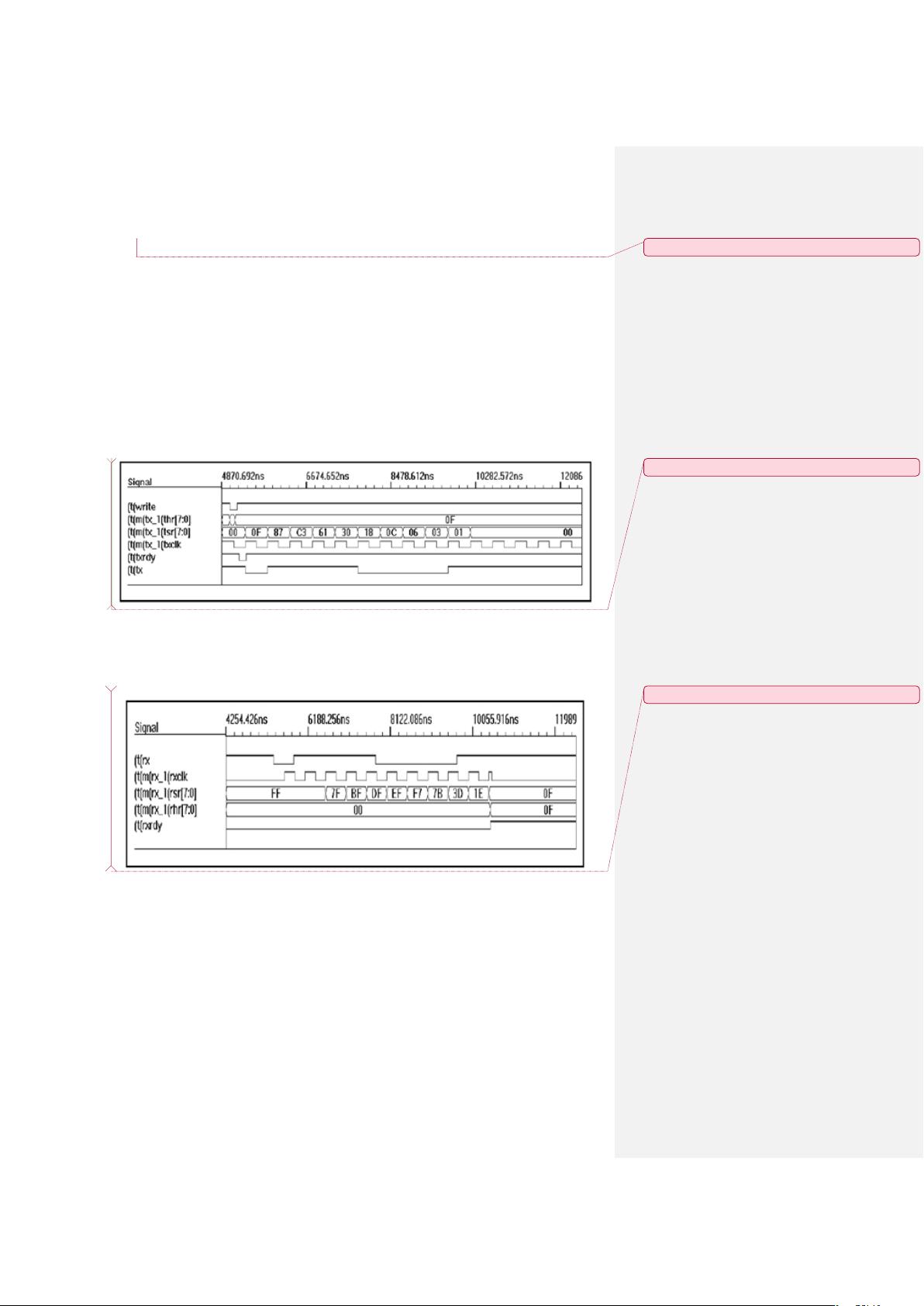

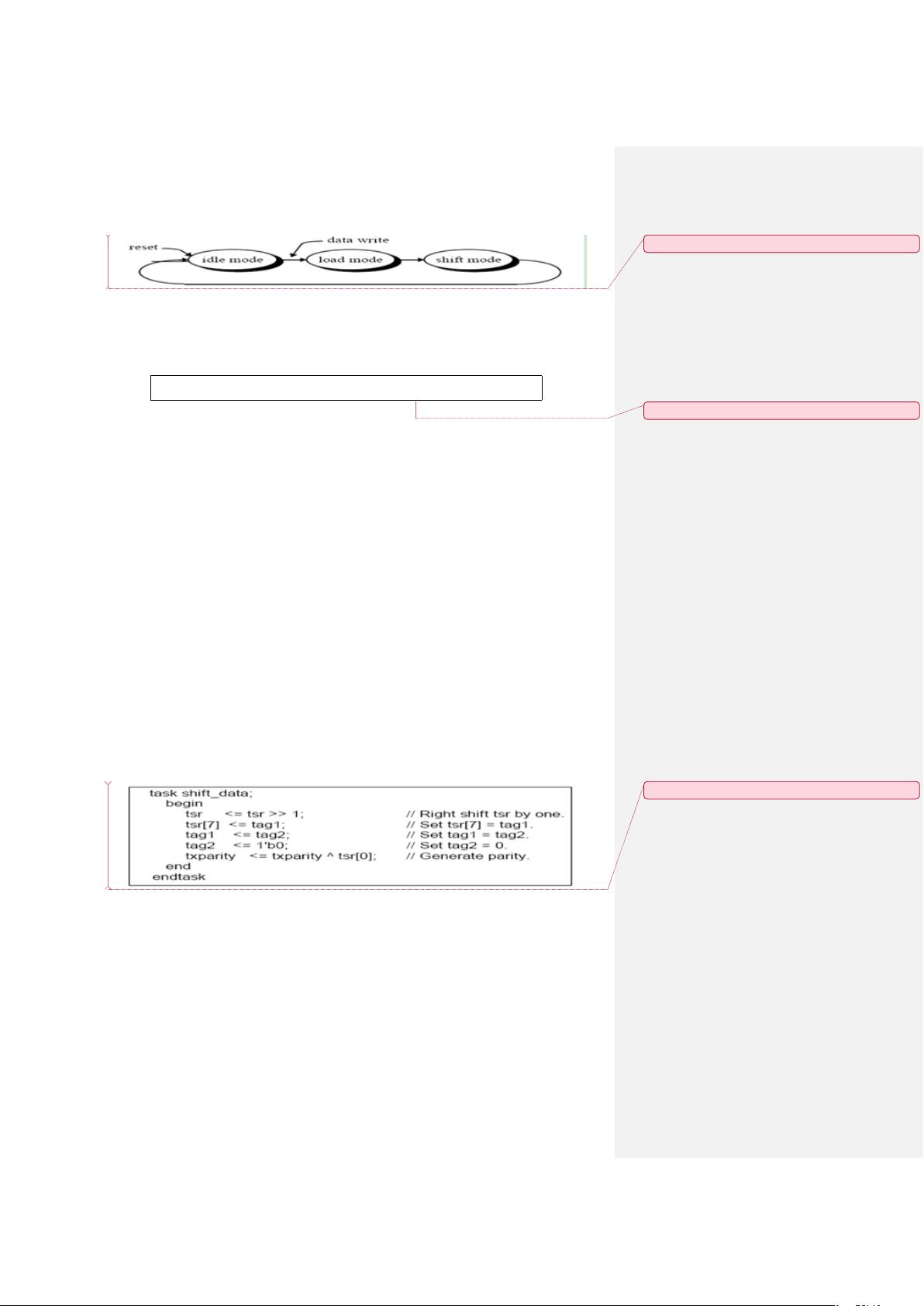

【UART(通用异步串行收发器)的HDL设计】 UART是一种广泛使用的通信协议,用于设备间的串行通信。在FPGA(现场可编程门阵列)设计中,使用硬件描述语言(HDL)如Verilog进行UART的设计和验证,能够提高设计效率和准确性。本文将详细阐述如何使用Verilog实现数字UART。 UART的核心由发射模块(Transmitter)和接收模块(Receiver)组成。发射模块负责将CPU提供的并行数据转换为串行流,而接收模块则将接收到的串行数据恢复为并行形式。在系统顶层,这两个模块通过共享的主时钟(mclkx16)和复位线连接,并通过双向数据总线(data[7:0])交换数据。发射和接收模块各自拥有独立的控制逻辑,确保全双工操作,即同时进行发送和接收。 UART的数据帧格式如图3所示,包含起始位、8位数据位、1位奇偶校验位和1位停止位。起始位通常为低电平,数据位按低位优先顺序排列,接着是奇偶校验位,根据配置可以是奇校验或偶校验。最后是停止位,通常为高电平,表示数据帧的结束。 发送时序如图4所示,主控时钟mclkx16经过分频得到波特率时钟txclk。数据并行写入发送模块,在波特率时钟的上升沿,数据逐位移出并通过tx输出端口发送。接收时序如图5所示,串行数据通过rx输入,逐位加载到接收移位寄存器,然后进入接收寄存器,当接收完成且无错误时,产生rxrdy标志,通知CPU数据已准备好读取。 UART的I/O接口定义了各种信号,包括输入的主时钟mclkx16、复位信号reset、写入和读取控制信号write和read,以及数据总线data[7:0]等。此外,还有错误检测标志如parityerr(奇偶校验错误)、framingerr(帧错误)和overrun(溢出错误),以及状态指示txrdy(发送就绪)和rxrdy(接收就绪)。 总结来说,设计一个基于HDL的UART涉及到以下几个关键步骤: 1. 定义UART的数据帧格式。 2. 设计发射模块,实现并行到串行的转换。 3. 设计接收模块,实现串行到并行的转换。 4. 分频主时钟,生成波特率时钟。 5. 实现错误检测和状态指示功能。 6. 集成顶层设计,将发射和接收模块与CPU接口相连。 通过这样的设计,开发者可以在FPGA中构建出一个完整的UART通信系统,实现高效、可靠的串行通信功能。

剩余49页未读,继续阅读

- 粉丝: 228

- 资源: 2万+

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- TOWER DEFENSE ZOMBIE WAR [1.01].zip

- GBT 27930 国标充电CAN报文解析 DBC文件

- 毕业设计基于C++和QT开发的智能售货系统(饮料售卖机)源码(高分毕设)

- TH2024005基于微信平台的文玩交易小程序ssm.zip

- java高校职工工资管理系统

- 零基础学AI-python语言:python基础语法(课件部分)

- IMT5G推进组发布5G无人机应用白皮书

- 基于Java SSM写的停车场管理系统,加入了车牌识别和数据分析

- 2025年P气瓶充装模拟考试卷

- 【java毕业设计】基于spring boot心理健康服务系统(springboot+vue+mysql+说明文档).zip

信息提交成功

信息提交成功