没有合适的资源?快使用搜索试试~ 我知道了~

LPC1700系列ARM基于第二代ARM Cortex-M3内核的微控制器

资源推荐

资源详情

资源评论

1. General description

The LPC1759/58/56/54/52/51 are ARM Cortex-M3 based microcontrollers for embedded

applications featuring a high level of integration and low power consumption. The ARM

Cortex-M3 is a next generation core that offers system enhancements such as enhanced

debug features and a higher level of support block integration.

The LPC1758/56/57/54/52/51 operate at CPU frequencies of up to 100 MHz. The

LPC1759 operates at CPU frequencies of up to 120 MHz. The ARM Cortex-M3 CPU

incorporates a 3-stage pipeline and uses a Harvard architecture with separate local

instruction and data buses as well as a third bus for peripherals. The ARM Cortex-M3

CPU also includes an internal prefetch unit that supports speculative branching.

The peripheral complement of the LPC1759/58/56/54/52/51 includes up to 512 kB of flash

memory, up to 64 kB of data memory, Ethernet MAC, USB Device/Host/OTG interface,

8-channel general purpose DMA controller, 4 UARTs, 2 CAN channels, 2 SSP controllers,

SPI interface, 2 I

2

C-bus interfaces, 2-input plus 2-output I

2

S-bus interface, 6 channel

12-bit ADC, 10-bit DAC, motor control PWM, Quadrature Encoder interface, 4 general

purpose timers, 6-output general purpose PWM, ultra-low power Real-Time Clock (RTC)

with separate battery supply, and up to 52 general purpose I/O pins.

2. Features and benefits

ARM Cortex-M3 processor, running at frequencies of up to 100 MHz

(LPC1758/56/57/54/52/51) or of up to 120 MHz (LPC1759). A Memory Protection Unit

(MPU) supporting eight regions is included.

ARM Cortex-M3 built-in Nested Vectored Interrupt Controller (NVIC).

Up to 512 kB on-chip flash programming memory. Enhanced flash memory accelerator

enables high-speed 120 MHz operation with zero wait states.

In-System Programming (ISP) and In-Application Programming (IAP) via on-chip

bootloader software.

On-chip SRAM includes:

Up to 32 kB of SRAM on the CPU with local code/data bus for high-performance

CPU access.

Two/one 16 kB SRAM blocks with separate access paths for higher throughput.

These SRAM blocks may be used for Ethernet (LPC1758 only), USB, and DMA

memory, as well as for general purpose CPU instruction and data storage.

Eight channel General Purpose DMA controller (GPDMA) on the AHB multilayer

matrix that can be used with the SSP, I

2

S-bus, UART, the Analog-to-Digital and

Digital-to-Analog converter peripherals, timer match signals, and for

memory-to-memory transfers.

LPC1759/58/56/54/52/51

32-bit ARM Cortex-M3 MCU; up to 512 kB flash and 64 kB

SRAM with Ethernet, USB 2.0 Host/Device/OTG, CAN

Rev. 6 — 25 August 2010 Product data sheet

LPC1759_58_56_54_52_51 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2010. All rights reserved.

Product data sheet Rev. 6 — 25 August 2010 2 of 73

NXP Semiconductors

LPC1759/58/56/54/52/51

32-bit ARM Cortex-M3 microcontroller

Multilayer AHB matrix interconnect provides a separate bus for each AHB master.

AHB masters include the CPU, General Purpose DMA controller, Ethernet MAC

(LPC1758 only), and the USB interface. This interconnect provides communication

with no arbitration delays.

Split APB bus allows high throughput with few stalls between the CPU and DMA.

Serial interfaces:

On the LPC1758 only, Ethernet MAC with RMII interface and dedicated DMA

controller.

USB 2.0 full-speed device/Host/OTG controller with dedicated DMA controller and

on-chip PHY for device, Host, and OTG functions. The LPC1752/51 include a USB

device controller only.

Four UARTs with fractional baud rate generation, internal FIFO, and DMA support.

One UART has modem control I/O and RS-485/EIA-485 support, and one UART

has IrDA support.

CAN 2.0B controller with two (LPC1759/58/56) or one (LPC1754/52/51) channels.

SPI controller with synchronous, serial, full duplex communication and

programmable data length.

Two SSP controllers with FIFO and multi-protocol capabilities. The SSP interfaces

can be used with the GPDMA controller.

Two I

2

C-bus interfaces supporting fast mode with a data rate of 400 kbit/s with

multiple address recognition and monitor mode.

On the LPC1759/58/56 only, I

2

S (Inter-IC Sound) interface for digital audio input or

output, with fractional rate control. The I

2

S-bus interface can be used with the

GPDMA. The I

2

S-bus interface supports 3-wire and 4-wire data transmit and

receive as well as master clock input/output.

Other peripherals:

52 General Purpose I/O (GPIO) pins with configurable pull-up/down resistors. All

GPIOs support a new, configurable open-drain operating mode. The GPIO block is

accessed through the AHB multilayer bus for fast access and located in memory

such that it supports Cortex-M3 bit banding and use by the General Purpose DMA

Controller.

12-bit Analog-to-Digital Converter (ADC) with input multiplexing among six pins,

conversion rates up to 200 kHz, and multiple result registers. The 12-bit ADC can

be used with the GPDMA controller.

On the LPC1759/58/56/54 only, 10-bit Digital-to-Analog Converter (DAC) with

dedicated conversion timer and DMA support.

Four general purpose timers/counters, with a total of three capture inputs and ten

compare outputs. Each timer block has an external count input. Specific timer

events can be selected to generate DMA requests.

One motor control PWM with support for three-phase motor control.

Quadrature encoder interface that can monitor one external quadrature encoder.

One standard PWM/timer block with external count input.

Real-Time Clock (RTC) with a separate power domain and dedicated RTC

oscillator. The RTC block includes 20 bytes of battery-powered backup registers.

WatchDog Timer (WDT). The WDT can be clocked from the internal RC oscillator,

the RTC oscillator, or the APB clock.

ARM Cortex-M3 system tick timer, including an external clock input option.

LPC1759_58_56_54_52_51 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2010. All rights reserved.

Product data sheet Rev. 6 — 25 August 2010 3 of 73

NXP Semiconductors

LPC1759/58/56/54/52/51

32-bit ARM Cortex-M3 microcontroller

Repetitive Interrupt Timer (RIT) provides programmable and repeating timed

interrupts.

Each peripheral has its own clock divider for further power savings.

Standard JTAG test/debug interface for compatibility with existing tools. Serial Wire

Debug and Serial Wire Trace Port options.

Emulation trace module enables non-intrusive, high-speed real-time tracing of

instruction execution.

Integrated PMU (Power Management Unit) automatically adjusts internal regulators to

minimize power consumption during Sleep, Deep sleep, Power-down, and Deep

power-down modes.

Four reduced power modes: Sleep, Deep-sleep, Power-down, and Deep power-down.

Single 3.3 V power supply (2.4 V to 3.6 V).

One external interrupt input configurable as edge/level sensitive. All pins on Port 0 and

Port 2 can be used as edge sensitive interrupt sources.

Non-maskable Interrupt (NMI) input.

The Wakeup Interrupt Controller (WIC) allows the CPU to automatically wake up from

any priority interrupt that can occur while the clocks are stopped in Deep sleep,

Power-down, and Deep power-down modes.

Processor wake-up from Power-down mode via any interrupt able to operate during

Power-down mode (includes external interrupts, RTC interrupt, USB activity, Ethernet

wake-up interrupt (LPC1758 only), CAN bus activity, Port 0/2 pin interrupt, and NMI).

Brownout detect with separate threshold for interrupt and forced reset.

Power-On Reset (POR).

Crystal oscillator with an operating range of 1 MHz to 25 MHz.

4 MHz internal RC oscillator trimmed to 1 % accuracy that can optionally be used as a

system clock.

PLL allows CPU operation up to the maximum CPU rate without the need for a

high-frequency crystal. May be run from the main oscillator, the internal RC oscillator,

or the RTC oscillator.

USB PLL for added flexibility.

Code Read Protection (CRP) with different security levels.

Unique device serial number for identification purposes.

Available as 80-pin LQFP package (12 mm ×

12 mm × 1.4 mm).

3. Applications

eMetering

Lighting

Industrial networking

Alarm systems

White goods

Motor control

LPC1759_58_56_54_52_51 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2010. All rights reserved.

Product data sheet Rev. 6 — 25 August 2010 4 of 73

NXP Semiconductors

LPC1759/58/56/54/52/51

32-bit ARM Cortex-M3 microcontroller

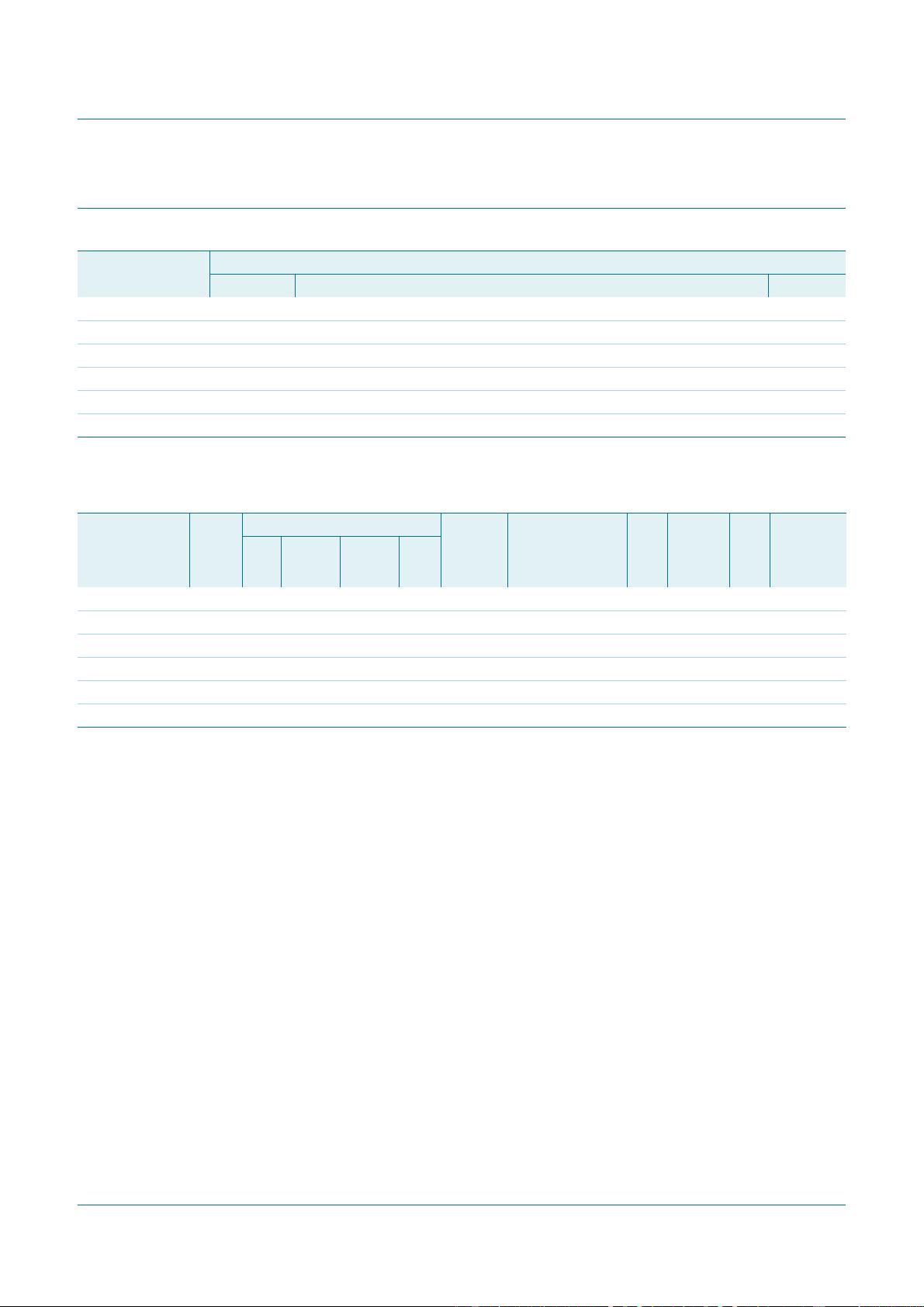

4. Ordering information

4.1 Ordering options

Table 1. Ordering information

Type number Package

Name Description Version

LPC1759FBD80 LQFP80 plastic low-profile quad package; 80 leads; body 12 × 12 × 1.4 mm SOT315-1

LPC1758FBD80 LQFP80 plastic low-profile quad package; 80 leads; body 12 × 12 × 1.4 mm SOT315-1

LPC1756FBD80 LQFP80 plastic low-profile quad package; 80 leads; body 12 × 12 × 1.4 mm SOT315-1

LPC1754FBD80 LQFP80 plastic low-profile quad package; 80 leads; body 12 × 12 × 1.4 mm SOT315-1

LPC1752FBD80 LQFP80 plastic low-profile quad package; 80 leads; body 12 × 12 × 1.4 mm SOT315-1

LPC1751FBD80 LQFP80 plastic low-profile quad package; 80 leads; body 12 × 12 × 1.4 mm SOT315-1

Table 2. Ordering options

Type number Flash SRAM in kB Ethernet USB CAN I

2

S-bus DAC Maximum

CPU

operating

frequency

CPU AHB

SRAM0

AHB

SRAM1

Total

LPC1759FBD80 512 kB 32 16 16 64 no Device/Host/OTG 2 yes yes 120 MHz

LPC1758FBD80 512 kB 32 16 16 64 yes Device/Host/OTG 2 yes yes 100 MHz

LPC1756FBD80 256 kB 16 16 - 32 no Device/Host/OTG 2 yes yes 100 MHz

LPC1754FBD80 128 kB 16 16 - 32 no Device/Host/OTG 1 no yes 100 MHz

LPC1752FBD80 64 kB 16 - - 16 no Device only 1 no no 100 MHz

LPC1751FBD80 32 kB 8 - - 8 no Device only 1 no no 100 MHz

LPC1759_58_56_54_52_51 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2010. All rights reserved.

Product data sheet Rev. 6 — 25 August 2010 5 of 73

NXP Semiconductors

LPC1759/58/56/54/52/51

32-bit ARM Cortex-M3 microcontroller

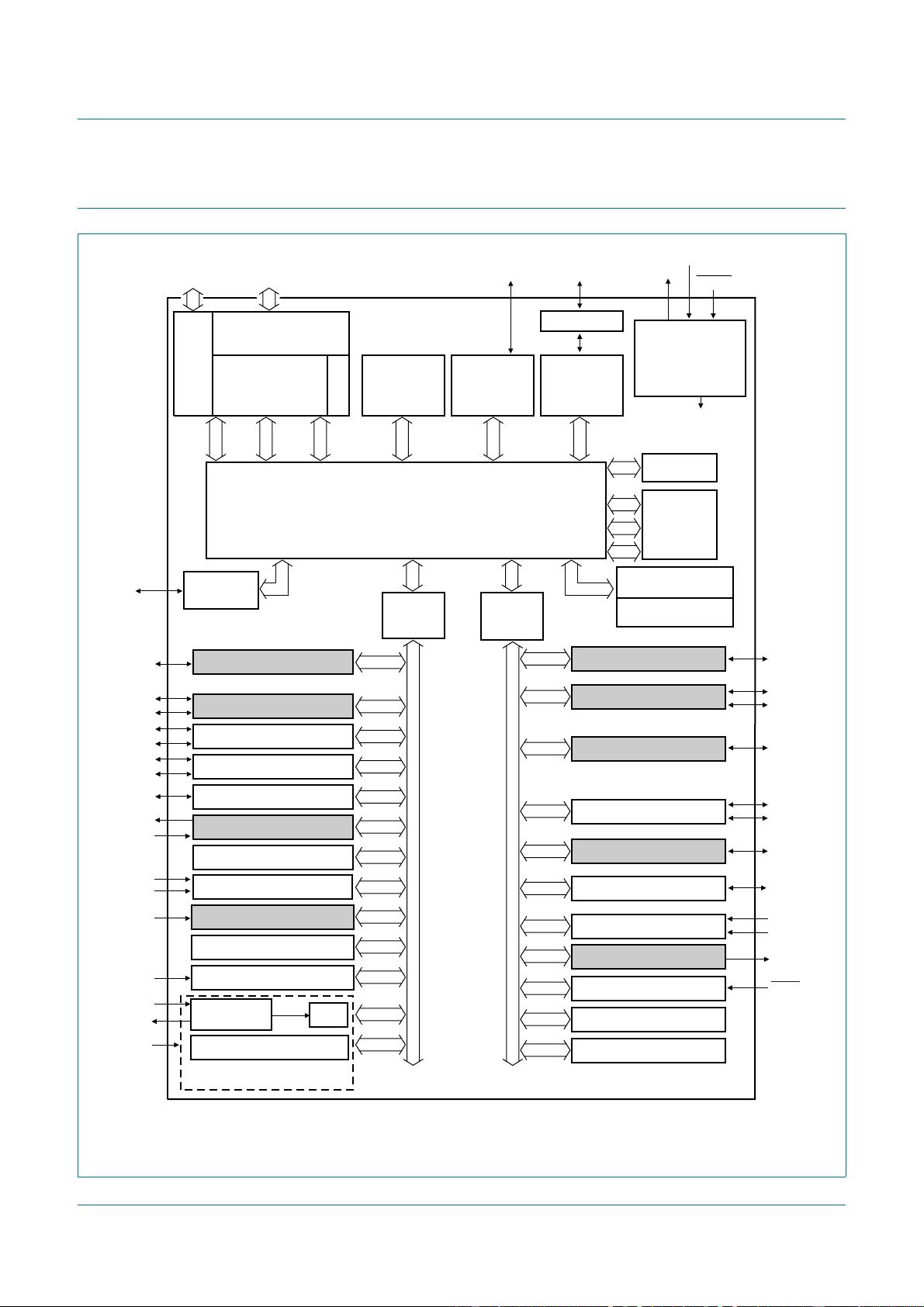

5. Block diagram

Grey-shaded blocks represent peripherals with connection to the GPDMA.

Fig 1. Block diagram

SRAM

64/32/

16/8 kB

ARM

CORTEX-M3

TEST/DEBUG

INTERFACE

EMULATION

TRACE MODULE

FLASH

ACCELERATOR

FLASH

512/256/128/64/32 kB

DMA

CONTROLLER

ETHERNET

CONTROLLER

WITH DMA

(2)

USB HOST/

DEVICE/OTG

CONTROLLER

WITH DMA

(4)

I-code

bus

D-code

bus

system

bus

AHB TO

APB

BRIDGE 0

HIGH-SPEED

GPIO

AHB TO

APB

BRIDGE 1

CLOCK

GENERATION,

POWER CONTROL,

SYSTEM

FUNCTIONS

XTAL1

XTAL2

RESET

clocks and

controls

JTAG

interface

debug

port

USB PHY

SSP0

UART2/3

I2S

(1)

RI TIMER

SYSTEM CONTROL

SSP1

UART0/1

CAN1/CAN2

(1)

I2C1

SPI0

TIMER 0/1

WDT

PWM1

12-bit ADC

PIN CONNECT

GPIO INTERRUPT CONTROL

RTC

BACKUP REGISTERS

32 kHz

OSCILLATOR

APB slave group 1

APB slave group 0

RTC POWER DOMAIN

LPC1759/58/56/54/52/51

master master master

002aae153

slaveslave slave

slave

ROM

slave

slave

MULTILAYER AHB MATRIX

P0, P1,

P2, P4

SCK0

SSEL0

MISO0

MOSI0

SCK1

SSEL1

MISO1

MOSI1

RXD2/3

TXD2/3

SCL2

I2C2

SDA2

MOTOR CONTROL PWM

MCOA[2:0]

MCOB[2:0]

MCI[2:0]

TIMER2/3

4 × MAT2

2 × MAT3

I2SRX_SDA

I2STX_CLK

I2STX_WS

I2STX_SDA

TX_MCLK

RX_MCLK

DAC

(3)

AOUT

QUADRATURE ENCODER

PHA, PHB

INDEX

RTCX1

RTCX2

VBAT

PWM1[6:1]

2 × MAT0/1

1 × CAP0,

2 × CAP1

RD1/2

TD1/2

SDA1

SCL1

AD0[7:2]

SCK/SSEL

MOSI/MISO

8 × UART1

RXD0/TXD0

P0, P2

PCAP1[1:0]

RMII pins

USB pins

MPU

(1)

LPC1759/58/56 only

(2)

LPC1758 only

EXTERNAL INTERRUPTS

EINT0

(3)

LPC1759/58/56/54 only

(4)

LPC1752/51 USB device only

剩余72页未读,继续阅读

资源评论

seanliuqy

- 粉丝: 0

- 资源: 8

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 基于HTML、CSS、JavaScript的easy云盘前端设计源码

- 基于Java、Vue等技术的优加任务管理系统设计源码

- matlab simulink半车主动悬架建模:基于ADRC(自抗扰控制)的主动悬架控制 主体模型为半车主动悬架,采取ADRC控制 输出为车身加速度,悬架动挠度,轮胎动变形 默认输入为正弦路面输

- 基于PHP和Vue的河马跑腿私域配送团队小程序设计源码

- Linux RTL8761b蓝牙驱动 Ubuntu 20.04可用

- 移动磁铁在线圈中产生感应电压分析与仿真 COMSOL 6.0案例还原及 此模型模拟磁铁在线圈中的运动,并计算感应电压,磁铁的位移很明显,因此使用动网格和滑移网格

- 基于TypeScript和JavaScript的核桃健康App设计源码

- 永磁同步电机全阶自适应观测器 自适应全阶观测器MATLAB仿真,高速电机,基础版15.9,改进版49(改进版波形精美,易于出图)下面图为改进版,低速高速都可以,最高5W转每分

- 基于Python生态的第三方库管理器设计源码

- 基于three.js和Vue3的简易智慧城市设计源码

- simulink永磁同步风机风光储VSG一次调频,风机为PMSG,风光储并网系统,频率波形和风机VSG出力如图 网侧VSG同步机控制

- 基于Vue框架的汽修门店SaaS系统设计源码

- 基于Kotlin语言的Android作业设计源码

- mmc分布式储能 恒功率控制 恒电压控制 无缝切

- 基于微信小程序的PowerLib图书馆门户小程序设计源码

- 前端分析-2023071100789

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功