没有合适的资源?快使用搜索试试~ 我知道了~

DSP与FPGA的并行通信-XINTF方案

试读

25页

需积分: 0 9 下载量 96 浏览量

更新于2024-10-29

3

收藏 3.14MB DOCX 举报

DSP与FPGA的并行通信-XINTF方案

DSP 与 FPGA 的并行通信——XINTF 方案

摘要:本文介绍了一种基于 DSP(TMS320F28335)和 FPGA(CycloneII 系列

EP4CE10F17C8)的实验平台构建方法。通过将 DSP 作为主控,FPGA 作为外设,

利用两者各自的优势进行配合。采用普中 DSP28335 开发板作为主核,小梅哥

AC620 开发板作为次核,通过物理杜邦线连接,以外部接口 XINTF 实现并行通

信。该平台实现了 DSP 对 FPGA 的双核通信,利用 FPGA 的 DAC 输出、ADC

回采功能,并通过 CAN 模块与上位机进行通信,完成了数据交互、中断等操作,

最终实现了整体回环的测试实验。

目 录

0 引言 ..............................................................................................................................................1

1 设计思想 ......................................................................................................................................1

2 DSP 与 FPGA 通信程序设计 .......................................................................................................2

2.1 主核时钟软件设置............................................................................................................2

2.1.1 初始化系统控制.....................................................................................................2

2.2 zone0 区域设置 ..................................................................................................................5

2.3 CAN 模块设置 ...................................................................................................................7

2.3.1 CAN 模块的 IO 口配置 ..........................................................................................7

2.3.2 CAN 模块的 CANB 初始化配置 ...........................................................................9

2.3.3 CAN 模块的 CANB 用户功能配置 .....................................................................12

2.3.4 CAN 模块的中断使用 ..........................................................................................15

2.4 次核模块设置..................................................................................................................16

3 实验结果 ....................................................................................................................................20

4 实验难点 ....................................................................................................................................21

4.1 CAN 波特率设置 .............................................................................................................21

4.2 地址线 .............................................................................................................................21

4.3 FPGA 端时序编写 ...........................................................................................................22

1

0 引言

随着数字信号处理技术和可编程逻辑器件的不断发展,DSP 和 FPGA 在众

多领域得到了广泛应用。DSP 具有强大的浮点运算能力,擅长数字信号处理算法

的实现;FPGA 则具有强大的外设驱动能力和灵活性,可根据需求定制各种硬件

逻辑。将两者结合构建实验平台,能够充分发挥各自的优势,实现更复杂的系统

功能。本次主核软件设置利用平台 CCS12.8,次核软件设置利用平台 Quartus II

13.0。

1 设计思想

主核的外部接口 XINTF 实现主核与次核的并行通信,这一系统的硬件连接

示意图如图 1.1 所示,物理图如 1.2 所示,主核将区域 0 的片选信号线 XZCS0、

写操作选通线 XWE0、读操作选通线 XRD、20 位地址总线 XA0~XA19、16 位

双向数据总线 XD0~XD15 等信号线与次核的通用 I/O 口建立起连接。由于整体

是双核通信,通过时钟尤为重要,这里采用了单时钟同步信号的方式,即利用了

主核上的 30MHz 晶振,通过倍频和分频的方式,通过 XCKO 口输出 45MHz 时

钟到次核。

图 1.1 主核与次核硬件连接示意图

图 1.2 主核与次核硬件连接物理示意图

本次实验方案拟定,利用上位机向 CAN 模块发送标准帧格式的数据帧,数

DSP28335

FPGA

CAN 通

信

上位机

A[19:0]

D[15:0]

Clk、WR、CS、RD

AD

DA

30MHz CLK

45MHz CLK

2

据为 0000000000000002,则实现将次核通过 ADC 采样 DAC 的值,再通过并行

通信传到主核,主核再通过 CAN 模块向上位机发送特定的采样值,以判断实验

正确性;如果发送的是其他数据,则是主核往次核写入特定的数据,次核判断特

定数据,以改变 DAC 输出的值。

2 DSP 与 FPGA 通信程序设计

掌握主核时钟设置及外部接口 XINTF 的工作时序是实现主核与次核通信

的基础。

2.1 主核时钟软件设置

由于次核时钟要求是 45MHz,因此主核需要将 30MHz 进行 6 倍频,2 分频

得到 90MHz 的主核工作频率,再将 90MHz 的主频进行 2 分频,得到 45MHz 的

外部接口 XINTF 的工作频率,包括 XCKO 的 45MHz 时钟输出,主要流程图如

图 2.1 所示,以下介绍主核。

图 2.1 45MHz 时钟设置流程图

2.1.1 初始化系统控制

系统控制初始化,在 main 里面调用了 InitSysCtrl()函数。该函数定义在

DSP2833x_SysCtrl.c 文件中,源代码如图 2.2 所示。

图 2.2 InitSysCtrl 函数内部逻辑

这一步通过源代码可以发现总共实现了三个功能。禁止看门狗、设置系统时

钟频率以及对需要外设时钟进行使能。

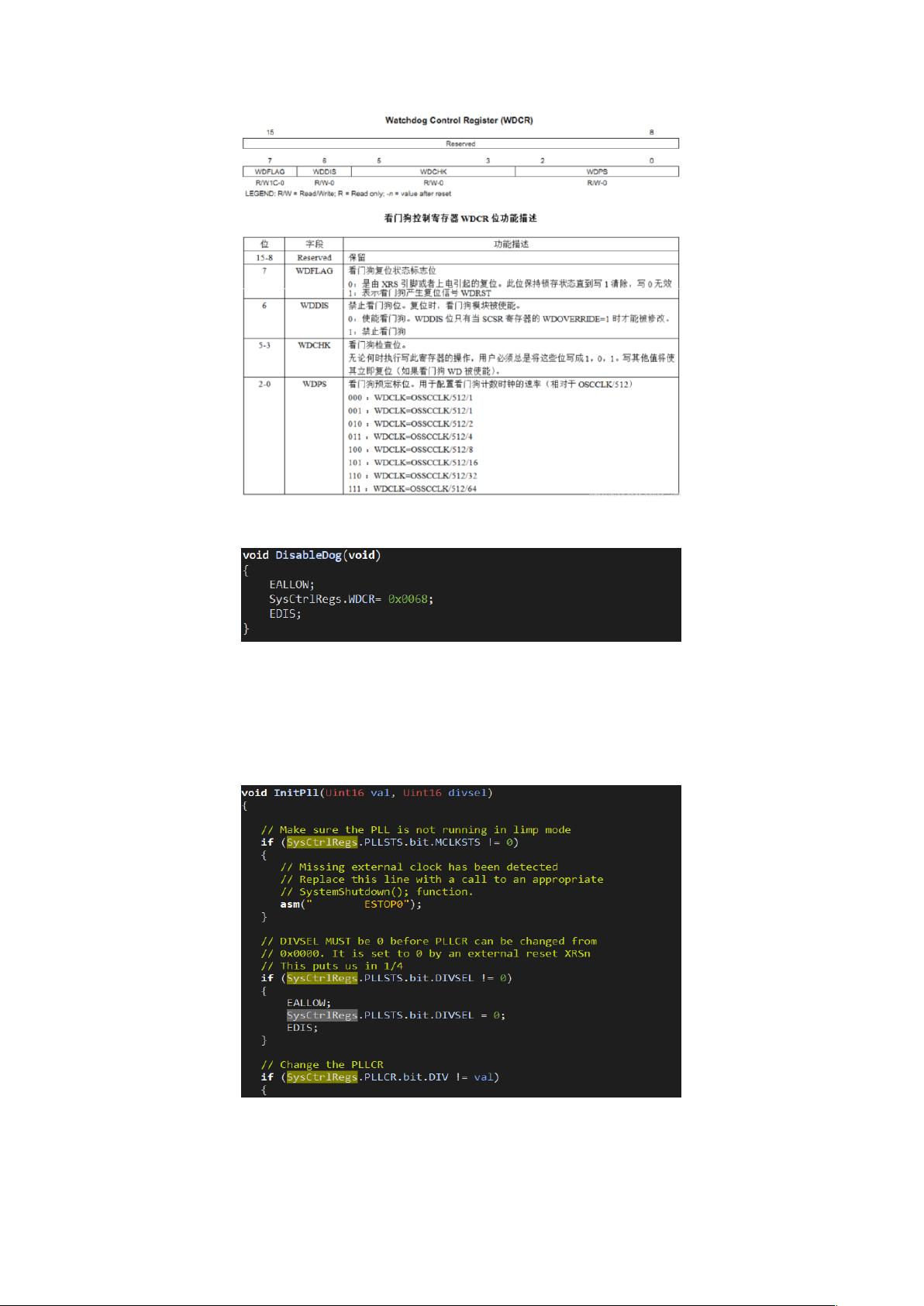

(1)禁止看门狗函数 DisableDog(),该函数内部使用的看门狗控制寄存器

WDCR 的功能如图 2.3 所示,该函数为默认定义,即第四位、第六位和第七位均

为 1。因此只需要按如图 2.4 所示即可。

3

图 2.3 看门狗控制寄存器功能

图 2.4 看门狗函数软件设置

(2)设置系统时钟频率函数 InitPll(),该函数的源程序代码如图 2.5 所示,

需要传入两个参数,一个为 val 值,另一个为 divse 值 l,该参数在头文件

DSP2833x_Examples.h 里面更改,如图 2.6 所示。

图 2.5 InitPll 函数逻辑(部分)

这里对应头文件图 2.2,divsel 为 2,val 为 10,这里 pllcr 就是 val。

剩余24页未读,继续阅读

资源推荐

资源评论

2018-10-08 上传

187 浏览量

2021-05-18 上传

141 浏览量

189 浏览量

2021-07-13 上传

184 浏览量

128 浏览量

2020-08-11 上传

2023-11-20 上传

174 浏览量

110 浏览量

2023-06-24 上传

183 浏览量

108 浏览量

资源评论

九+六

- 粉丝: 16

- 资源: 1

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 基于MATLAB 使用模糊逻辑算法控制给定交叉口的红绿灯系统

- android-19安卓操作系统版本8

- springboot医院病历管理系统--论文-springboot毕业项目,适合计算机毕-设、实训项目、大作业学习.zip

- springboot在线小说阅读平台_0hxfv-springboot毕业项目,适合计算机毕-设、实训项目、大作业学习.zip

- springboot智慧生活分享平台62(源码+sql+论文)-springboot毕业项目,适合计算机毕-设、实训项目、大作业学习.zip

- springboot智能菜谱推荐系统_ct3p7--论文-springboot毕业项目,适合计算机毕-设、实训项目、大作业学习.zip

- 毕业生信息招聘平台-springboot毕业项目,适合计算机毕-设、实训项目、大作业学习.zip

- 大学生创新创业训练项目管理系统设计与实现-springboot毕业项目,适合计算机毕-设、实训项目、大作业学习.zip

- 大健康养老公寓管理系统_to14d-springboot毕业项目,适合计算机毕-设、实训项目、大作业学习.zip

- 复现一篇国内中文核心,改进的DSOGI-PLL锁相环 能够对含有电压直流分量或者是含有高次谐波 都能够锁定电压基波频率50HZ

- 大学新生报到系统的设计与实现-springboot毕业项目,适合计算机毕-设、实训项目、大作业学习.zip

- 大学生社团活动平台-springboot毕业项目,适合计算机毕-设、实训项目、大作业学习.zip

- 儿童性教育网站-springboot毕业项目,适合计算机毕-设、实训项目、大作业学习.zip

- 点餐平台网站-springboot毕业项目,适合计算机毕-设、实训项目、大作业学习.zip

- 个性化电影推荐系统-springboot毕业项目,适合计算机毕-设、实训项目、大作业学习.zip

- 高校学生饮食推荐系统_02187-springboot毕业项目,适合计算机毕-设、实训项目、大作业学习.zip

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功