没有合适的资源?快使用搜索试试~ 我知道了~

资源推荐

资源详情

资源评论

Application Report

ZHCA530 – April 2013

1

LDO

环路稳定性及其对射频频综相噪的影响

李俊明, 龙云

摘 要

相位噪声是时钟、射频频综最为关注的技术指标之一。影响锁相环相噪的因素有很多,比

如电源、参考源相噪、VCO 自身的相噪、环路滤波器的设置等。其中,电源引入的低频噪

声往往对锁相环的近端相噪有着很大的影响。对于高性能的时钟和射频频综产品,为了获

得极低的相噪性能,往往采用低噪声的 LDO 供电。然而,采用不同的 LDO 给频综供电,

取得的相噪性能往往会有很大差别,同时,LDO 外围电路设计也会影响到频综的相噪性能。

本文首先简要地介绍了 LDO 的噪声来源及环路稳定性对输出噪声的影响;其次,根据调频

理论推导出 VCO 的相位噪声与 LDO 的噪声频谱密度的理论计算关系。在此基础上,为了

验证 LDO 噪声对射频频综输出相噪的影响,分别采用 TPS7A8101 和 TPS74401 LDO 评

估板给 TRF3765 射频频综评估板供电,对比测试这两种情况下的 TRF3765 相噪曲线;同

时,为了验证 LDO 环路稳定性对频综相噪的影响,针对 TPS7A8101 评估板的参考电路做

出部分修改,并对比测试了电路修改前后的 TRF3765 输出相噪。

目录

1 LDO 噪声来源及环路稳定性对输出噪声影响 ......................................................................................... 2

1.1 LDO 噪声来源 ........................................................................................................................... 2

1.2 LDO 噪声抑制方法 .................................................................................................................... 3

1.3 LDO 环路稳定性与输出噪声的关系 ........................................................................................... 4

2 LDO 噪声与 VCO 输出相噪的关系 .................................................................................................... 5

3 采用不同 LDO 进行射频频综供电对比测试 ........................................................................................ 6

3.1 TPS7A8101/TPS74401 频综供电对比测试 ............................................................................... 6

3.2 TPS7A8101 输出电路优化及其对频综相噪的影响 ..................................................................... 8

4 结论 .................................................................................................................................................. 10

5 参考文献 ........................................................................................................................................... 10

图表

图 1 LDO 的 PSRR 与噪声 ..................................................................................................................... 2

图 2 LDO 内部框图(噪声源) ............................................................................................................... 3

图 3 LDO 内部框图(增加噪声抑制电容和前馈电容) ........................................................................... 3

图 4 不同

FF

C

下的噪声频谱密度图 .......................................................................................................... 4

图 5 LDO 小信号模型 ............................................................................................................................. 4

图 6 增加前馈电容后的频率响应波特图 .................................................................................................. 5

图 7 由电源噪声引入的 VCO 相噪恶化 ................................................................................................... 5

图 8 TPS7A8101 与 TPS74401 噪声频谱密度图 .................................................................................... 7

图 9 LDO 频综供电对比测试设置 ........................................................................................................... 7

ZHCA530

2 LDO

环路稳定性及其对射频频综相噪的影响

图 10 采用 TPS7A8101/TPS74401 供电的 TRF3765 相噪曲线 .............................................................. 8

图 11 TPS7A8101 评估板初始原理图 ..................................................................................................... 8

图 12 TPS7A8101 提高环路稳定性后的原理图 ...................................................................................... 9

图 13 TPS7A8101 稳定性改善前后 TRF3765 相噪曲线.......................................................................... 9

表格

表 1 不同 LDO 给频综供电对比测试结果 .............................................................................................. 10

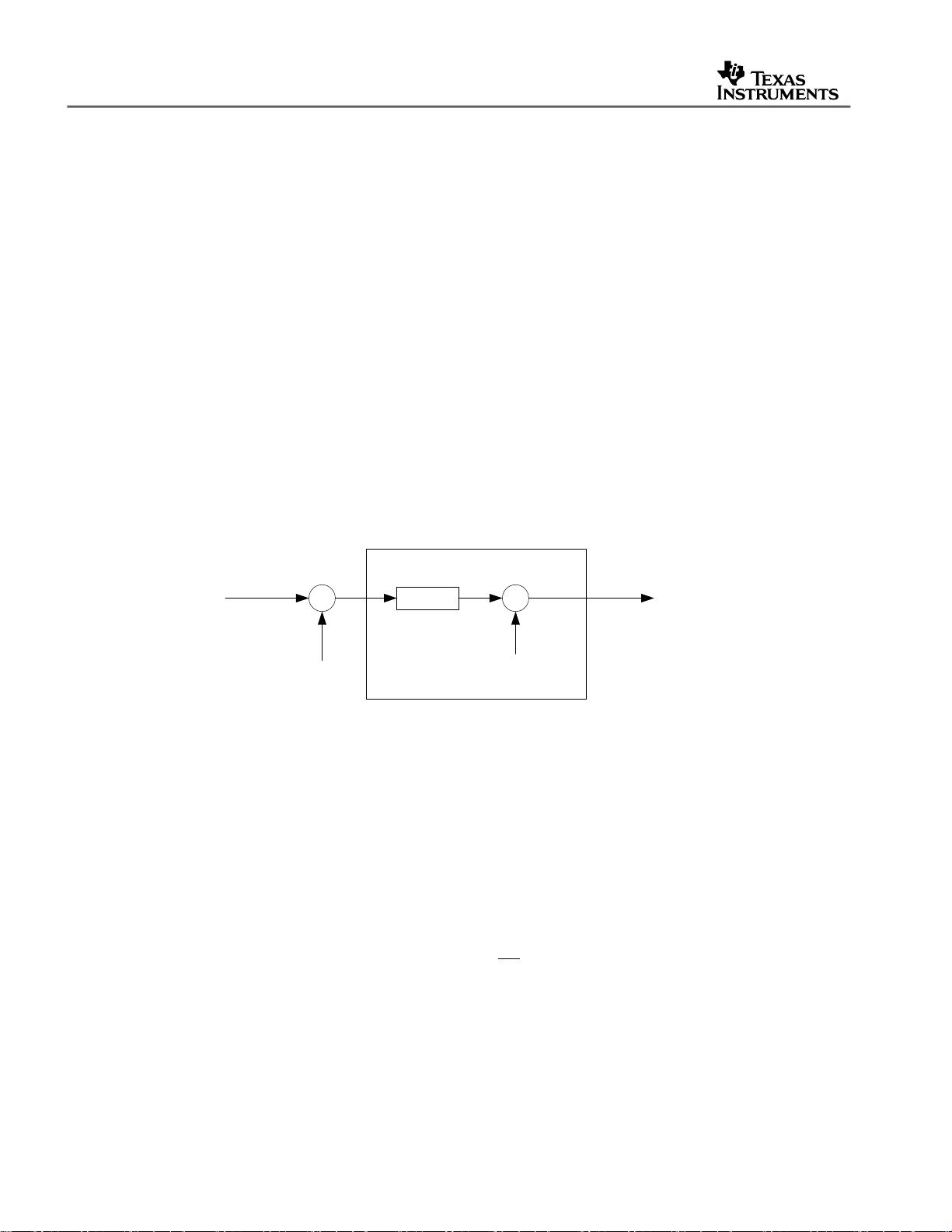

1 LDO 噪声来源及环路稳定性对输出噪声影响

1.1 LDO 噪声来源

LDO 的噪声分为 LDO 内部的噪声和 LDO 外部的噪声。LDO 内部的噪声来自于内部电路的带隙基

准源,放大器以及晶体管。LDO 外部的噪声来自于输入。在 LDO 的手册中,PSRR 是表征 LDO

抑制外部噪声的能力,但 PSRR 高并不代表 LDO 内部噪声小。LDO 的总输出噪声才是表征 LDO

内部噪声抑制的参数,一般在电气特性表里用单位

RMS

V

µ

表示,或者在噪声频谱密度图上表示。

PSRR

Ʃ

Ʃ

DC

External

Noise

Internal

Noise

LDO

DC+

Noise

图 1 LDO 的 PSRR 与噪声

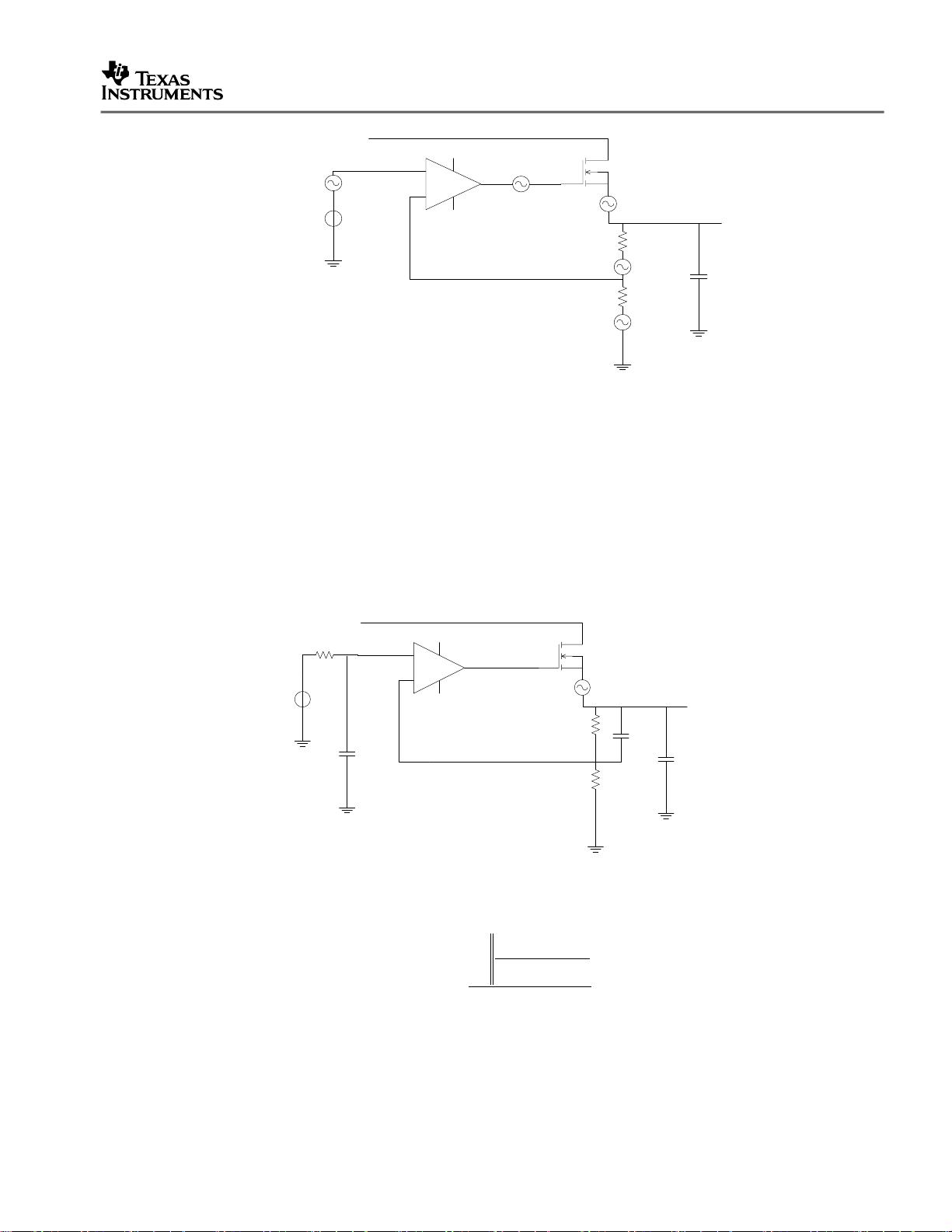

图 2 是 LDO 内部结构框图,

N

V

代表等效噪声源。噪声源包括带隙基准源产生的噪声

()N REF

V

,误

差放大器产生的噪声

()N AMP

V

,FET 产生的噪声

()N FET

V

以及反馈电阻产生的噪声

( 1)NR

V

和

( 2)NR

V

。

在大多数情况下,由于带隙基准源电路是由很多不同的电阻、晶体管和电容组成,它所产生的噪

声会远远大于反馈电阻产生的噪声。而且带隙基准源是误差放大器的输入,它所产生的噪声也会

经由误差放大器放大来控制 FET,所以误差放大器本身以及 FET 所产生的噪声也会比带隙基准源

的噪声要低。可以说,LDO 内部最大的噪声源就是带隙基准源。我们把 LDO 输出噪声

()N OUT

V

表

示为

1

( ) ( ) ()

2

1

N OUT N Other N REF

R

VV V

R

= ++ ×

(1)

()N Other

V

是

()N AMP

V

以及

()N FET

V

的和。由公式 1 可以得出,输出噪声最小值出现在 R1 短接到 FB,

误差放大器的增益近似为 1 的时候。

ZHCA530

LDO

环路稳定性及其对射频频综相噪的影响

3

Error Amp

2

R

1

R

( 1)

NR

V

( 2)NR

V

REF

V

()N REF

V

IN

V

()

N AMP

V

()N FET

V

NFET

OUT

C

OUT

V

+

+

−

−

FB

V

图 2 LDO 内部框图(噪声源)

1.2 LDO 噪声抑制方法

为了抑制带隙基准源产生的噪声,有三种办法。

一是降低误差放大器的带宽,抑制了带隙基准源的高频噪声。但是降低带宽会使 LDO 的动态性能

降低。

二是在带隙基准源和误差放大器之间加低通滤波。高性能的 LDO 都会有一个噪声抑制 NR 管脚,

NR

C

并联在带隙基准源和 GND 之间,起到低通滤波的作用。如图 3 所示。

Error Amp

2

R

1

R

REF

V

IN

V

()N OUT

V

NFET

OUT

C

OUT

V

+

+

−

−

FB

V

FF

C

NR

C

图 3 LDO 内部框图(增加噪声抑制电容和前馈电容)

三是在反馈电阻 R1 上增加前馈电容

FF

C

。在增加了

FF

C

和

NR

C

后,输出噪声可以表示为

1

( ) ( ) ()

2

1

2

1

FF

N OUT N Other RC N REF

R

fC

V V GV

R

π

××

= ++ × ×

(2)

从式 2 可以得出,

FF

C

越大,输出噪声就越小。频率越高,输出噪声越小。

剩余10页未读,继续阅读

资源评论

付浮悠

- 粉丝: 6

- 资源: 1

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- Java程序设计课件,个人学习整理,仅供参考

- python tkinter库学生管理系统,带sqlite3数据库版.zip

- 一个用python写的库存管理系统,GUI使用tkinter库,数据库管理使用pymysql.zip

- 蘑菇是否有毒图像识别数据

- 最终结果-数字底层技术转型与数字场景应用转型.xlsx

- 基于 Python tkinter 与 MySQL的图书管理系统.zip

- health check-in system.zip

- 微信公众号python爬虫程序

- 基于jsp的网上购物论文

- 基于非对称纳什谈判的多微网电能共享运行优化策略 关键词:纳什谈判 合作博弈 微网 电转气-碳捕集 P2P电能交易交易 参考文档:《基于非对称纳什谈判的多微网电能共享运行优化策略》完美复现

- RISCV处理器架构的官方参考学习资料.zip

- Labview自动贩卖机

- 基于LabVIEW的计算器

- 地市新型数字基础设施水平数据集(2003-2024年).txt

- 信捷PLC XD5做的一个STC四轴机械手程序,是一个冲床上下料四轴程序,,两种冲压控制方式,使用绝对式伺服,MODBUS通讯 程序功能非常完善,有伺服状态监控,故障,连线检测,通讯检测等,程序已经

- MATLAB-simulink主动均衡电路模型#汽车级锂电池 动力锂电池模组(16节电芯) 主动均衡电路:Buck-boost...

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功