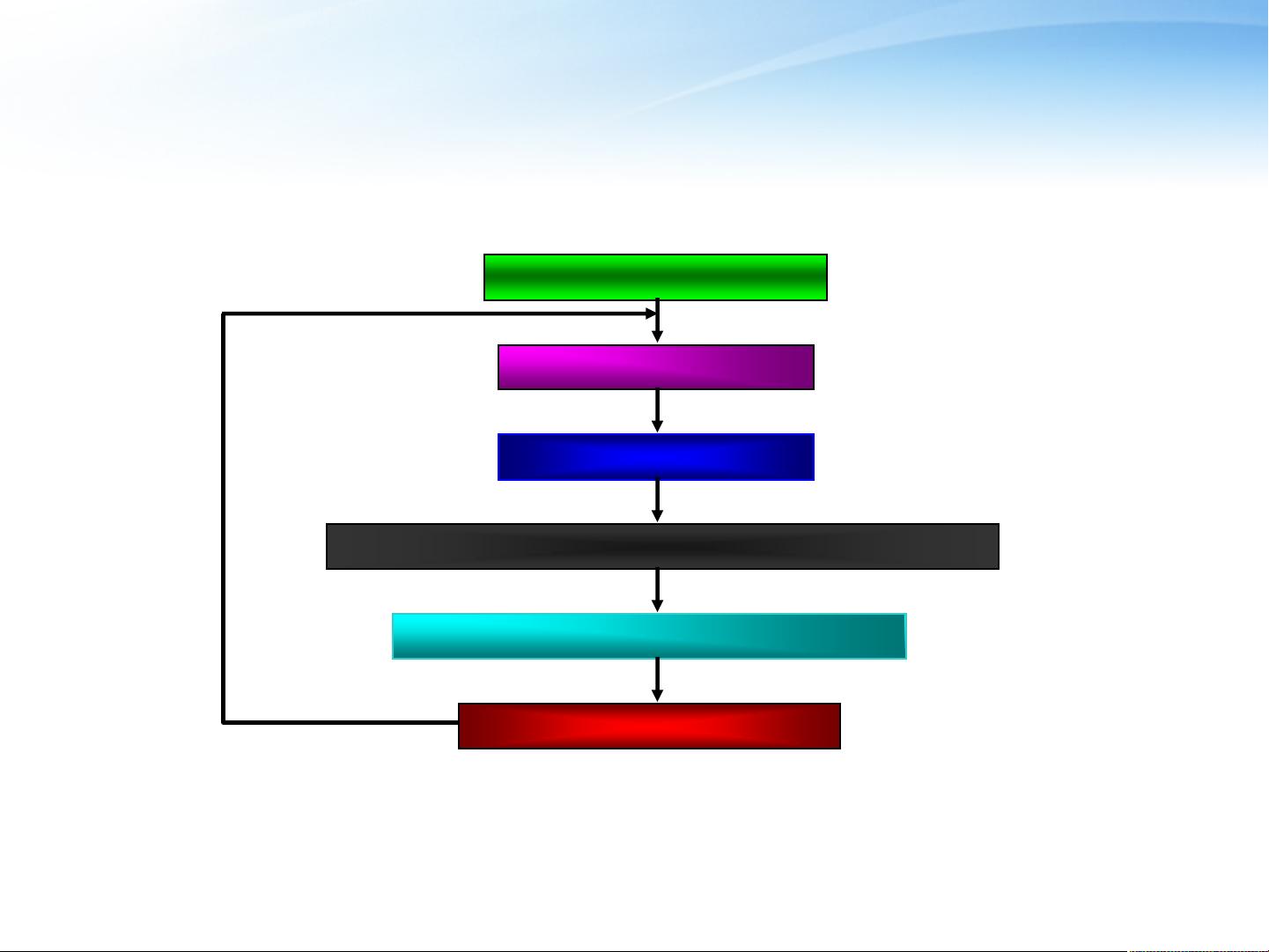

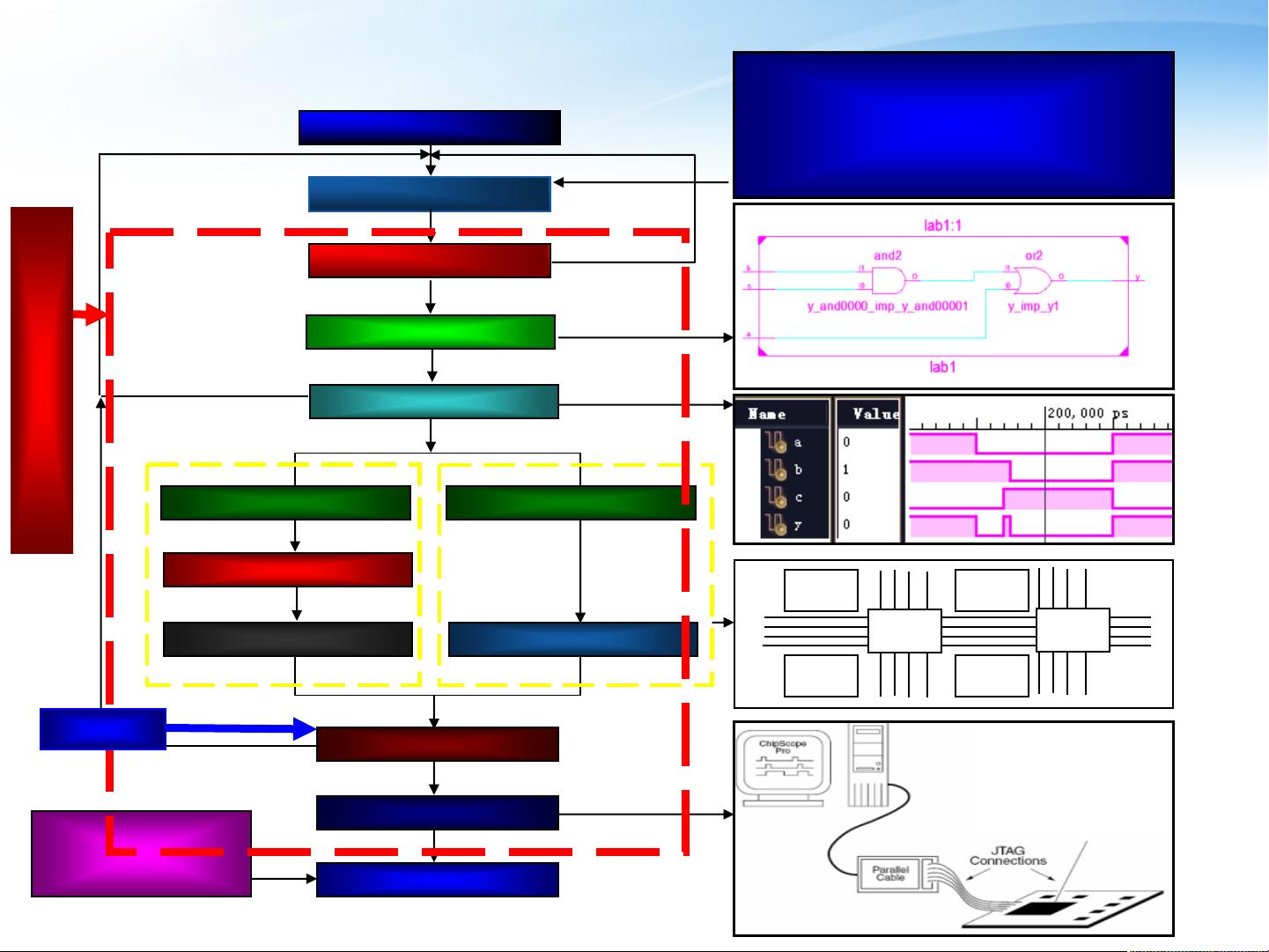

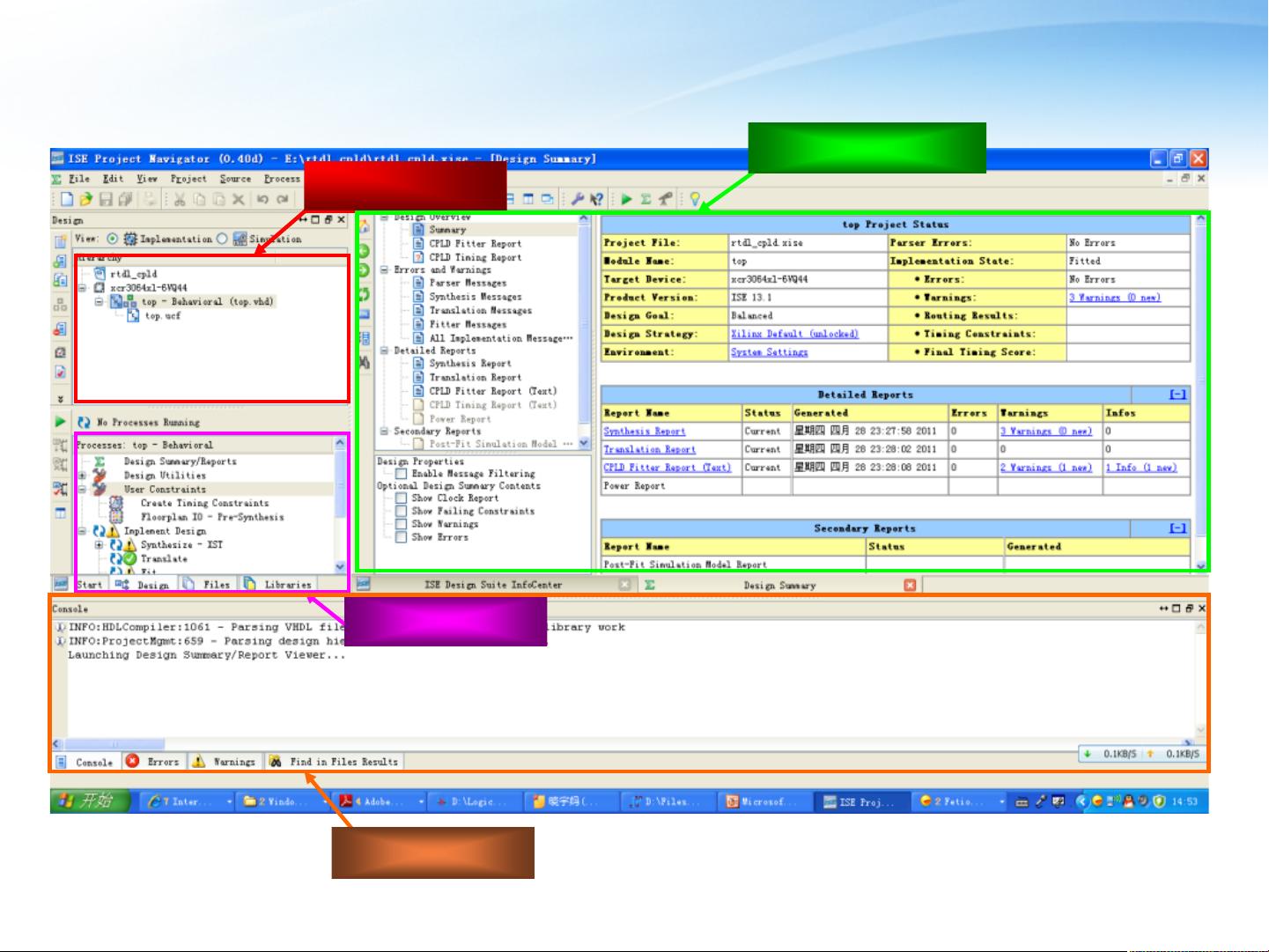

【ISE14.7教程详解】 ISE(Integrated Software Environment),是Xilinx公司推出的一款用于FPGA和CPLD设计的集成开发环境。本教程旨在帮助初学者掌握ISE14.7的使用,以实现现代数字系统设计流程。 在传统的数字系统设计中,设计者需要手动完成从真值表到卡诺图简化,再到电路实现的全过程。然而,现代数字系统设计流程已大大自动化,借助ISE这样的工具,设计师可以高效地进行设计输入、功能级仿真、逻辑综合、时序仿真、系统调试与验证。 在ISE14.7中,设计流程大致分为以下几个步骤: 1. **设计输入**:我们需要定义设计的实体。例如,以下是一个简单的VHDL代码段,展示了如何定义一个名为lab1的实体,它有三个输入a、b、c和一个输出y: ``` entity lab1 is port(a, b, c : in std_logic; y : out std_logic); end lab1; architecture rtl of lab1 is begin y<=a or (c and b); end rtl; ``` 2. **逻辑综合**:编写好VHDL代码后,使用ISE进行逻辑综合,将高级语言描述转化为逻辑门级表示。在这个例子中,`y<=a or (c and b);`会被转换为一系列AND、OR门。 3. **时序仿真**:在综合之前,可以先进行功能级仿真,确保设计逻辑正确。综合完成后,进行时序仿真,考虑时序影响,验证设计是否满足性能要求。 4. **适配与布局布线**:综合后的设计经过适配过程,适应选定的FPGA或CPLD的资源。接着,布局布线(PAR)将逻辑门分配到物理位置,并连接它们,以优化速度和资源利用率。 5. **设计实现与下载**:最终,生成配置文件,加载到FPGA或CPLD中。通过示波器、逻辑分析仪等硬件设备,以及软件程序进行实际运行和调试,确保设计按预期工作。 在ISE13.1版本中,我们还可以了解到如何启动软件、新建工程、设置工程参数,如产品类别、芯片型号、封装类型等。此外,设计流程还包括创建新的设计文件,选择VHDL模块,添加代码,以及进行库调用、端口声明和内部信号声明等。 通过这个教程,学习者将能够掌握基于VHDL的ISE设计流程,包括创建工程、编写VHDL代码、综合、仿真、实现和下载到硬件。通过实践,设计师可以逐步理解并掌握现代数字系统设计的自动化工具,从而提高设计效率和准确性。

剩余82页未读,继续阅读

- 粉丝: 0

- 资源: 2

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

信息提交成功

信息提交成功