没有合适的资源?快使用搜索试试~ 我知道了~

DP83867IR 千兆位以太网 PHY 收发器. 数据表

需积分: 1 2 下载量 73 浏览量

2023-07-18

16:35:45

上传

评论

收藏 3.75MB PDF 举报

温馨提示

试读

143页

DP83867IR 千兆位以太网 PHY 收发器. 数据手册 Ultra low RGMII latency TX < 90ns, RX < 290ns Time Sensitive Network (TSN) compliant Low power consumption 457 mW Exceeds 8000 V IEC 61000-4-2 ESD protection Meets EN55011 class B emission standards 16 programmable RGMII delay modes on RX/TX Integrated MDI termination resistors Programmable MII/GMII/RGMII termination impedance WoL (Wake-on-LAN) packet detection 25-MHz or 125-MHz synchronized clock output Start of Frame Detect for IEEE 1588 time stamp RJ45 mirror mo

资源推荐

资源详情

资源评论

DP83867IR/CR Robust, High Immunity 10/100/1000 Ethernet Physical Layer

Transceiver

1 Features

• Ultra low RGMII latency TX < 90ns, RX < 290ns

• Time Sensitive Network (TSN) compliant

• Low power consumption 457 mW

• Exceeds 8000 V IEC 61000-4-2 ESD protection

• Meets EN55011 class B emission standards

• 16 programmable RGMII delay modes on RX/TX

• Integrated MDI termination resistors

• Programmable MII/GMII/RGMII termination

impedance

• WoL (Wake-on-LAN) packet detection

• 25-MHz or 125-MHz synchronized clock output

• Start of Frame Detect for IEEE 1588 time stamp

• RJ45 mirror mode

• Fully compatible to IEEE 802.3 10BASE-Te,

100BASE-TX, and 1000BASE-T Specification

• Cable diagnostics

• MII, GMII and RGMII MAC interface options

• Configurable I/O voltage (3.3 V, 2.5 V, 1.8 V)

• Fast link drop mode

• JTAG support

2 Applications

• Motor drives

• Industrial factory automation

• Field Bus Support

• Industrial embedded computing

• Wired and wireless communications infrastructure

• Test and measurement

• Consumer electronics

3 Description

The DP83867 device is a robust, low power, fully

featured Physical Layer transceiver with integrated

PMD sublayers to support 10BASE-Te, 100BASE-TX

and 1000BASE-T Ethernet protocols. Optimized for

ESD protection, the DP83867 exceeds 8-kV IEC

61000-4-2 (direct contact).

The DP83867 is designed for easy implementation

of 10/100/1000 Mbps Ethernet LANs. It interfaces

directly to twisted pair media via an external

transformer. This device interfaces directly to the

MAC layer through the IEEE 802.3 Standard Media

Independent Interface (MII), the IEEE 802.3 Gigabit

Media Independent Interface (GMII) or Reduced GMII

(RGMII). The QFP package supports MII/GMII/RGMII

whereas the QFN package supports RGMII.

The DP83867 provides precision clock

synchronization, including a synchronous Ethernet

clock output. It has low latency and provides IEEE

1588 Start of Frame Detection.

The DP83867 consumes only 490mW (PAP) and 457

mW (RGZ) under full operating power. Wake on LAN

can be used to lower system power consumption.

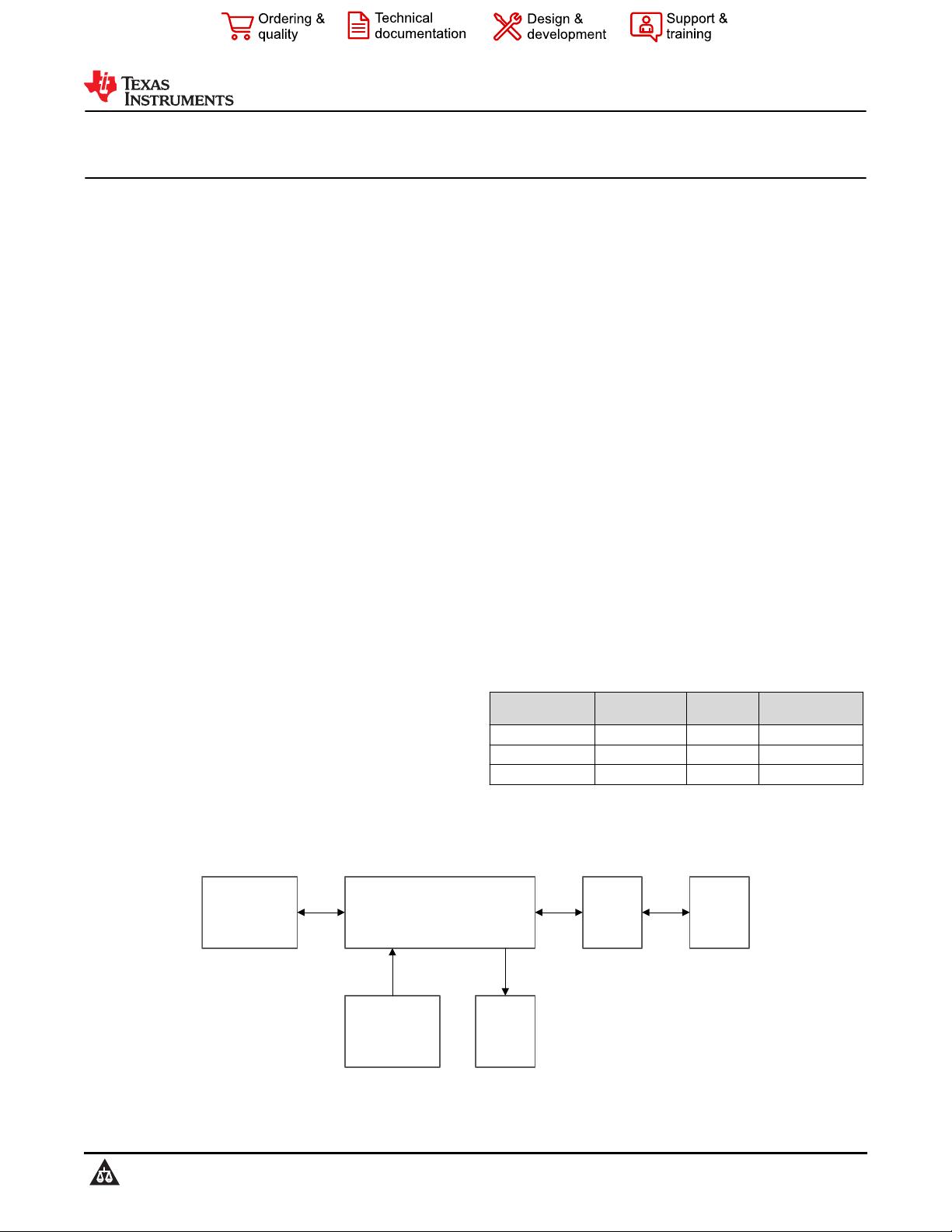

Device Information

PART NUMBER TEMPERATURE

PACKAGE

(1)

BODY SIZE (NOM)

DP83867IRPAP –40°C to +85°C QFP (64) 10 mm x 10 mm

DP83867IRRGZ –40°C to +85°C QFN (48) 7 mm x 7 mm

DP83867CRRGZ 0°C to +70°C QFN (48) 7 mm x 7 mm

(1) For all available packages, see the orderable addendum at

the end of the data sheet.

DP83867

10/100/1000 Mbps

Ethernet Physical Layer

Ethernet MAC Magnetics RJ-45

Status

LEDs

25 MHz

Crystal or Oscillator

MII (PAP)

GMII (PAP)

RGMII (PAP, RGZ)

10BASE-Te

100BASE-TX

1000BASE-T

DP83867IR, DP83867CR

SNLS484G – FEBRUARY 2015 – REVISED OCTOBER 2022

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications,

intellectual property matters and other important disclaimers. PRODUCTION DATA.

Table of Contents

1 Features............................................................................1

2 Applications..................................................................... 1

3 Description.......................................................................1

4 Revision History.............................................................. 2

5 Device Comparison......................................................... 8

6 Pin Configuration and Functions...................................8

6.1 Unused Pins .............................................................14

7 Specifications................................................................ 15

7.1 Absolute Maximum Ratings...................................... 15

7.2 ESD Ratings............................................................. 15

7.3 Recommended Operating Conditions.......................15

7.4 Thermal Information..................................................16

7.5 Electrical Characteristics...........................................16

7.6 Power-Up Timing...................................................... 18

7.7 Reset Timing.............................................................19

7.8 MII Serial Management Timing................................. 19

7.9 RGMII Timing............................................................19

7.10 GMII Transmit Timing

(2)

......................................... 20

7.11 GMII Receive Timing

(2)

.......................................... 20

7.12 100-Mbps MII Transmit Timing

(1)

........................... 20

7.13 100-Mbps MII Receive Timing

(2)

............................ 20

7.14 10-Mbps MII Transmit Timing

(2)

............................. 21

7.15 10-Mbps MII Receive Timing

(2)

.............................. 21

7.16 DP83867IR/CR Start of Frame Detection Timing... 21

7.17 Timing Diagrams ....................................................25

7.18 Typical Characteristics............................................ 30

8 Detailed Description......................................................31

8.1 Overview................................................................... 31

8.2 Functional Block Diagram......................................... 32

8.3 Feature Description...................................................34

8.4 Device Functional Modes..........................................37

8.5 Programming............................................................ 51

8.6 Register Maps...........................................................59

9 Application and Implementation................................ 118

9.1 Application Information............................................118

9.2 Typical Application.................................................. 118

10 Power Supply Recommendations............................125

11 Layout......................................................................... 128

11.1 Layout Guidelines................................................. 128

11.2 Layout Example.................................................... 130

12 Device and Documentation Support........................131

12.1 Documentation Support........................................ 131

12.2 Related Links........................................................ 131

12.3 Receiving Notification of Documentation Updates131

12.4 Support Resources............................................... 131

12.5 Electrostatic Discharge Caution............................131

12.6 Glossary................................................................131

12.7 Trademarks...........................................................131

4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

Changes from Revision F (October 2019) to Revision G (August 2022) Page

• Updated Start of Frame Detect for IEEE 1588 time stamp.................................................................................1

• Added following wording to the end of first paragraph in Section 8.4.3.9 "DP83867 devices manufactured

after August, 2022, have an increased random seed value that now includes 255 different seed values to

expedite Auto-MDIX resolution with a link partner."..........................................................................................46

• Removed Reg 0x01D5 Programmable Gain Register (PROG_GAIN)............................................................. 59

• Changed Bit 11:10 SPEED_OPT_ATTEMPT_CNT to RW description in ........................................................79

• Changed bits 15:9, so that bit 12 can be '1'. Bit 7 description updated Section 8.6.31 ................................... 90

• Added Register 0x008A....................................................................................................................................96

• Added Register 0x00B3....................................................................................................................................97

• Added Register 0x00C0....................................................................................................................................97

• Added Register 0x0100.................................................................................................................................... 98

Changes from Revision E (March 2017) to Revision F (October 2019) Page

• Added "Time Sensitive Network (TSN) Compliant" to Section 1 ....................................................................... 1

• Changed "Fast Link up / Link Drop Modes" to "Fast Link Drop Mode" in Section 1 .......................................... 1

• Added "Field Bus Support" to Section 2 ............................................................................................................ 1

• Changed 'TX_EN / TX_CTRL' pin type in Pin Functions.................................................................................. 10

• Deleted "NOTE: Internal Pull-Up/Pull-Down resistors on the IO pins are disabled when the device enters

functional mode after power up." from Pin Functions....................................................................................... 10

• Added XI pin voltage ratings to Section 7.1 .....................................................................................................15

• Added XI Input Voltage section to Section 7.5 .................................................................................................16

• Changed links to RGMII timing diagrams in Section 7.9 ................................................................................. 19

• Changed T

holdR

parameter description in Section 7.9 ..................................................................................... 19

• Added table note explaining how Duty Cycle % must be interpreted in Section 7.9 ....................................... 19

DP83867IR, DP83867CR

SNLS484G – FEBRUARY 2015 – REVISED OCTOBER 2022

www.ti.com

2 Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

Product Folder Links: DP83867IR DP83867CR

• Added table note explaining how Duty Cycle % must be interpreted in Section 7.9 ....................................... 19

• Changed Figure 7-10 .......................................................................................................................................21

• Changed statement about PHY address in Section 8.4.2 ............................................................................... 41

• Added Figure 8-11 ........................................................................................................................................... 46

• Deleted "The BIST allows full control of the packet lengths and of the IPG." from Section 8.4.5 ....................48

• Deleted mention of ALCD from Section 8.4.6 ..................................................................................................48

• Deleted subsection describing ALCD from Section 8.4.6 ................................................................................ 48

• Added sentence about the polarity of MDI signals in Section 8.4.6.5 ..............................................................49

• Changed 'CRS' strap function from "Fast Link Detect" to "Fast Link Drop" in Table 8-4 ................................. 51

• Changed notes after Table 8-4 to be table notes referenced within the table. .................................................51

• Added definition for register Bit Name type 'Strap' in Section 8.6 ................................................................... 59

• Deleted Advanced Link Cable Diagnostics Control Register (ALCD_CTRL) .................................................. 59

• Added PAP package default for '1000BASE-T FULL DUPLEX' in Section 8.6.10 ...........................................69

• Changed 'MDI_CROSSOVER' default in Section 8.6.14 .................................................................................72

• Added PAP package default for 'SPEED_OPT_EN' in Section 8.6.18 ............................................................ 79

• Added Section 8.6.28 ...................................................................................................................................... 88

• Changed descriptions of 'FORCE_DROP' and 'FLD_EN' in Section 8.6.29 ....................................................89

• Added Section 8.6.30 ...................................................................................................................................... 90

• Added 'INT_TST_MODE_1' to Section 8.6.31 .................................................................................................90

• Changed 'PORT_MIRROR_EN' default in Section 8.6.31 ...............................................................................90

• Added PAP package default for 'RGMII_EN' in Section 8.6.32 ....................................................................... 90

• Added Section 8.6.35 ...................................................................................................................................... 93

• Changed description of 'STRAP_FLD' from "Fast Link Detect" to "Fast Link Drop" in Section 8.6.38 ............ 95

• Added Section 8.6.41 ...................................................................................................................................... 96

• Added Section 8.6.42 ...................................................................................................................................... 96

• Added RGZ package default for 'RGMII_TX_DELAY_CTRL' in Section 8.6.44 .............................................. 97

• Added RGZ package default for 'RGMII_RX_DELAY_CTRL' in Section 8.6.44 ..............................................97

• Added Section 8.6.47 ...................................................................................................................................... 97

• Added Section 8.6.51 ...................................................................................................................................... 98

• Changed capacitor value in Figure 9-2 and added footnotes......................................................................... 119

• Added requirements for 2.5-V clock source capacitors in Section 9.2.1.2 .................................................... 121

• Added Figure 9-4 ........................................................................................................................................... 121

• Added "RMS Jitter" to Table 9-2 .................................................................................................................... 121

• Added Section 9.2.1.4 ................................................................................................................................... 123

• Changed capacitor placement in Figure 10-1 and footnote about decoupling capacitor placement.............. 125

• Changed capacitor placement in Figure 10-2 and footnote about decoupling capacitor placement.............. 125

Changes from Revision C (November 2015) to Revision D (July 2016) Page

• Added '(Straps Required)' to RX_DV/RX_CTRL pin in Pin Functions table..................................................... 10

• Changed '1nF' to '1µF' for VDD1P1 and VDD1P0 pin in Pin Functions table...................................................10

• Added Operating Junction Temperature to Section 7.3 ................................................................................... 15

• Changed parameter symbol from VIH to V

IH

in Section 7.5 ............................................................................ 16

• Added MDC toggling clarification to Section 7.7 ..............................................................................................19

• Changed target strap voltage thresholds in Table 8-3 ..................................................................................... 51

• Changed 'SPEED_SEL1' to 'ANEG_SEL1' in Table 8-4 ..................................................................................51

• Added '(Straps Required)' to RX_DV/RX_CTRL in Table 8-4 ..........................................................................51

• Changed 'SPEED_SEL0' to 'ANEG_SEL' in Table 8-4 ....................................................................................51

• Changed 'SPEED_SEL0' to 'ANEG_SEL0' in Table 8-4 ..................................................................................51

• Changed table name from 'PAP Speed Select Strap Details' to Table 8-5 ...................................................... 51

• Changed 'SPEED_SEL0' and 'SPEED_SEL' to 'ANEG_SEL0' and 'ANEG_SEL1' in Table 8-5 ..................... 51

• Changed table name from 'RGZ Speed Select Strap Details' to Table 8-6 ..................................................... 51

• Changed 'SPEED_SEL' to 'ANEG_SEL' in Table 8-6 ......................................................................................51

• Changed Default state of from 'Strap' to '0' for bit 13 in Table 8-9 ...................................................................59

• Changed Default state of from 'Strap' to '1' for bit 6 in Table 8-9 .....................................................................59

• Changed bit 9 name from 100BASE-T FULL DUPLEX to 1000BASE-T FULL DUPLEX in Table 8-18 .......... 69

www.ti.com

DP83867IR, DP83867CR

SNLS484G – FEBRUARY 2015 – REVISED OCTOBER 2022

Copyright © 2022 Texas Instruments Incorporated

Submit Document Feedback

3

Product Folder Links: DP83867IR DP83867CR

• Changed bit 9 descriptions from half duplex to full duplex in Table 8-18 .........................................................69

• Changed 'Interrupt Status and Event Control Register (ISR)' to 'MII Interrupt Control Register (MICR)' in

Section 8.6.16 ..................................................................................................................................................75

• Changed Register definition to move a statement from Section 8.6.17 to Section 8.6.16 ...............................75

• Changed default of bit 9 from '1' to '0' in Configuration Register 2 (CFG2), Address 0x0014 ......................... 79

• Changed default of bits 5:0 from '0' to '0 0111' in Table 8-27 ...........................................................................79

• Added Section 8.6.29 register.......................................................................................................................... 89

• Changed Name of Bits 6:5 from 'STRAP_SPEED_SEL' to 'STRAP_ANEG_SEL' in Table 8-46 .................... 94

• Changed Name of Bit 6 from 'RESERVED' to 'RESERVED (RGZ)' in Table 8-46 .......................................... 94

• Changed Name of Bit 5 from 'STRAP_SPEED_SEL (PAP)' to 'STRAP_SPEED_SEL (RGZ)' in Table 8-46 ..94

• Changed name of Bit 6:4 from 'RESERVED' to 'RESERVED (PAP)' in Table 8-47 .........................................95

• Added description for 'STRAP_RGMII_CLK_SKEW_TX (RGZ)' in Table 8-47 ............................................... 95

• Changed name of Bit 2:0 from 'RESERVED' to 'RESERVED (PAP)' in Table 8-47 .........................................95

• Added description for 'STRAP_RGMII_CLK_SKEW_RX (RGZ)' in Table 8-47 ...............................................95

• Changed default value of bit 4:0 from '10000' to 'TRIM' in Section 8.6.97 .................................................... 106

• Changed description for IO_IMPEDANCE_CTRL bits in Section 8.6.97 .......................................................106

• Changed Section 10 section...........................................................................................................................125

• Added "The 2.5-V VDDA2P5 can come up with or after the 1.8-V VDDA1P8 but not before it" to Section 10 ...

125

• Added Figure 10-3 ......................................................................................................................................... 125

• Added Table 10-1 ...........................................................................................................................................125

• Added note regarding 1.8-V supply sequence if no load exists on 2.5-V supply in Layout ........................... 125

Changes from Revision B (August 2015) to Revision C (November 2015) Page

• Changed the title to add DP83867IRRGZ/CRRGZ in the datasheet. ................................................................ 1

• Added part numbers .......................................................................................................................................... 1

• Changed latency bullet point in Section 1for better description of the Low Latency Feature............................. 1

• Changed Power consumption number in Features section................................................................................ 1

• Added Radiated Emissions performance to Section 1 ...................................................................................... 1

• Added MDI Termination Resistor in Section 1 ................................................................................................... 1

• Added Programmable MAC Interface Impedance in ......................................................................................... 1

• Added 'RJ45 Mirror Mode' to Section 1 ............................................................................................................. 1

• Added compatibility to Section 1 ........................................................................................................................1

• Changed Section 1 to merge 'Highlights' and 'Key Specifications' into a single section.................................... 1

• Deleted specification about dual voltage from Section 1 ................................................................................... 1

• Added Dual supply voltage for RGZ devices in Section 1 ................................................................................. 1

• Deleted Auto-Crossover bullet point from Section 1 ..........................................................................................1

• Deleted duplicate Low latency specification ...................................................................................................... 1

• Deleted MDIO bullet point from key specification............................................................................................... 1

• Added MAC interface information in Description ............................................................................................... 1

• Added QFN power Consumption in Description ................................................................................................ 1

• Added Package information for the new devices in the Device Information table.............................................. 1

• Added Device Comparison Table....................................................................................................................... 8

• Changed Pin Functions table to add information about new RGZ devices...................................................... 10

• Changed bypass capacitor information for power pins in Pin Functions table................................................. 10

• Added information about pull-up pull-down resistors in the table note of the table ......................................... 10

• Added Unused Pins section .............................................................................................................................14

• Added Absolute Maximum Ratings table..........................................................................................................15

• Added ESD information about new RGZ devices in Section 7.2 ..................................................................... 15

• Added VDD1P0 information in Recommended Operating Conditions .............................................................15

• Added temperature information about RGZ devices in Recommended Operating Conditions ....................... 15

• Added thermal information for RGZ Devices in Section 7.4 ............................................................................ 16

• Added PMD output voltage data for new RGZ devices in Section 7.5 ............................................................ 16

• Added RGMII TX and RX Latency values in Section 7.9 .................................................................................19

• Added FBD for new RGZ devices in Functional Block Diagram ......................................................................32

DP83867IR, DP83867CR

SNLS484G – FEBRUARY 2015 – REVISED OCTOBER 2022

www.ti.com

4 Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

Product Folder Links: DP83867IR DP83867CR

• Added "Magic Packet should be byte aligned" in Magic Packet Structure section...........................................34

• Changed "Auto-MDIX is independent of Auto-Negotiation" to "For 10/100, Auto-MDIX is independent of Auto-

Negotiation" in Section 8.4.3.9 .........................................................................................................................46

• Added Loopback Availability table.................................................................................................................... 46

• Changed description for Section 8.4.4.1.4 .......................................................................................................47

• Added description for Section 8.4.4.2 ..............................................................................................................47

• Deleted mention of ALCD from Section 8.4.6 ..................................................................................................48

• Changed "improperly-terminated cables with ±1m accuracy" to "improperly-terminated cables, and crossed

pairs wires with ±1m accuracy" in Section 8.4.6.1 ...........................................................................................48

• Changed Mirror Mode Configuration table........................................................................................................49

• Added internal resistor to the diagram inFigure 8-12 .......................................................................................51

• Added Target voltage range in Table 8-3 ......................................................................................................... 51

• Added strapping information for RGZ devices in Table 8-4 ............................................................................. 51

• Changed incorrect pin number for LED_1 and LED_0 in Table 8-4 table.........................................................51

• Added RGMII TX and RX Skew Strap information to Table 8-4 ...................................................................... 51

• Added Table 8-6 ...............................................................................................................................................51

• Added Table 8-7 ...............................................................................................................................................51

• Added Table 8-8 ...............................................................................................................................................51

• Added information regarding address configuration of RGZ devices to Section 8.5.4 .................................... 55

• Added Power Saving Modes section................................................................................................................ 57

• Deleted repeated bits from Auto-Negotiate Expansion Register ..................................................................... 66

• Changed Bit 13 description in Register 0x14 ...................................................................................................79

• Deleted "in Robust Auto MDI-X modes" in bit 15 description of Section 8.6.25 .............................................. 85

• Added "ms" to timer values in bit 13:12 in Section 8.6.25 ............................................................................... 85

• Deleted Registers FLD_CFG and FLD_THR_CFG from Datasheet................................................................ 87

• Added Section 8.6.28 ...................................................................................................................................... 88

• Added Section 8.6.30 ...................................................................................................................................... 90

• Changed description for bit 11 in Section 8.6.34 ............................................................................................. 92

• Added information in bit 10:7 description for Section 8.6.34 ........................................................................... 92

• Added Section 8.6.35 ...................................................................................................................................... 93

• Added Section 8.6.41 ...................................................................................................................................... 96

• Added Section 8.6.42 ...................................................................................................................................... 96

• Added Section 8.6.47 ...................................................................................................................................... 97

• Added Section 8.6.51 ...................................................................................................................................... 98

• Added comment about RGZ devices in Section 8.6.98 ................................................................................. 108

• Added comment about RGZ devices in Section 8.6.99 ................................................................................. 110

• Added GPIO_MUX_CTRL register for RGZ devices.......................................................................................111

• Added TDR registers 0x0190 to 0x01A4.........................................................................................................112

• Added TDR registers.......................................................................................................................................112

• Added footnote about voltage level for RGZ devices in Figure 10-1 ............................................................. 125

• Added Comment for VDDA1P8 pins in Figure 10-1. ..................................................................................... 125

• Added footnote about Voltage level for RGZ devices in Figure 10-2 .............................................................125

• Added power down supply sequence sentence in Section 10 .......................................................................125

Changes from Revision A (June 2015) to Revision B (August 2015) Page

• Added "Power consumption as low as 490 mW" to the Section 1 list................................................................ 1

• Changed Section 3 text From: "The DP83867 consumes only 565 mW" To: "The DP83867 consumes only

490 mW"............................................................................................................................................................. 1

• Changed Pin RBIAS Description From: "A 10 kΩ +/-1% resistor" To: "A 11 kΩ ±1% resistor"......................... 10

• Changed Power consumption, 2 supplies TYP value From 565 mW To 530 mW in the Section 7.5 .............. 16

• Changed Power consumption, optional 3rd supply TYP value From 545 mW To 490 mW in the Section 7.5 ....

16

• Changed Register address: From: "BICSR1 register (0x0039)" To: "BICSR2 register (0x0072)", and changed

From: "read from the BISCR register (0x0016h)" To: "read from the STS2 register (0x0017h)" in the Section

8.4.5 .................................................................................................................................................................48

www.ti.com

DP83867IR, DP83867CR

SNLS484G – FEBRUARY 2015 – REVISED OCTOBER 2022

Copyright © 2022 Texas Instruments Incorporated

Submit Document Feedback

5

Product Folder Links: DP83867IR DP83867CR

剩余142页未读,继续阅读

资源评论

yasin墨染锦年

- 粉丝: 5530

- 资源: 9

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功