触发器实验报告.doc

2.虚拟产品一经售出概不退款(资源遇到问题,请及时私信上传者)

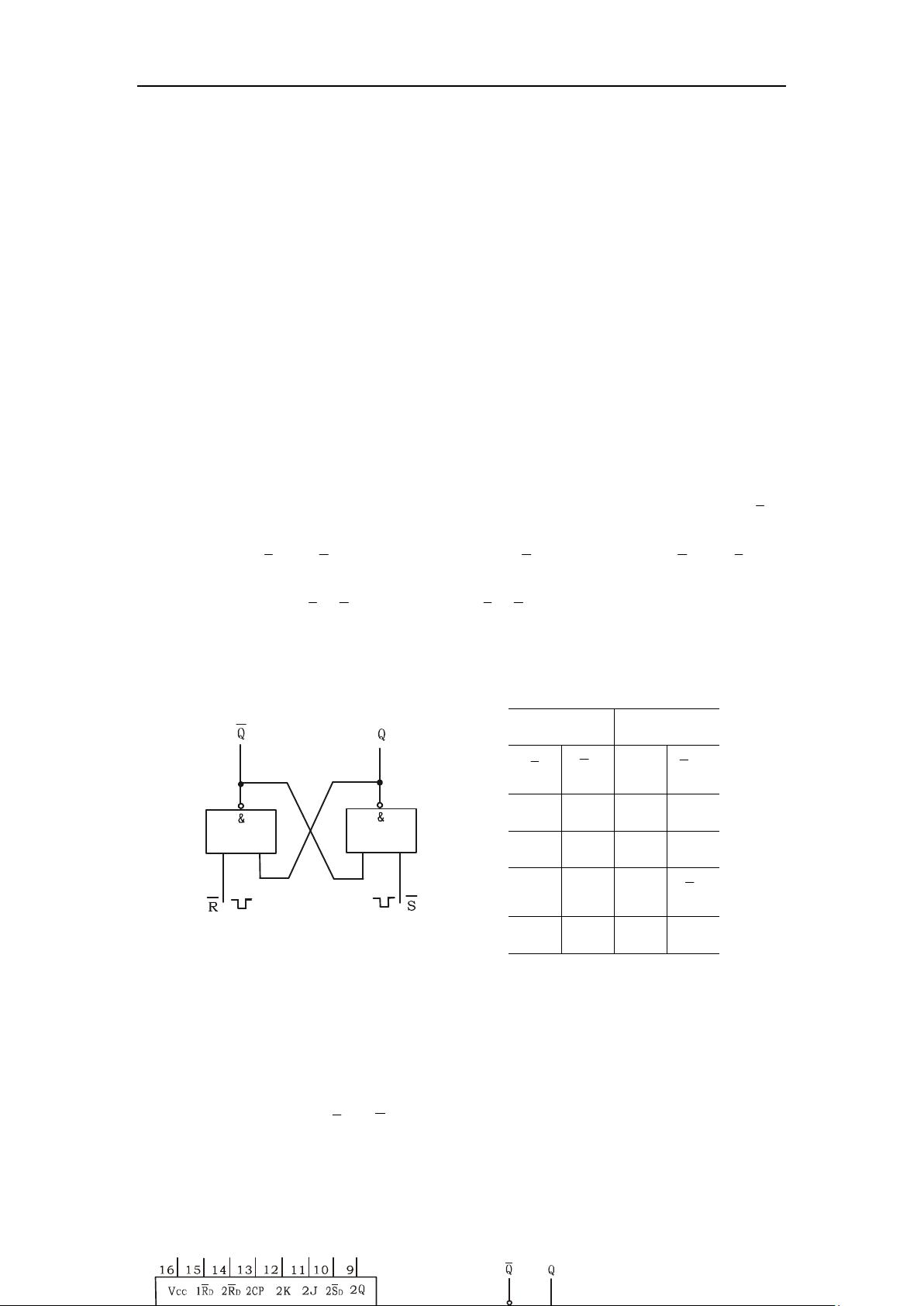

实验3 触发器及其应用 一、实验目的 1、掌握基本RS、JK、D和T触发器的逻辑功能 2、掌握集成触发器的逻辑功能及使用方法 3、熟悉触发器之间相互转换的方法 二、实验原理 触发器具有两个稳定状态,用以表示逻辑状态"1"和"0",在一定的外界信号作用下 ,可以从一个稳定状态翻转到另一个稳定状态,它是一个具有记忆功能的二进制信息存 贮器件,是构成各种时序电路的最基本逻辑单元。 1、基本RS触发器 图5-8-1为由两个与非门交叉耦合构成的基本RS触发器,它是无时钟控制低电平直 接触发的触发器。基本RS触发器具有置"0"、置"1"和"保持"三种功能。通常称为置 "1"端,因为=0(=1)时触发器被置"1";为置"0"端,因为=0 (=1)时触发器被置"0",当==1时状态保持;==0时, 触发器状态不定,应避免此种情况发生,表5-8-1为基本RS触发器的功能表。 基本RS触发器。也可以用两个"或非门"组成,此时为高电平触发有效。 表5-8-1 "输 入 "输 出 " "[pic"[pic"Qn+1"[pic" "] "] " "]n+1" "0 "1 "1 "0 " "1 "0 "0 "1 " "1 "1 "Qn "[pic" " " " "]n " "0 "0 "φ "φ " 图 5—8—1 基本RS触发器 2、JK触发器 在输入信号为双端的情况下,JK触发器是功能完善、使用灵活和通用性较强的一种触发 器。本实验采用74LS112双JK触发器,是下降边沿触发的边沿触发器。引脚功能及逻辑符 号如图5-8-2所示。 JK触发器的状态方程为 Qn+1 =Jn+Qn J和K是数据输入端,是触发器状态更新的依据,若J、K有两个或两个以上输入端时,组 成"与"的关系。Q与 为两个互补输出端。通常把 Q=0、=1的状态定为触发器"0"状态;而把Q=1,=0定为"1"状态。 图5-8-2 74LS112双JK触发器引脚排列及逻辑符号 下降沿触发JK触发器的功能如表5-8-2 表5-8-2 "输 入 "输 出 " "[pic"[pic"CP "J "K "Qn+1"[pic" "]D "]D " " " " "]n+1" "0 "1 "× "× "× "1 "0 " "1 "0 "× "× "× "0 "1 " "0 "0 "× "× "× "φ "φ " "1 "1 " "0 "0 "Qn "[pic" " " " " " " "]n " "1 "1 " "1 "0 "1 "0 " "1 "1 " "0 "1 "0 "1 " "1 "1 " "1 "1 "[pic"Qn " " " " " " "]n " " "1 "1 " "× "× "Qn "[pic" " " " " " " "]n " 注:×— 任意态 — 高到低电平跳变 — 低到高电平跳变 Qn(n )— 现态 Qn+1(n+1 )— 次态 φ— 不定态 JK触发器常被用作缓冲存储器,移位寄存器和计数器。 3、D触发器 在输入信号为单端的情况下,D触发器用起来最为方便,其状态方程为 Qn+1=Dn,其输出状态的更新发生在CP脉冲的上升沿,故又称为上升沿触发的边沿触发 器,触发器的状态只取决于时钟到来前D端的状态,D触发器的应用很广,可用作数字信 号的寄存,移位寄存,分频和波形发生等。有很多种型号可供各种用途的需要而选用。 如双D 74LS74、四D 74LS175、六D 74LS174等。 图5-8-3 为双D 74LS74的引脚排列及逻辑符号。功能如表5-8-3。 图5-8-3 74LS74引脚排列及逻辑符号 表5-8-3 表5-8-4 "输 入 "输 出 " "[pic"[pic"CP "D "Qn+1"n" "]D "]D " " " "+1 " "0 "1 "× "× "1 "0 " "1 "0 "× "× "0 "1 " "0 "0 "× "× "φ "φ " "1 "1 " "1 "1 "0 " "1 "1 " "0 "0 "1 " "1 "1 " "× "Qn "n" "输 入 "输出 " "[pic"[pi"CP "T "Qn+1" "]D "c]D" " " " "0 "1 "× "× "1 " "1 "0 "× "× "0 " "1 "1 " "0 "Qn " "1 "1 " "1 "" " " " " "n " 4、触发器之间的相互转换 在集成触发器的产品中,每一种触发器都有自己固定的逻辑功能。但可以利用转换的 方法获得具有其它功能的触发器。例如将JK触发器的J、k两端连在一起,并认它为T端, 就得到所需的T触发器。如图5-8-4(a)所示,其状态方程为: Qn+1 =Tn +Qn (a) T触发器 (b) T'触 【触发器实验报告】 实验3主要探讨了四种类型的触发器:基本RS触发器、JK触发器、D触发器以及触发器间的相互转换。触发器作为基础的存储元件,其核心特性在于它们能维持两种稳定状态,代表二进制的0和1,并在特定条件下能够从一种状态翻转至另一种状态。 1. **基本RS触发器**: RS触发器由两个与非门交叉耦合构成,提供置"0"(S=0)、置"1"(R=0)和保持(S=R=1)功能。表5-8-1展示了其功能。要注意的是,当S和R同时为0时,触发器状态不确定,需要避免这种情况。此外,RS触发器也可以用两个或非门实现,此时为高电平触发。 2. **JK触发器**: JK触发器是一种双端输入的触发器,具有更丰富的功能,如下降沿触发。74LS112双JK触发器是实验中使用的例子。JK触发器的状态方程为Qn+1 = JQn + KQn,J和K是输入端,J=K=1时,状态翻转;J=K=0时,状态保持不变。JK触发器常用于缓冲存储、移位寄存器和计数器设计。 3. **D触发器**: D触发器在输入信号为单端时非常便捷,其状态仅取决于D端的时钟前沿状态,因此被称为上升沿触发的边沿触发器。D触发器广泛应用于数字信号存储、移位寄存和频率分频等场景。双D 74LS74是其中一种常见的型号。 4. **触发器转换**: 触发器可以通过特定的连接方式转换为其他类型。例如,JK触发器的J和K端短接可以形成T触发器,状态方程变为Qn+1 = Tn + Qn,T=0时保持状态,T=1时翻转。反之,T'触发器在每个时钟脉冲下都会翻转状态,适用于计数电路。D触发器通过Q端与D端相连也可以转换为T'触发器。 实验的目的不仅在于理解这些触发器的逻辑功能,还要掌握如何实际操作和使用集成触发器,以及如何根据需求转换触发器类型。这些基础知识对于理解和设计复杂的时序电路至关重要,是电子工程和计算机科学领域的基石。通过实验,学生可以深化对触发器工作原理的理解,提高实际操作技能,为后续的数字系统设计打下坚实的基础。

- 粉丝: 195

- 资源: 3万+

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

信息提交成功

信息提交成功

- 1

- 2

- 3

前往页