EDA技术实验报告.doc

2.虚拟产品一经售出概不退款(资源遇到问题,请及时私信上传者)

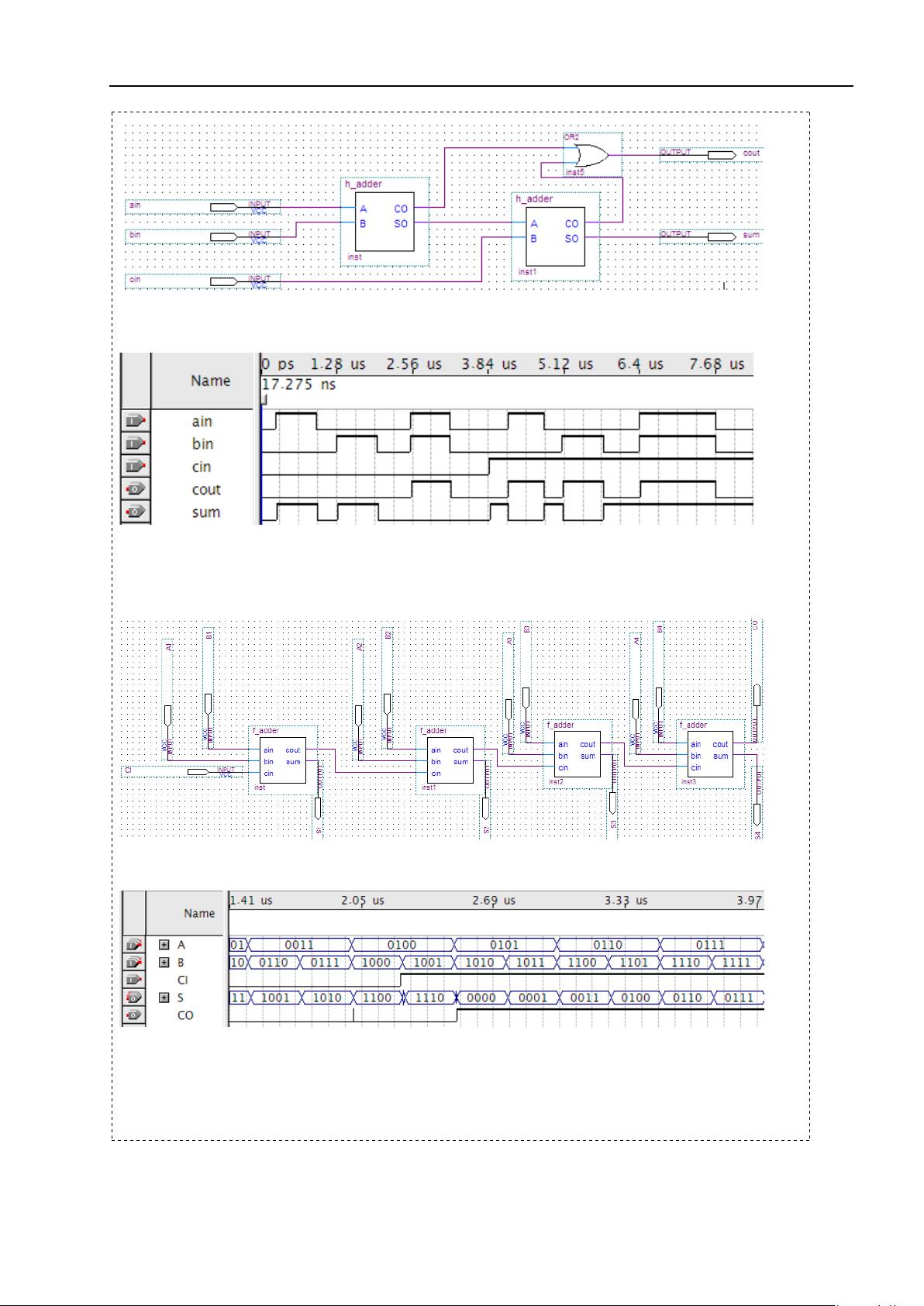

实验一 利用原理图输入法设计4位全加器 一、实验目的: 掌握利用原理图输入法设计简单组合电路的方法,掌握MAX+plusII的层次化设计方 法。通过一个4位全加器的设计,熟悉用EDA软件进行电路设计的详细流程。 二、实验原理: 一个4位全加器可以由4个一位全加器构成,全加器的进位以串行方式实现,即将低 位加法器的进位输出cout与相邻的高位加法器的低位进位输入信号cin相接。 1位全加器f-adder由2个半加器h-adder和一个或门按照下列电路来实现。 半加器h-adder由与门、同或门和非门构成。 四位加法器由4个全加器构成 三、实验内容: 1. 熟悉QuartusII软件界面,掌握利用原理图进行电路模块设计的方法。 QuartusII设计流程见教材第五章:QuartusII应用向导。 2.设计1位全加器原理图 (1)生成一个新的图形文件(file->new->graphic editor) (2)按照给定的原理图输入逻辑门(symbol->enter symbol) (3)根据原理图连接所有逻辑门的端口,并添加输入/输出端口 (4)为管脚和节点命名: 在管脚上的PIN_NAME处双击鼠标左键,然后输入名字; 选中需命名的线,然后输入名字。 (5)创建缺省(Default)符号: 在 File菜单中选择 Create Symbol Files for Current File 项,即可创建一个设计的符号,该符号可被高层设计调用。 3.利用层次化原理图方法设计4位全加器 (1)生成新的空白原理图,作为4位全加器设计输入 (2)利用已经生成的1位全加器的缺省符号作为电路单元,设计4位全加器的原理图. 4.新建波形文件(file->new->Other Files->Vector Waveform File),保存后进行仿真(Processing ->Start Simulation),对4位全加器进行时序仿真。给出波形图,并分析仿真结果是否正确。 "1位半加器: " "原理图: " " " " " "仿真波形: " " " "1位全加器: " "原理图: " " " "仿真波形: " " " "4位全加器: " "原理图: " " " "仿真波形: " " " "4位全加器仿真结果正确: " "例:0011(A)+0111(B)+0(CI)结果为1010(S),进位CO为0。 " 5.思考 如何在原理图中输入一个总线,并与其他总线连接? "先选中细线,然后右击,选"bus " "line",总线是以粗线条表示。与其他总线连接:例如一根8位的总线 bus1[7..0]欲与 " "另三根分别为1、3、4个位宽的连线相接,则它们的标号可分别表示为bus1[0],bus1[3" "..1],bus1[7..4]。 " 实验二 简单组合电路的设计 一、实验目的: 熟悉QuartusII VHDL文本设计流程全过程。学习简单组合电路的设计、多层次电路设计、仿真和硬件测 试。 二、实验原理 VHDL硬件描述语言是一种可以从多个层次上对数字逻辑电路进行建模的国际标准(IEEE) ,本次实验是用VHDL设计一个简单的数字组合逻辑电路,并结合QuartusII环境和实验电 路进行硬件测试。 三、实验内容: 1. 根据实验一中一位全加器的电路原理图,改用VHDL语言文本输入方法,设计一位全加器 ,要求采用结构化的描述方法。设计完成后,利用QuartusII集成环境进行时序分析、 仿真,记录仿真波形和时序分析数据。 2. 用VHDL语言设计一个四选一数据选择器电路。 要求先设计一个二选一数据选择器mux21,然后利用元件例化语句设计四选一数据选择 器mux41,同样请给出时序分析数据和仿真结果。 3)硬件测试(选用器件 EPF10K10 Pin84) 管脚锁定: 1)一位全加器 a PIO23(I/O19) 30 SW1 b PIO24(I/O20) 35 SW2 ci PIO25(I/O21) 36 SW3 s PIO21(I/O16) 27 LED10 co PIO19(I/O8) 29 LED12 2)四选一数据选择器 a1 PIO23 30 SW1 a0 PIO24 35 SW2 d3 PIO27 38 SW5 d2 PIO28 39 SW6 d1 PIO29 47 SW7 d0 PIO30 42 SW8 yout 29 LED12 四、思考题 比较原理图输入法和文本输入法的优缺点。 "实验结果: " "一位全加器的VHDL描述: " "半加器的VHDL描述: " "LIBRARY IEEE; " "USE IEEE.STD_LOGIC_1164.ALL; " "ENTITY h_adder IS " "PORT (a,b:IN STD_L 在现代电子工程设计领域,电子设计自动化(EDA)技术已经成为不可或缺的一部分。EDA技术通过计算机辅助设计(CAD)软件,大幅提高了电路设计的效率和复杂度,使工程师能够在更短的时间内完成更复杂的电路设计和验证。EDA技术实验报告.doc是关于通过实践学习掌握EDA工具QuartusII的使用,实现数字电路设计、仿真和验证的详细记录,包含两个实验,实验一着重于原理图输入法的设计,而实验二则着重于VHDL文本设计方法。 在实验一中,学生将通过原理图输入法设计一个4位全加器,该全加器由4个1位全加器串联构成,进位以串行方式实现。全加器的进位输出cout与相邻的高位加法器的低位进位输入cin相连接,构成一个完整的4位加法器。每一位全加器f-adder由两个半加器h-adder和一个或门组成。半加器的实现则需要与门、同或门和非门。通过此实验,学生不仅能够掌握原理图输入法设计简单组合电路的方法,而且还能熟悉QuartusII软件的设计流程和层次化设计方法。 实验的步骤涉及熟悉QuartusII界面,利用原理图设计电路模块,创建和管理项目文件,以及进行仿真。仿真过程中,学生将新建波形文件并进行时序仿真,通过观察波形图来分析电路是否正确实现了设计目标。实验结果的正确性通过仿真波形图来验证,例如,对于输入的二进制数0011(A)和0111(B),以及进位输入CI为0,正确的输出应为1010(S),进位CO为0。 实验二则转向使用VHDL硬件描述语言进行数字组合逻辑电路设计。VHDL是一种国际标准硬件描述语言,能够从多个层次上对数字逻辑电路进行建模。本实验要求学生使用VHDL重新设计实验一中的1位全加器,并利用QuartusII环境进行时序分析和仿真。此外,学生还需设计一个四选一数据选择器电路,这要求学生先设计一个二选一数据选择器,再通过元件例化技术构建四选一数据选择器。硬件测试环节要求学生利用特定的FPGA芯片进行测试,将设计的电路配置到硬件中,并进行实际的输入输出测试验证。 此实验不仅让学生掌握VHDL设计流程,而且加深了对多层次电路设计、仿真以及硬件测试的理解。学生需要进行时序分析,记录仿真波形和时序分析数据,以及在实验电路板上进行硬件测试,将设计的电路实际运行起来,观察指示灯等输出设备的响应,验证设计的正确性。 通过这两个实验,学生不仅能够深入理解原理图输入法和VHDL文本输入法在电路设计中的应用,而且能够评估两种方法各自的优缺点。原理图输入法直观易懂,适合初学者快速上手,但面对复杂电路时,管理变得困难。VHDL文本输入法抽象且专业性高,能够清晰地描述复杂的电路逻辑,适合用于大规模集成电路设计,便于逻辑功能的验证和综合优化,但其学习曲线相对陡峭,要求学生有一定的逻辑思维和编程基础。 EDA技术实验报告.doc详细记录了利用QuartusII软件进行数字电路设计、仿真和硬件测试的学习过程,涵盖原理图输入法和VHDL文本输入法的设计与分析。通过这些实验,学生能够深刻理解EDA技术在现代集成电路设计中的重要性,掌握实用的设计技巧,并对电子工程领域形成更全面的认识。

剩余36页未读,继续阅读

- 粉丝: 197

- 资源: 3万+

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 博思智联-三联集团-新乡连锁店培训流程说明.doc

- 博思智联-三联集团-职位评估培训.ppt

- 博思智联-三联集团-新乡培训流程说明.doc

- Delphi编程-Oracle-控件-delphi连接Oracle数据库控件

- mysql安装配置教程.txt

- 泛华-中国青年报项目—岗 位 描 述 书培训模搬.doc

- 和君创业—上海西域酒业项目培训—培训计划2.doc

- 和君创业—上海西域酒业项目培训—培训小结(提要)学员使用.doc

- 和君创业—上海西域酒业项目培训—业务员培训资料目录.doc

- 基于antlr4 解析器,支持spark sql, tidb sql, flink sql, Sparkflink jar 运行命令解析器详细文档+全部资料.zip

- 毕业设计:基于MQTT的物联网设备接入平台、使用Flink流处理框架详细文档+全部资料.zip

- 基于 SSM 框架,Flink 流,MySQL 数据库、BS 架构的小说网站详细文档+全部资料.zip

- 基于docker的实时监控系统,详细文档+全部资料.zip

- 基于Bilibili公开的数据,通过Flink实时分析计算,做成需要的动态图表详细文档+全部资料.zip

- IMG_20241218_182829.jpg

- 华彩--三鼎控股—华鼎锦纶子集团培训管理办法--外派培训9.27.doc

信息提交成功

信息提交成功

- 1

- 2

- 3

前往页