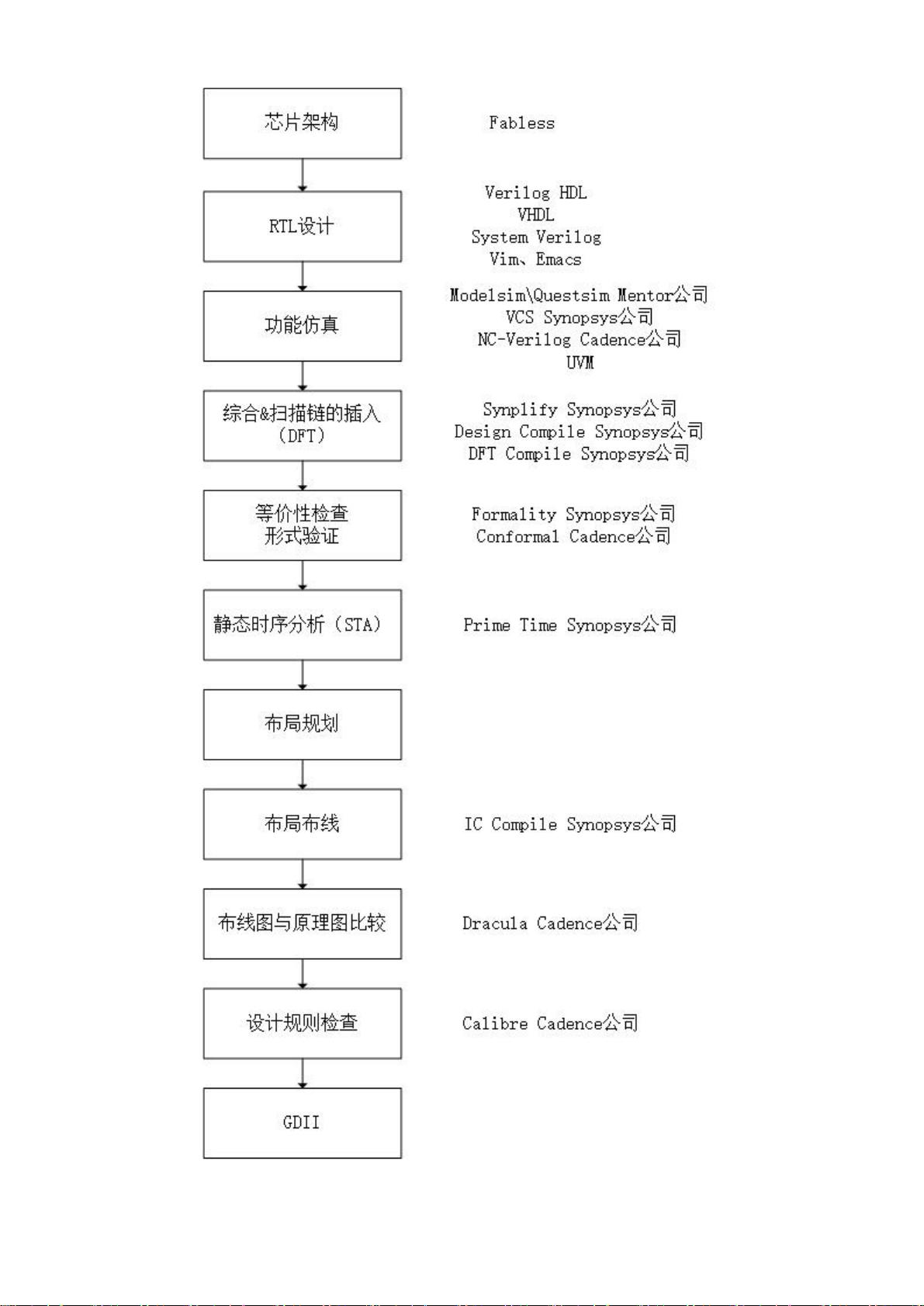

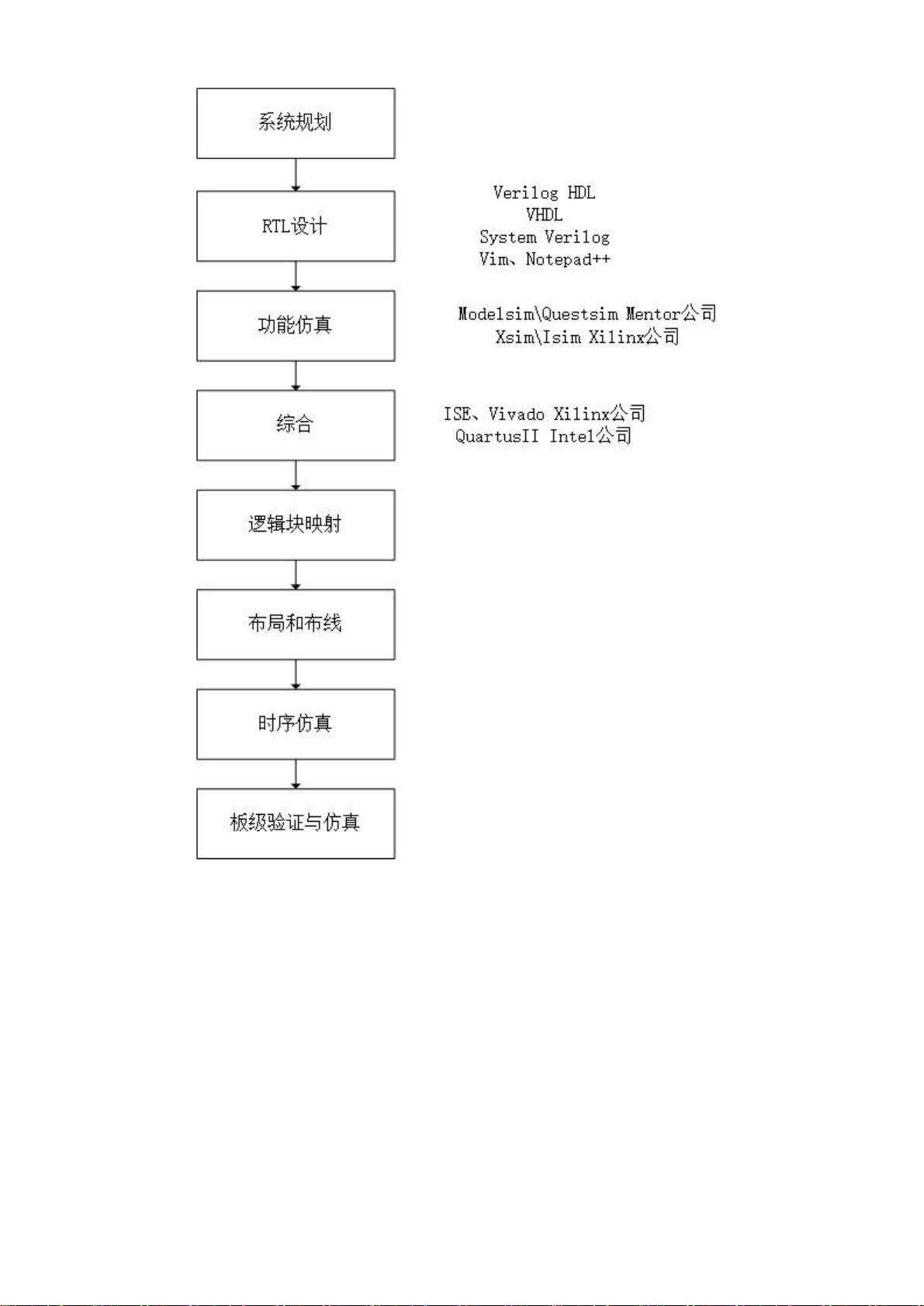

你要的FPGA&数字前端笔面试题来了 FPGA&ASIC基本开发流程 题目:简述ASIC设计流程,并列举出各部分用到的工具。 ASIC开发基本流程 题目:简述FPGA的开发流程。 FPGA开发基本流程 题目:名词解释: 数字电路基础 题目:数制转换 题目:逻辑函数及其化简 题目:什么是冒险和竞争,如何消除? 题目:用与非门等设计一个全加法器 题目:MOS逻辑门 题目:用D触发器带同步高置数和异步高复位端的二分频的电路,画出逻辑电路,Verilog描述。 题目:ASIC中低功耗的设计方法和思路(不适用于FPGA) 时序逻辑电路基础 题目:简述建立时间和保持时间,作图说明 题目:说明D触发器与Latch的区别。 题目:最小周期计算 题目:什么是Clock Jitter和Clock Skew,这两者有什么区别。 题目:什么是亚稳态,产生的原因,如何消除? 题目:同步和异步 题目:谈谈对Retiming技术的理解 数字集成电路 题目:反相器的速度与哪些因素有关?什么是转换时间(transition time)和传播延迟(propagation delay)? 题目:什么是高阻态 ... 在电子工程领域,FPGA(Field-Programmable Gate Array)和数字前端是重要的概念,它们在硬件设计和集成电路开发中扮演着核心角色。这里我们深入探讨这些领域中常见的笔面试题及其涉及的知识点。 ASIC(Application-Specific Integrated Circuit)设计流程包括: 1. **芯片架构**:定义芯片的功能需求、性能指标和工艺选择。 2. **RTL设计**:使用Verilog、System Verilog或VHDL编写描述硬件逻辑的代码。 3. **功能仿真**:通过软件模拟确保设计功能的正确性。 4. **DFT(Design for Testability)**:插入测试结构,便于芯片制造后的测试。 5. **等价性检查**:验证RTL代码与门级网表的一致性。 6. **STA(Static Timing Analysis)**:分析设计的时序性能,确保满足速度要求。 7. **布局规划**和**时钟树综合**:优化电路布局和时钟网络分布。 8. **DRC(Design Rule Check)**和**LVS(Layout vs. Schematic)**:确保设计符合制造规则,检查布局布线的准确性。 9. **GDSII生成**:最终输出用于制造的图形数据。 接着,FPGA的开发流程相对简单: 1. **系统规划**:确定FPGA应用的系统功能和模块。 2. **RTL设计**:编写Verilog或其他硬件描述语言的代码。 3. **功能仿真**:验证设计功能。 4. **综合、编译和布局布线**:使用厂商提供的工具完成。 5. **时序仿真**:分析时序约束,确保满足设计速度要求。 6. **板级验证**:在实际硬件上测试设计。 数字电路基础题目的知识点包括: - **数制转换**:二进制、八进制、十进制、十六进制之间的转换。 - **逻辑函数及其化简**:布尔代数,卡诺图,最简与或表达式。 - **冒险和竞争**:由于延迟不匹配导致的逻辑错误,可通过添加适当的缓冲器或改变时序约束来消除。 - **全加法器设计**:用与非门实现加法运算。 - **MOS逻辑门**:NMOS、PMOS和CMOS逻辑门的工作原理。 - **D触发器和Latch**:理解它们的存储功能,以及同步和异步复位的区别。 - **时序逻辑**:建立时间和保持时间,亚稳态,时钟抖动(Clock Jitter)和时钟偏移(Clock Skew)的概念及影响。 - **Retiming技术**:优化设计时序,通过重新安排逻辑路径来改进性能。 数字集成电路方面的问题涵盖: - **反相器速度**:与器件尺寸、阈值电压、负载电容等因素相关。 - **转换时间和传播延迟**:衡量信号变化速度和信号通过逻辑门所需的时间。 - **高阻态**和**Open-Drain Output**:理解和应用在接口和驱动电路中。 - **CMOS门速度比较**:非门与或非门的相对速度取决于结构和设计。 - **Clock Gating Cell**:用于降低功耗的技术,只在需要时才使能时钟。 在Verilog编程中,常遇到的问题包括: - **跨时钟域**:使用同步器、FIFO等解决时钟域间的信号传输。 - **信号边沿检测**:检测上升沿或下降沿,产生脉冲信号。 - **串并转换**:将串行数据转换为并行数据,反之亦然。 - **序列检测器**:实现特定序列的检测逻辑。 - **异步双端口RAM**:独立读写操作的存储器设计。 - **分频电路**:实现特定频率的输出。 - **时钟切换电路**:平滑切换两个异步时钟源。 - **同步FIFO**:实现具有读写指针和深度控制的FIFO。 - **IIC协议**:低速通信协议的Verilog实现。 - **异步FIFO**:不受时钟同步限制的FIFO设计。 - **按键抖动消除**:通过滤波或计数机制消除按键按下时的短暂抖动。 这些问题反映了FPGA和数字前端设计工程师必须掌握的基础知识和高级技能,包括硬件描述语言、逻辑设计、时序分析、低功耗设计以及硬件验证等方面。熟悉这些知识点对于准备面试和实际项目开发至关重要。

剩余34页未读,继续阅读

- 粉丝: 3w+

- 资源: 32

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜 信息提交成功

信息提交成功