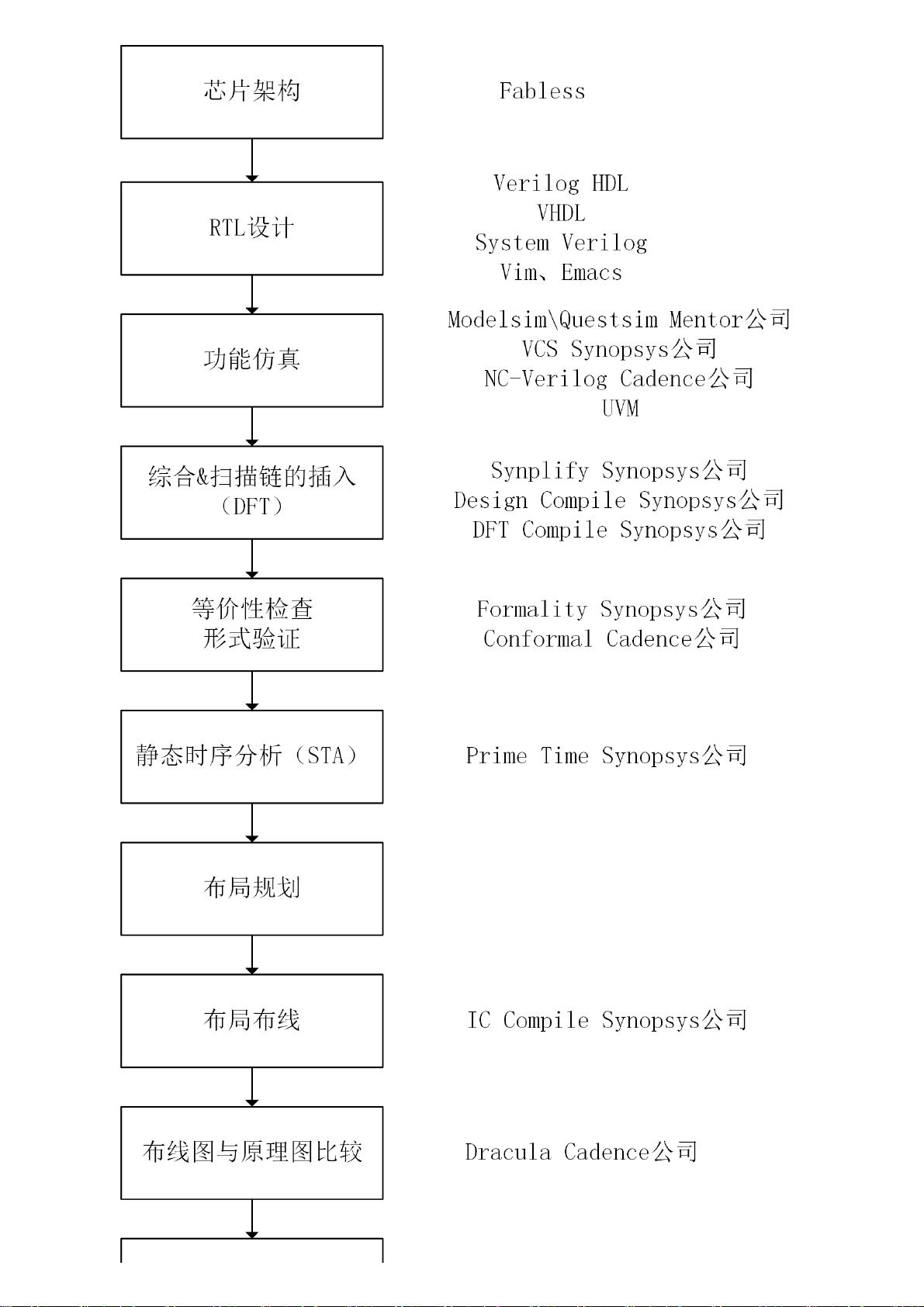

FPGA(现场可编程门阵列)和ASIC(应用特定集成电路)是现代数字电路设计中的两种重要技术。ASIC具有更高的性能和更低的功耗,但成本高且开发周期长。相比之下,FPGA灵活性更高,开发周期较短,适用于需要快速原型开发和小规模生产的场景。本文针对FPGA和ASIC的面试题展开详细解析。 ASIC设计流程主要分为以下阶段:需求分析、系统设计、前端设计、后端设计、制造、封装与测试。在前端设计阶段,常用的工具有VHDL/Verilog语言用于编写硬件描述语言(HDL),逻辑仿真工具(如ModelSim)用于验证设计的正确性,综合工具(如Design Compiler)用于将HDL代码综合为门级网表。后端设计阶段涉及布局布线(Place and Route),通常使用的工具有Cadence Encounter或Synopsys IC Compiler等。 FPGA开发流程则包含设计输入(通常是HDL代码)、综合、实现(包括布局布线)、仿真验证、硬件测试。FPGA的开发和验证可以使用Xilinx Vivado或Intel Quartus等综合工具来完成。 数字电路基础方面,需要了解位(bit)、字节(byte)、字(word)、双字(dword)、四字(qword)等概念。这些是基本的数据单位,其中1字节等于8位,1字等于2字节,1双字等于2字,1四字等于2双字。 原码、反码、补码、符号-数值码是用于表示带符号整数的编码方式。以8位为例,原码的表示范围是-127到+127(最高位为符号位),反码将原码除符号位外的其他位取反,补码则是在反码的基础上加1。符号-数值码即为补码。 数制转换包括二进制、八进制、十进制和十六进制之间的转换。逻辑函数及其化简涉及到布尔代数,是数字电路设计的基础。冒险和竞争是电路中的不希望出现的现象,冒险由逻辑门延迟引起,而竞争是由逻辑门的输入竞争引起。消除冒险的方法有卡诺图化简、引入冗余项等。 设计2-4译码器和BCD译码器是基础电路设计的一部分,需要考虑逻辑门的组合和电路的实现。MOS逻辑门是指使用金属氧化物半导体(MOS)技术构建的逻辑门,包括NMOS和PMOS。 D触发器是数字电路中的基本存储单元,带有同步高置数和异步高复位端的二分频电路的实现涉及到触发器的工作原理。CMOS反相器的功耗主要包括静态功耗和动态功耗,其中静态功耗与阈值电压和漏电流相关,动态功耗与电容充放电相关。 ASIC中的低功耗设计方法包括电源门控、多阈值CMOS、动态电压频率调整等,但这些技术不适用于FPGA。输入一个8位数,输出其中1的个数,若只能使用1位全加器,则最少需要多少个全加器来实现该功能,涉及组合逻辑和优化问题。 时序逻辑电路基础部分需要理解建立时间(setup time)和保持时间(hold time)的概念,并了解D触发器与锁存器(Latch)的区别。同步电路与异步电路的区别在于是否使用了统一的时钟信号。最小周期的计算、时钟抖动(Clock Jitter)与时钟偏差(Clock Skew)的区别及亚稳态的产生原因和消除方法均是FPGA设计中需要掌握的重要知识点。 阻塞赋值与非阻塞赋值、localparam、parameter和define、task与function的区别是Verilog语言中重要的概念,影响代码的可读性、性能和资源使用。 Retiming技术用于优化时序电路,是FPGA和ASIC设计中的高级话题。高阻态(High Impedance)通常用Z表示,亚稳态是指触发器在时钟边沿附近进入的一种不稳定状态。 在RTL代码编写方面,多时钟域设计处理包括异步信号同步、跨时钟域信号传输等。时钟切换电路、串并转换、PWM控制呼吸灯、序列检测器、异步双端口RAM、三分频电路、异步复位同步释放电路、按键抖动消除电路、同步FIFO、IIC协议的RTL设计、异步FIFO、双口RAM、真双口RAM、Register File、SRAM与DRAM、SDRAM与DDR、ROM的设计等,这些均为FPGA设计面试中的高频考点。 在设计中,通常需要理解信号边沿检测、状态机设计、存储器设计等,这些都是实现复杂数字电路的基石。FPGA设计的灵活性和高效性使其在众多领域有着广泛的应用。掌握上述知识点,对从事FPGA/ASIC开发的工程师来说至关重要。在进行面试准备时,应重视对上述概念的理解和掌握,并能熟练运用Verilog或VHDL等硬件描述语言进行实践。

剩余52页未读,继续阅读

- 粉丝: 1

- 资源: 9

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 1.电力系统短路故障引起电压暂降 2.不对称短路故障分析 包括:共两份自编word+相应matlab模型 1.短路故障的发生频次以及不同类型短路故障严重程度,本文选取三类典型的不对称短路展开研究

- 开源基于51单片机的多功能智能闹钟设计,课设毕设借鉴参考

- 深度强化学习电气工程复现文章,适合小白学习 关键词:能量管理 深度学习 强化学习 深度强化学习 能源系统 优化调度 编程语言:python平台 主题:用于能源系统优化调度的深度强化学习算法的性能比较

- 泰州市2005-2024年近20年历史气象数据下载

- 盐城市2005-2024年近20年历史气象数据下载

- 连云港市2005-2024年近20年历史气象数据下载

- 南通市2005-2024年近20年历史气象数据下载

- 饿了么bxet参数算法

- 医护人员检测22-YOLO(v5至v11)、COCO、CreateML、Paligemma、TFRecord、VOC数据集合集.rar

- nvm desktop -4.0.5-x64-setup

信息提交成功

信息提交成功