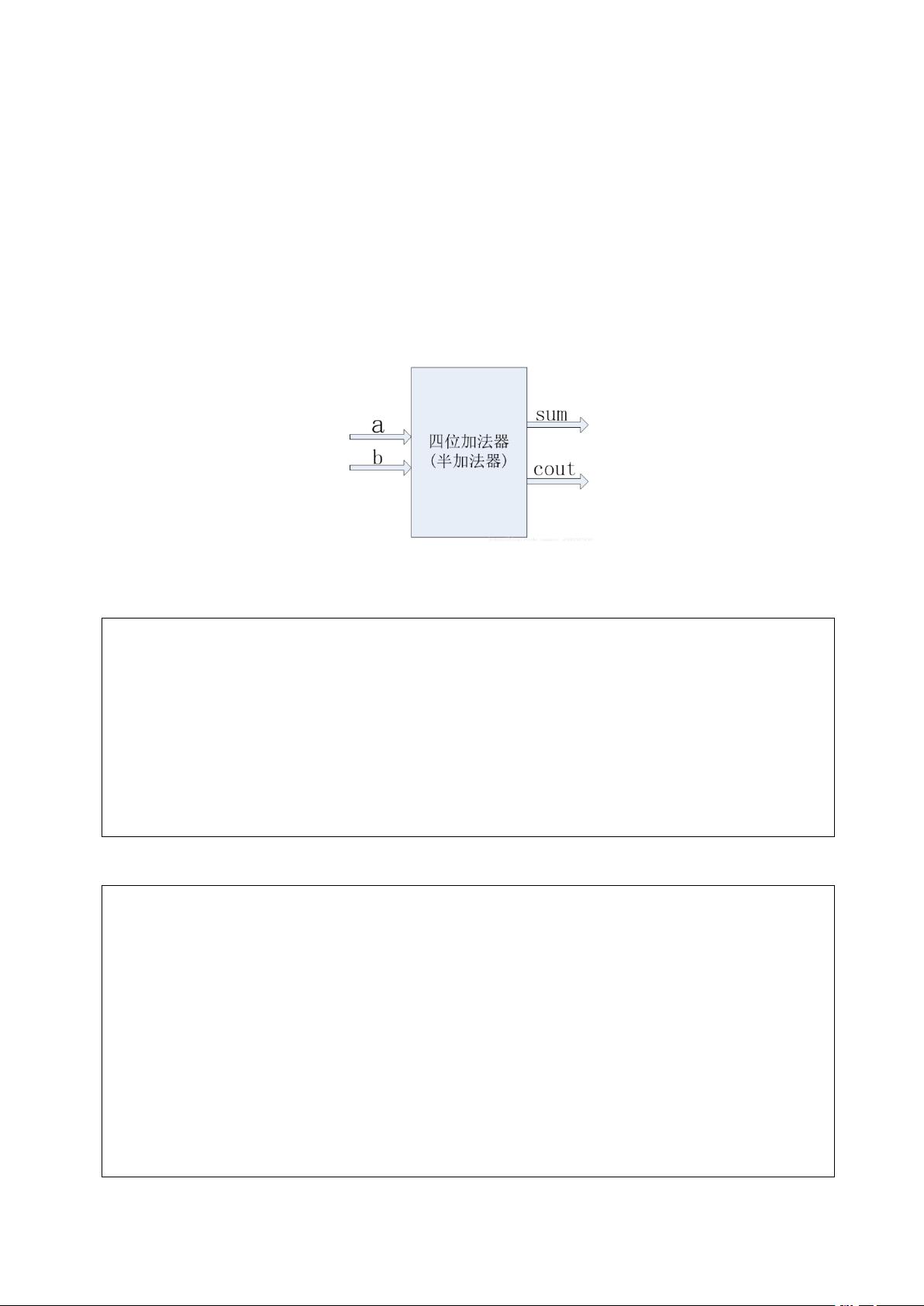

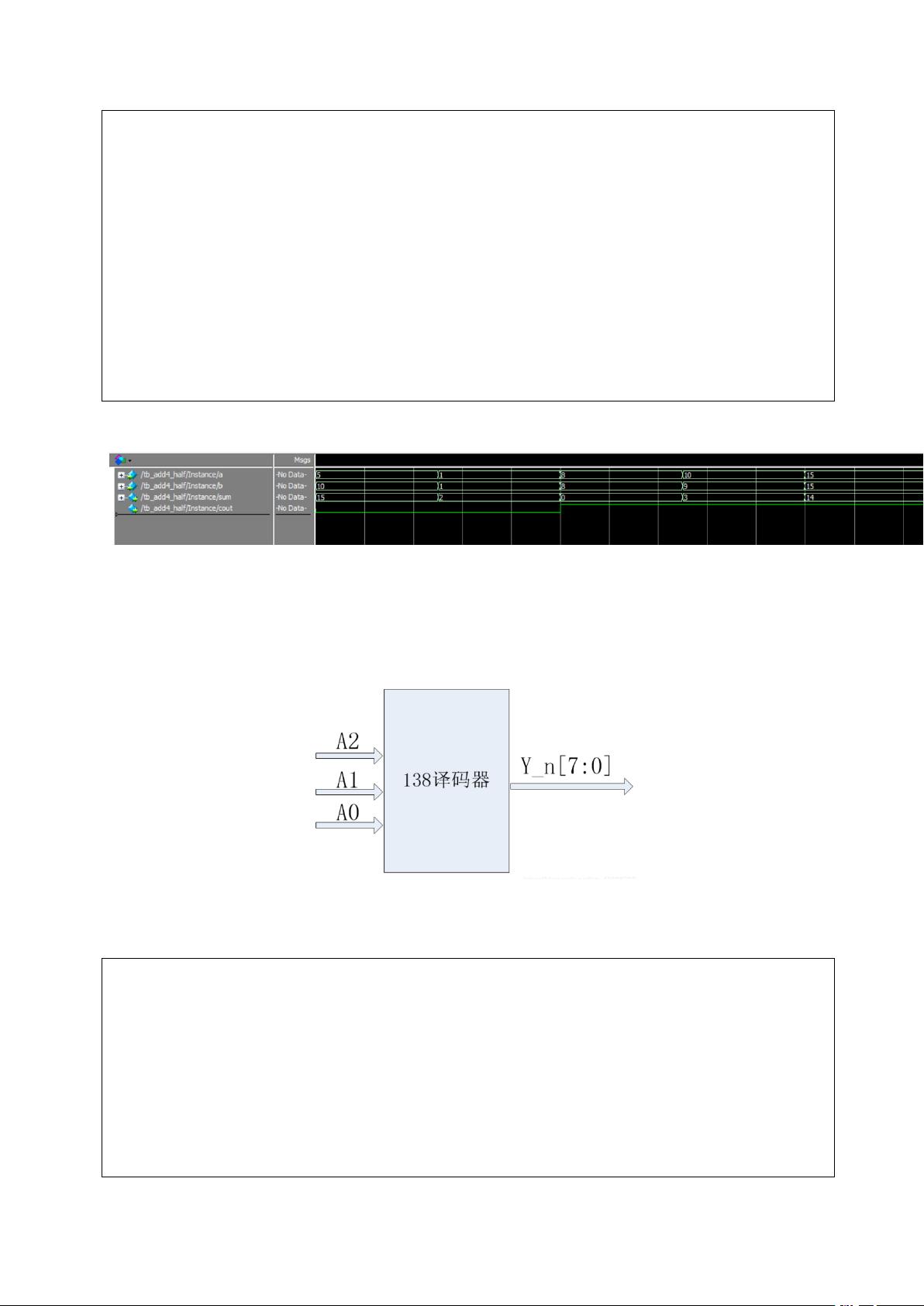

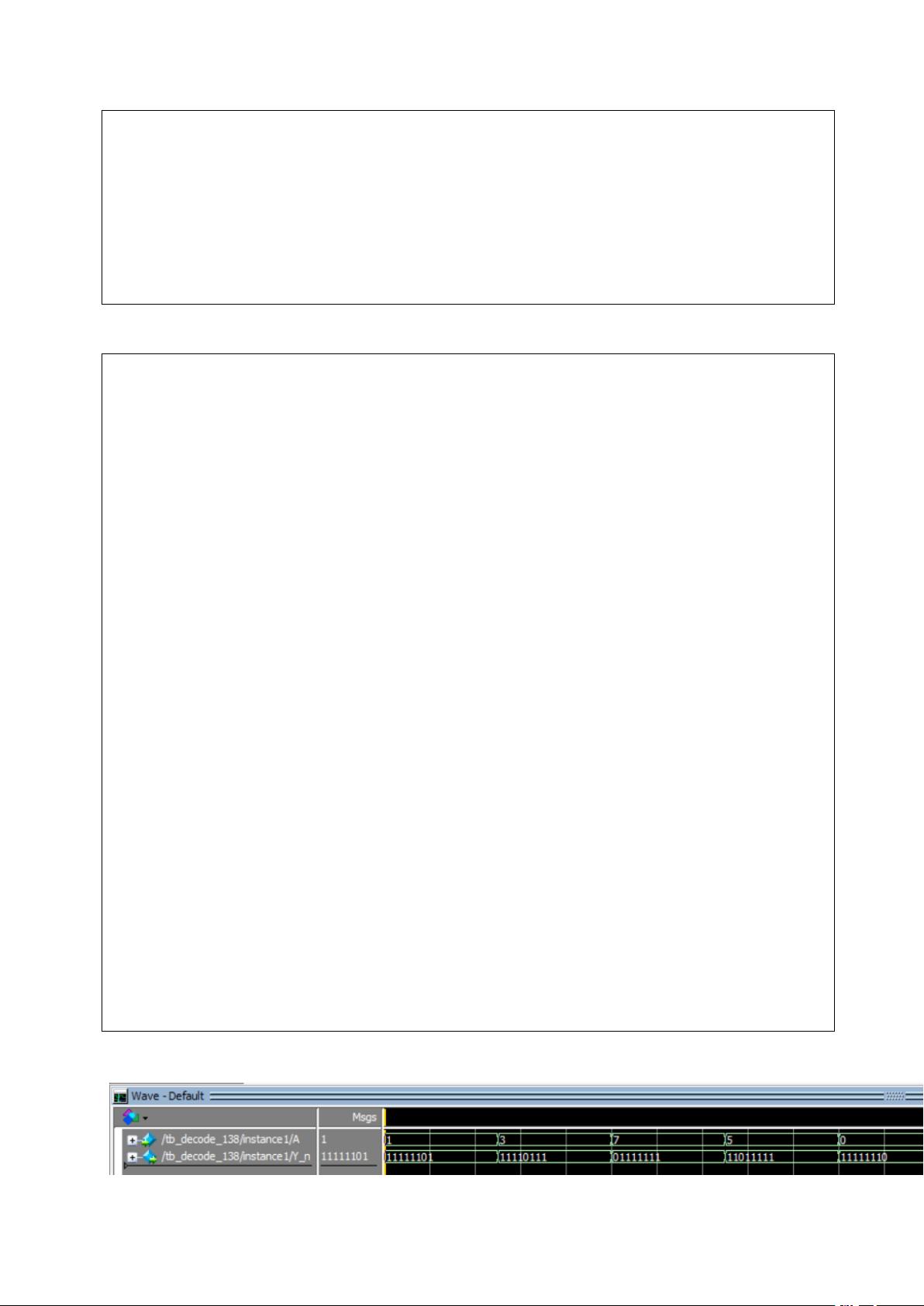

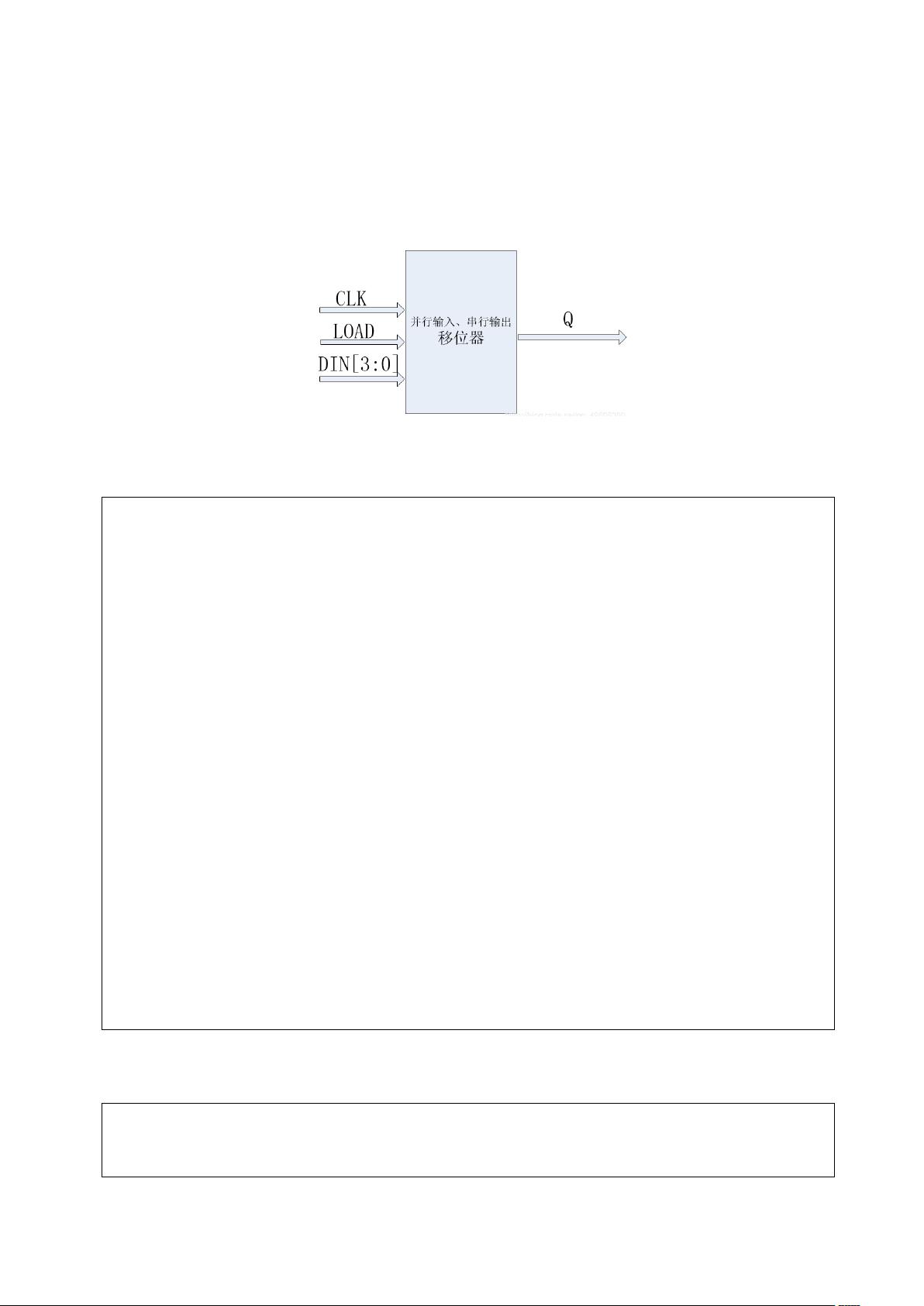

一、4位半加法器的Verilog实现 二、138译码器的Verilog实现 三、并行输入串行输出移位寄存器 四、带异步复位和置位、上升沿触发的触发器 五、模10计数器 六、停车位剩余计数显示牌的Verilog实现 七、银行排号机系统电路 八、分频器(2的偶数分频、16分频(占空比为2:14)、5分频) 九、四选一数据选择器——testbench仿真 十、ASK调制、FSK调制(正弦波) ———————————————— 原文链接:https://blog.csdn.net/qq_42605300/article/details/105760677 【FPGA系统-Verilog设计实验汇总】涵盖了10个数字系统电路的实现,这些电路在数字电子系统设计中有着广泛的应用。以下是每个实验的详细说明: 1. **4位半加器的Verilog实现**:半加器是基本的数字逻辑电路,用于计算两个二进制位的和,不考虑进位位。在Verilog中,通过定义模块`add4_half`,输入是4位的`a`和`b`,输出是4位的`sum`和一位的进位`cout`。使用`assign`语句直接计算`a + b`的和与进位。 2. **138译码器的Verilog实现**:138译码器是一种3-8线译码器,用于将三位二进制输入转换为八个输出信号。在Verilog中,`decode_138`模块根据输入`A`的3位值来设置8个输出`Y_n`的高低电平。使用`case`语句实现不同输入时的输出状态。 3. **并行输入串行输出移位寄存器**:这种电路可以将并行输入的数据转换为串行输出。它通常包括移位操作和时钟控制,可用于数据传输和存储。 4. **带异步复位和置位、上升沿触发的触发器**:触发器是数字系统的基础存储单元,能保持数据并在特定时钟边沿改变状态。异步复位和置位功能允许在任何时间重置或设定触发器的状态。 5. **模10计数器**:模10计数器是一种计数电路,其计数值在达到10后会回零,常见于计数和频率分频应用。 6. **停车位剩余计数显示牌的Verilog实现**:这个设计可能包括计数器和显示驱动逻辑,用于实时显示停车场的剩余车位。 7. **银行排号机系统电路**:这类系统通常包括多个输入模块(如客户取号),一个中央处理器(处理号码分配),以及显示设备(显示当前号码)。Verilog实现可能涉及队列管理、信号同步等技术。 8. **分频器**:分频器是将输入时钟频率分成固定比例的输出时钟。实验中提到了2的偶数分频、16分频(占空比2:14)和5分频,这涉及计数逻辑和时钟门控。 9. **四选一数据选择器**:四选一数据选择器允许通过选择信号从四个输入中选取一个数据进行输出。在Verilog中,通过testbench仿真测试数据选择逻辑的正确性。 10. **ASK调制、FSK调制(正弦波)**:ASK(振幅键控)和FSK(频率键控)是模拟信号调制方法,常用于无线通信。Verilog实现可能涉及到数字信号到模拟信号的转换算法。 以上实验展示了Verilog在FPGA系统设计中的应用,包括基本逻辑门、组合逻辑电路、时序逻辑电路、数字信号处理和通信系统。通过这些实验,学习者可以掌握Verilog语言并理解数字系统的设计原理。

剩余28页未读,继续阅读

- 粉丝: 6892

- 资源: 43

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- toad for db2 freeware

- vue 打印插件.zip

- Vue Tour 是一款轻量级、简单且可自定义的导览插件,可与 Vue.js 配合使用 它提供了一种快速简便的方式来引导用户浏览您的应用程序 .zip

- Vue SFC REPL 作为 Vue 3 组件.zip

- Vue JS-掌握 Web 应用程序.zip

- vue calendar fullCalendar 无需 jquery 计划事件管理.zip

- 头歌java实训作业-test-day09.rar

- 头歌java实训作业-test-day08.rar

- 头歌java实训作业-test-day07.rar

- Vue Argon 仪表板.zip

信息提交成功

信息提交成功