HDLGEN INTRODUCTION

WILSON CHEN

2023-05

CONTENT

⚫ OVERVIEW

⚫ USAGE

⚫ EMBEDDED FUNCTIONS

⚫ EXTENDED FUNCTIONS

⚫ OTHER FUNCTIONS

⚫ THANKS & NOTICE

OVERVIEW

HDLGen is a tool for HDL generation,it enables embedded Perl or

Python scripts in Verilog source code, and support Perl style variable

anyway, to generate desired HDL in an easy and efficient way.

It supports all syntax and data structure of Perl or Python,and has a

few predefined functions for signal define, module instance, port

connection etc.

This tool also supports extended API functions in Perl format(Python

API not on plan yet), for any function or module that you want or have.

HDL and script mixed design file can be any name, while final

generated RTL file will be Verilog(.v)

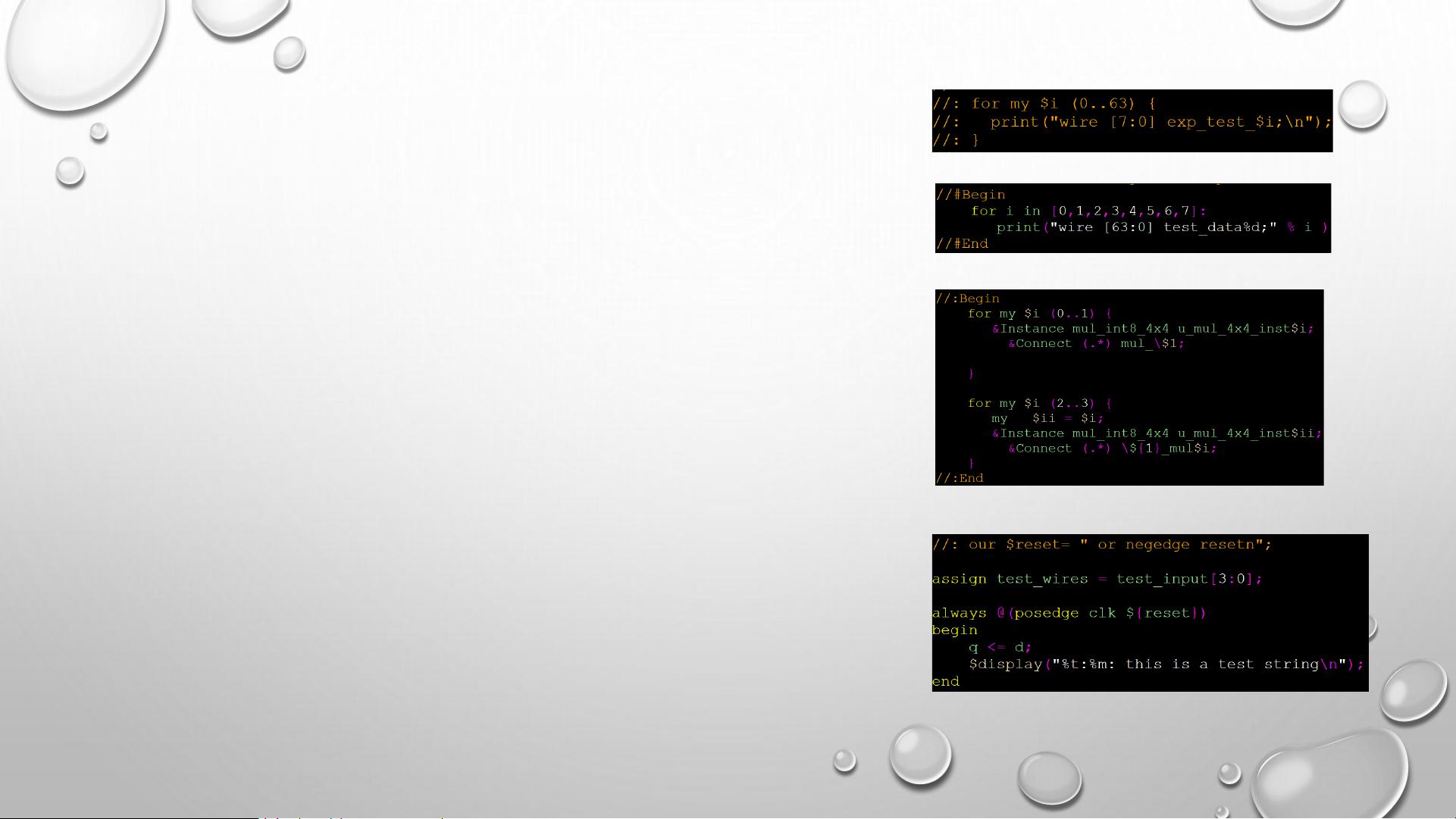

Assume line starting with “//:” to be single line Perl script;

Assume line starting with “//:Begin” and ending with “//:End” are multi-line

Perl script;

Assume line starting with “//#” to be single line Python script;

Assume line starting with “//#Begin” and ending with “//#End” are multi-

line Python script;

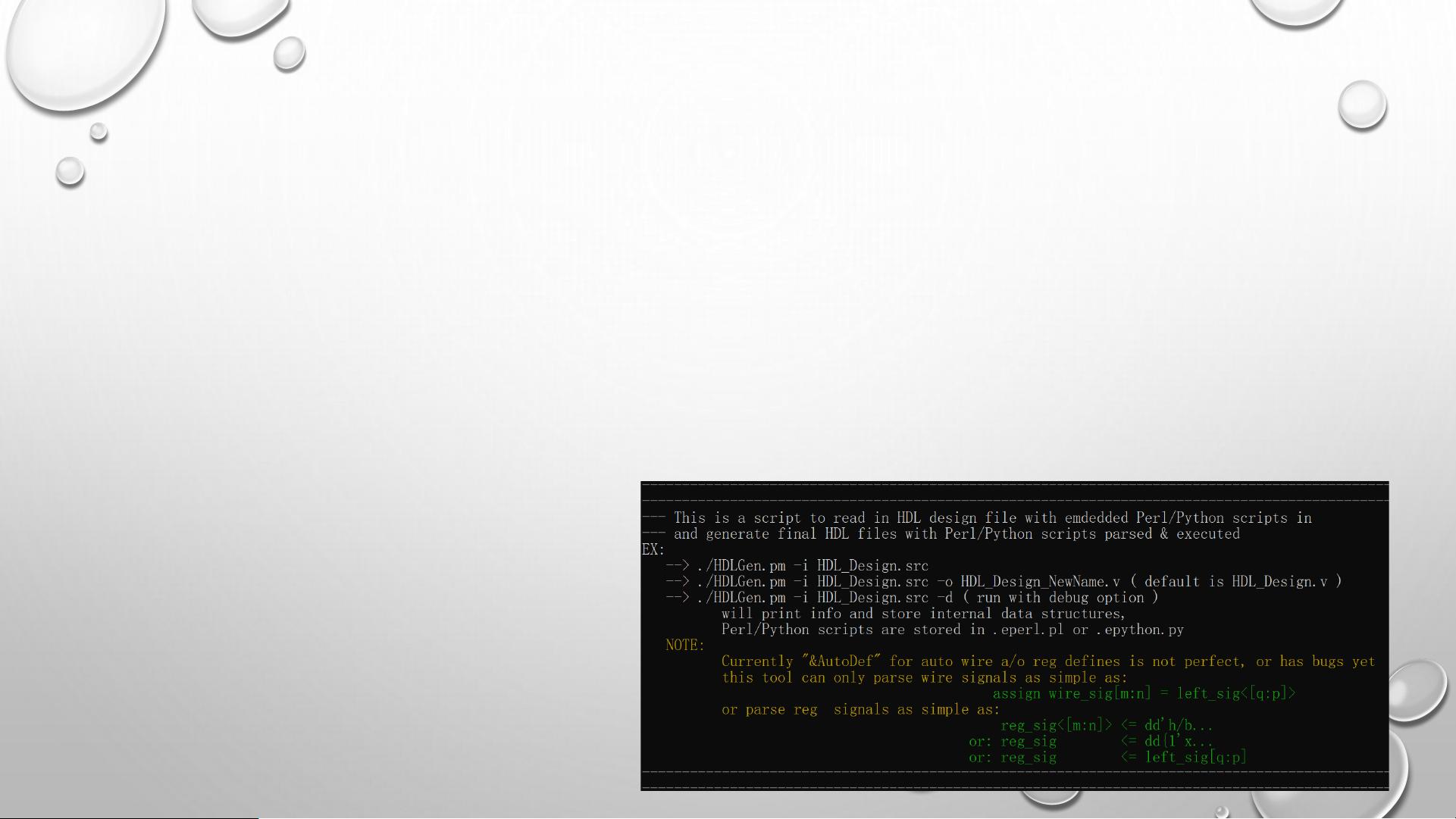

USAGE - INPUT

HDLGen supports single source file or multi-file(through a filelist file),generate Verilog HDL with same name. It

only need 1 input option de fault, like:

HDLGen.pm -i my_design.src

and my_design.v will be generated as a pure Verilog HDL file.

or HDLGen.pm –f src.flist, all files in src.flist will be processed and generate one Verilog file for 1 input.

Other options usage:

-u[usage] : print usage or helping message

-o[output] : override output file

-d[debug] : debug, several intermedia files will be saved to help debug

-v[verbose] : verbal mode,will print a lot of information on screen, if –debug turned on too(rarely used)

Suggestion:

⚫ Only use (-I ) in most case;

⚫ Turn on (-d) if error message not understood;

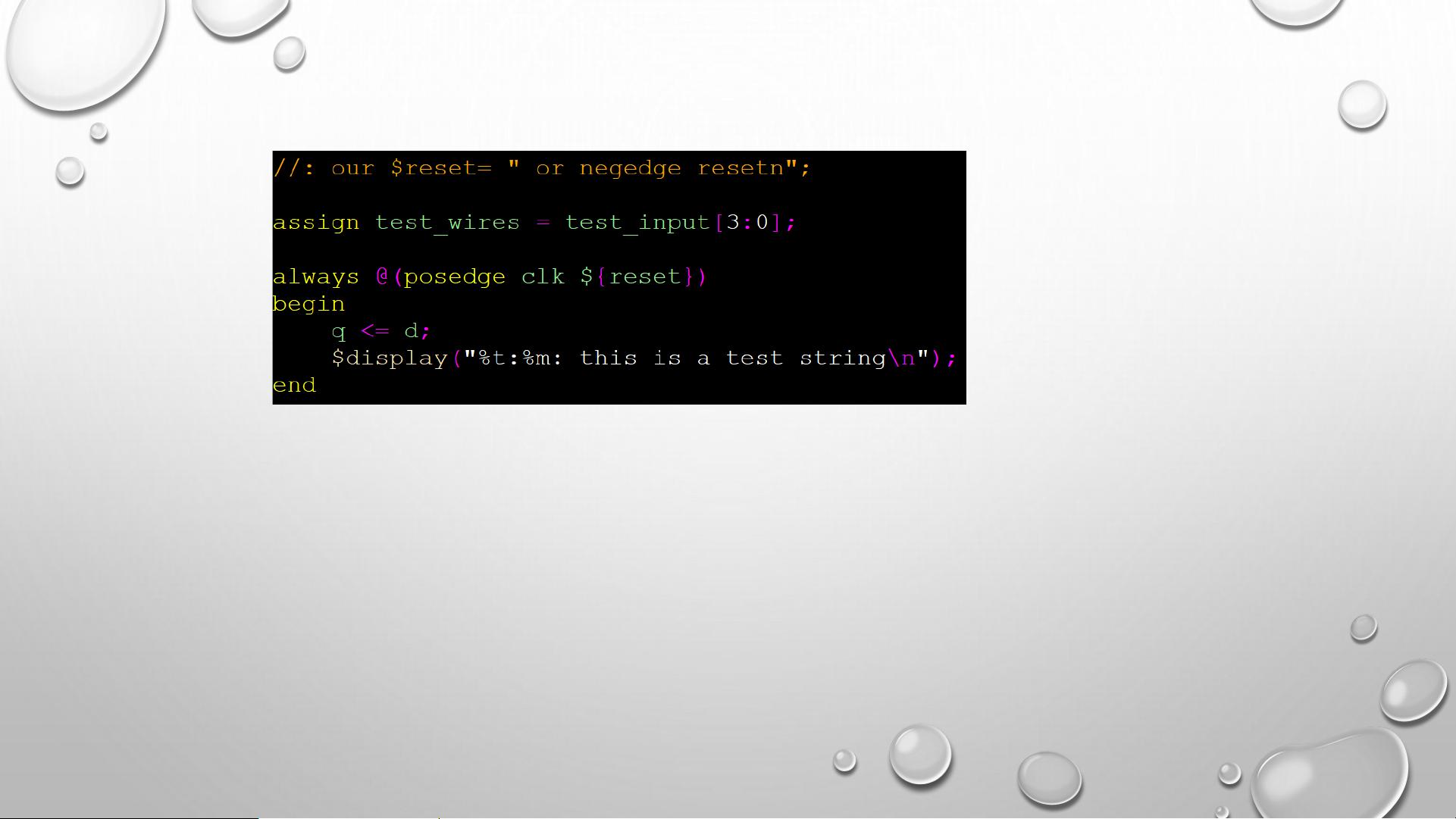

USAGE – FLEXIBLE VARIABLES

You can use Perl style variable wherever in Verilog code, as long as you defined such variable before using it.

Note:

⚫ Such variable can be used wherever as nati ve Verilog code, without any “//:”;

⚫ But such variable must be defined as “our” type;

⚫ And these variables must be used with “{}”, like ${reset}, to differentiate from Verilog embedded

functions;