2012

年

3

月

1

日

第

35

卷第

5

期

现代电子技术

Modern

Electronics

Techni

q

ue

Mar.2012

Vol.35No.5

基于

FPGA

的出租车计价系统设计

王

翠

(

盐城工学院 实验教学部

,

江苏 盐城

224051

)

摘

要

:

设计出租车计价系统

,

运用自顶向下的设计思想

,

以芯片

C

y

clone

Ⅱ

EP2C8T144C8

为设计核心

,

采用

Quartus

Ⅱ

仿真

软件

,

对设计电路的各模块及整个系统进行了

EDA

仿真验证

。

结果表明

,

该计价系统具有计时

、

计费

、

计程和动态显示的功

能

,

符合设计要求

,

修改

VHDL

语言源程序

,

可完成更多的出租车计价系统的扩展功能

。

关键词

:

出租车计价

;

自顶向下

;

VHDL

;

FPGA

中图分类号

:

TN911.7

-

34

文献标识码

:

A

文章编号

:

1004

-

373X

(

2012

)

05

-

0179

-

03

Desi

g

n

of

taximeter

based

on

FPGA

WANG

Cui

(

De

p

artment

of

Ex

p

erimental

Teachin

g

,

Yanchen

g

Institute

of

Technolo

gy

,

Yanchen

g

224051

,

China

)

Abstract

:

A

taximeter

based

on

Quartus

Ⅱ

simulation

software

was

desi

g

ned

b

y

usin

g

FPGA

chi

p

c

y

clone

Ⅱ

EP2C8T144C8

,

which

is

of

to

p

-

down

desi

g

n

idea.The

circuit

of

each

module

and

the

entire

s

y

stem

were

simulated.The

simulation

results

p

rove

that

the

taximeter

s

y

stem

is

of

countin

g

time

,

billin

g

,

meterin

g

and

d

y

namic

dis

p

la

y

function.To

modif

y

the

VHDL

lan

g

ua

g

e

source

code

,

it

can

com

p

lete

more

taximeter

extended

functions.

Ke

y

words

:

taximeter

;

to

p

-

down

;

VHDL

;

FPGA

收稿日期

:

2011

-

09

-

13

0

引

言

随着电子技术的发展

,

出租车计价器的设计也从传

统的全部由机械元器件组成的机械式设计到半电子式

(

即用电子线路代替部分机械器件的出租车计价器

[

1

]

),

再从集成电路式到目前基于

FGPA

芯片为核心的系统

的设计共经历了四个阶段

,

利用

FPGA

芯片

,

用较少的

外部硬件和适当的软件相互配合

,

可以通过软件编程来

完成更多的附加功能

,

设计比较灵活

,

并且还具有功耗

小

,

体积小

、

低成本

、

安全可靠

、

使用方便

[

2

]

等优点

。

因

此

,

使用

FPGA

来设计出租车计价系统已受到人们的

关注

,

也能更好地发挥其优点

。

本文 以

FPGA

为 设 计 载 体

,

通 过

VHDL

语 言 编

程

,

采用

Quartus

Ⅱ

仿真软件

,

设计了一种能动态显示

出租车计时

、

计费

、

计程的 系统

,

具有 一定的实际 应用

价值

。

1

出租车计价系统的设计要求

1.1

实现计费功能

车起步开 始 计 费

,

首 先 显 示 起 步 价

(

本 次 设 计 为

8.0

元

),

行程在

3km

以内

,

按起步价收费

;

当行驶超过

3km

,

1.6

元

/

km

,

车暂时停车

(

如遇红绿灯或中途暂时

停车

),

当等待时间超过

3min

,

按

1

元

/

min

收费

。

1.2

实现显示功能

能动态显示出租车行驶的里程

,

范围为

00

~

99km

(

考虑到出租车就在市区或近郊附近活动

),

同时显示等

待时间

,

范 围 为

00

~

59 min

,

显 示 总 计 价 值

,

范 围 为

00

~

999.9

元

,

计价分辨率为

0.1

元

。

2

出租车计价系统的设计体系

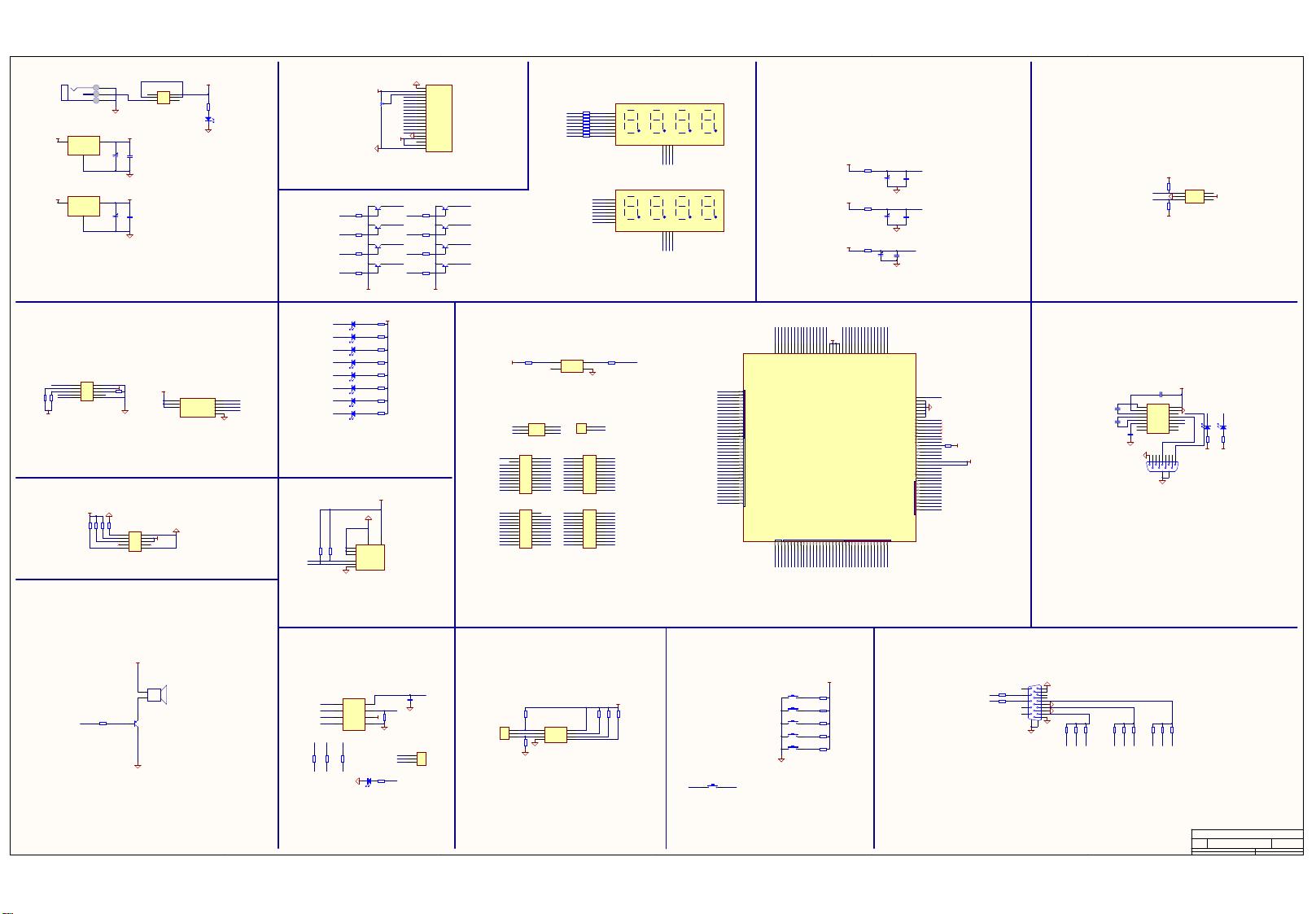

图

1

为整个系统的 顶层框图

,

根据层次化设计理

论

[

3

]

,

将出租车自动计价系统自顶向下可分为分频模

块

、

控制模块

、

计量模块

、

译码和动态扫描显示模块

。

图

1

系统的顶层框图

(

1

)

分频模块

。

通过分 频

[

4

]

产生不同频率的脉冲

信号用来实现系统的计费

,

本次设计中通过对

240 Hz

的输 入 脉 冲 进 行

15

次

,

24

次 和

240

次 分 频

,

得 到

16Hz

,

10 Hz

和

1 Hz

的三种频率

,

分别用 于

1.6

元

,