GMII to RGMII v4.1

LogiCORE IP Product Guide

Vivado Design Suite

PG160 January 21, 2021

GMII to RGMII v4.1 2

PG160 January 21, 2021 www.xilinx.com

Table of Contents

IP Facts

Chapter 1: Overview

Navigating Content by Design Process . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

About the Core. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

Feature Summary. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

Applications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

Unsupported Features. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

Licensing and Ordering . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

Chapter 2: Product Specification

Standards . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

Performance. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Resource Utilization. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Port Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

MDIO Management System . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Register Space . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Chapter 3: Designing with the Core

General Design Guidelines . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

Shared Logic . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

Clocking. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

Resets . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

Protocols. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

Chapter 4: Design Flow Steps

Customizing and Generating the Core . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

Constraining the Core . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

Simulation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

Synthesis and Implementation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

Chapter 5: Example Design

External Clocking . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

Internal Clocking . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

Send Feedback

GMII to RGMII v4.1 3

PG160 January 21, 2021 www.xilinx.com

Top-Level Example Design HDL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

Chapter 6: Test Bench

Demonstration Test Bench . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

Customizing the Test Bench . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

Appendix A: Upgrading

Migrating to the Vivado Design Suite. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

Upgrading in the Vivado Design Suite . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

Appendix B: Debugging

Finding Help on Xilinx.com . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

Debug Tools . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

Simulation Debug. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

Hardware Debug . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

Appendix C: Additional Resources and Legal Notices

Xilinx Resources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

Documentation Navigator and Design Hubs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

References . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

Please Read: Important Legal Notices . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

Send Feedback

GMII to RGMII v4.1 4

PG160 January 21, 2021 www.xilinx.com Product Specification

GMII to RGMII v4.1GMII to RGMII v4.1

Introduction

The Xilinx

®

LogiCORE™ IP Gigabit Media

Independent Interface (GMII) to Reduced

Gigabit Media Independent Interface (RGMII)

core provides the RGMII between RGMII

Ethernet physical media devices (PHY) and the

Gigabit Ethernet controller (GEM) in the

Zynq

®

-7000 SoCs, Gigabit Ethernet soft IP in

Versal™ device, and Zynq

®

UltraScale+™

MPSoCs. This core can be used in all three

modes of operation (10/100/1000 Mb/s). The

Management Data Input/Output (MDIO)

interface is used to determine the speed of

operation. This core can switch dynamically

between the three different speed modes.

Features

• Tri-speed (10/100/1000 Mb/s) operation

• Full-duplex operation

• MDIO interface to set operating speed and

duplex mode by MAC

G

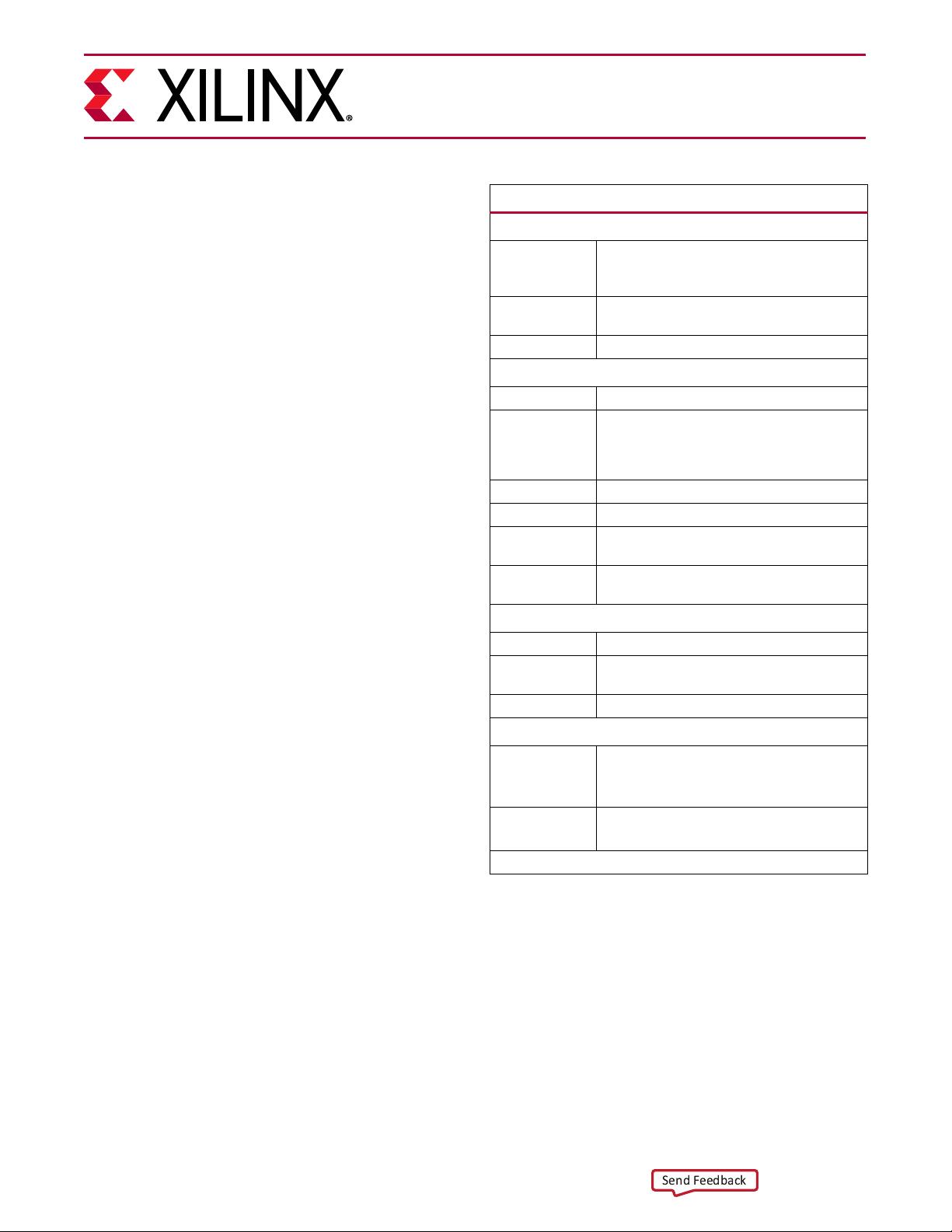

IP Facts

LogiCORE IP Facts Table

Core Specifics

Supported

Device Family

(1)

Zynq

®

UltraScale+™ MPSoC,

Zynq

®

-7000 SoC,

Versal™ device

Supported User

Interfaces

GMII

Resources Performance and Resource Utilization web page

Provided with Core

Design Files Encrypted RTL

Example Design

GMII to RGMII with internally

generated GMII clock

GMII to RGMII with externally

generated GMII clock

Test Bench Demonstration Test Bench

Constraints File XDC

Simulation

Model

Not Provided

Supported

S/W Driver

N/A

Tested Design Flows

(2)

Design Entry Vivado

®

Design Suite

Simulation

For supported simulators, see the

Xilinx Design Tools: Release Notes Guide.

Synthesis Vivado Synthesis

Support

Release Notes

and Known

Issues

Master Answer Record 54689

All Vivado IP

Change Logs

Master Vivado IP Change Logs 72775

Provided by Xilinx at the Xilinx Support web page

Notes:

1. For a complete list of supported devices, see the Vivado

IP catalog.

2. For the supported versions of the tools, see the

Xilinx Design Tools: Release Notes Guide.

Send Feedback

GMII to RGMII v4.1 5

PG160 January 21, 2021 www.xilinx.com

Chapter 1

Overview

Navigating Content by Design Process

Xilinx® documentation is organized around a set of standard design processes to help you

find relevant content for your current development task. This document covers the

following design process:

• Hardware, IP, and Platform Development: Creating the PL IP blocks for the hardware

platform, creating PL kernels, subsystem functional simulation, and evaluating the

Vivado® timing, resource use, and power closure. Also involves developing the

hardware platform for system integration. Topics in this document that apply to this

design process include:

°

Port Descriptions

°

Register Space

°

Clocking and Resets

°

Customizing and Generating the Core

°

Constraining the Core

°

Chapter 5, Example Design

About the Core

The GMII to RGMII IP core provides the Reduced Gigabit Media Independent Interface

(RGMII) between Ethernet physical media devices and the Gigabit Ethernet controller in

Zynq®-7000 SoCs, Versal™ devices, and Zynq® UltraScale+™ MPSoCs. This core can switch

dynamically between the three different speed modes of operation (10/100/1000 Mb/s).

Feature Summary

• Tri-speed operation (10/100/1000 Mb/s)

Send Feedback

评论5