possessor pursuant to the possessor's agreement to do the following:

of National Instruments Corporation. This proprietary information is supplied to the

This document contains confidential and proprietary information which is the property

2. not to reproduce, publish or copy it in whole or in part without written

1. to maintain this document in confidence;

3. not to use this document as a basis for the manufacture or sale of goods

without written permission.

permission; and

C

D

B

C

D

4

3 2 1

B

A

123

4

A

SCALE: NONE

C 7U296

SIZE CODE IDENT NO. DRAWING NO. REV

c

COPYRIGHT

SHEET OF

NATIONAL INSTRUMENTS CORP. ALL RIGHTS RESERVED.

146456B-01 0

21

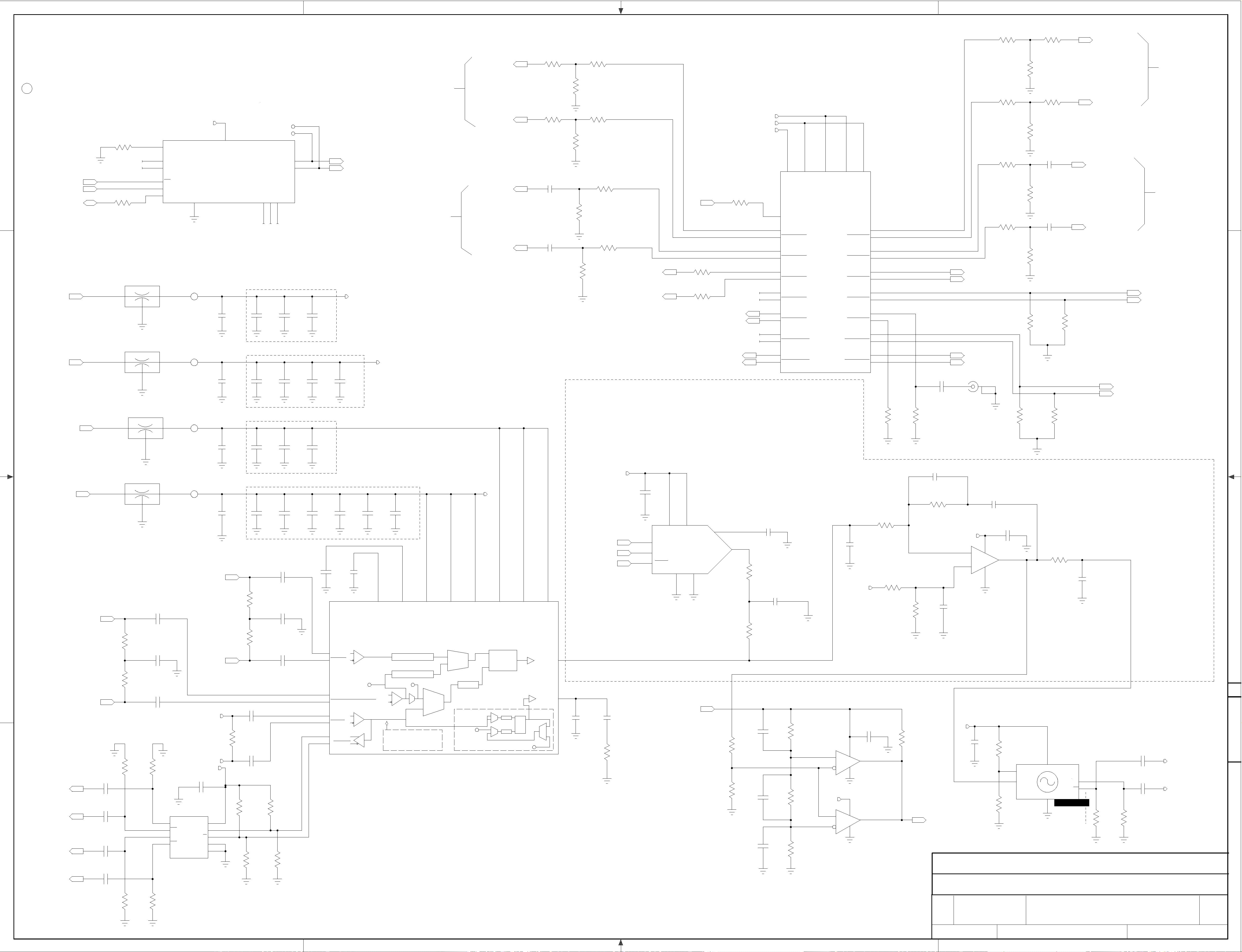

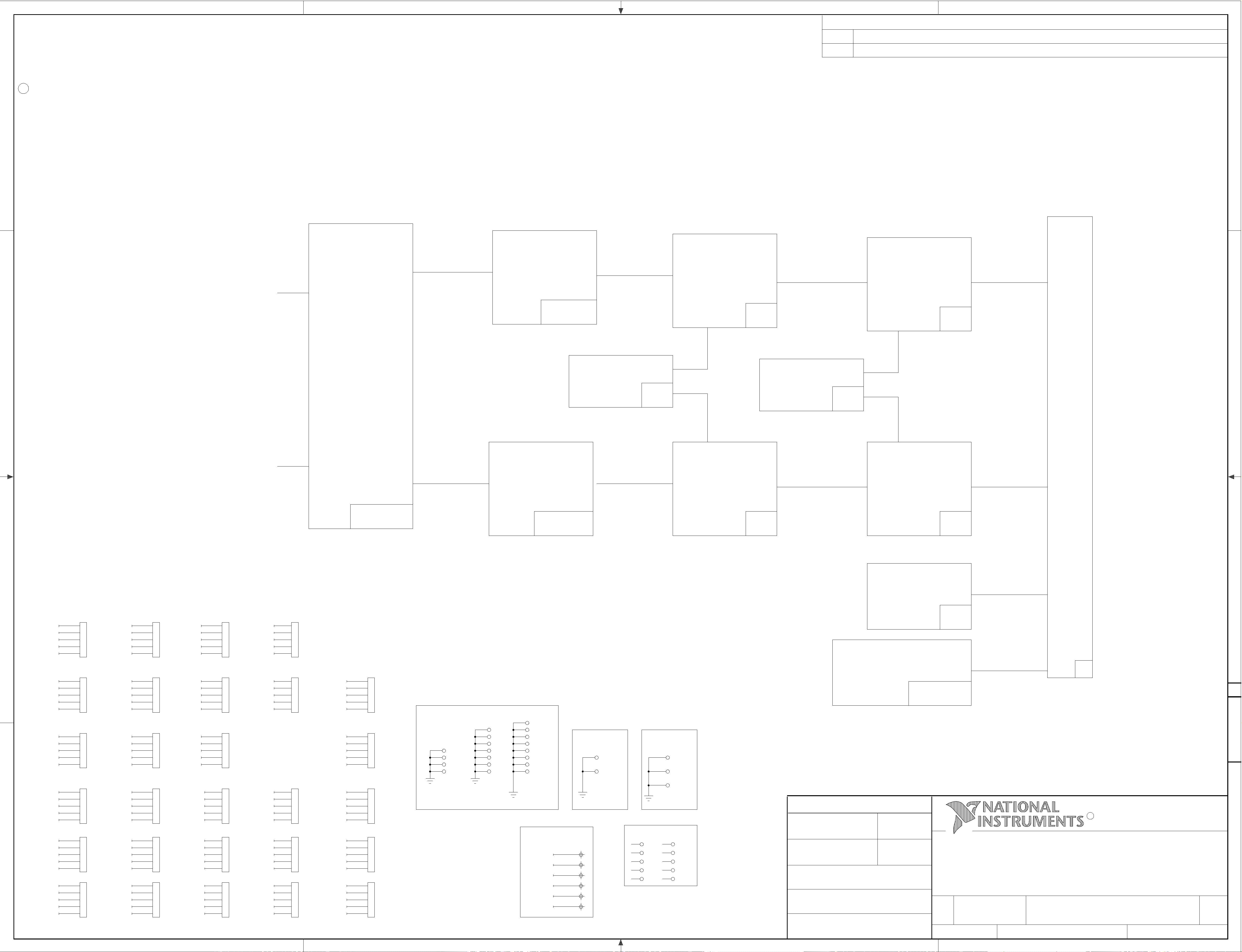

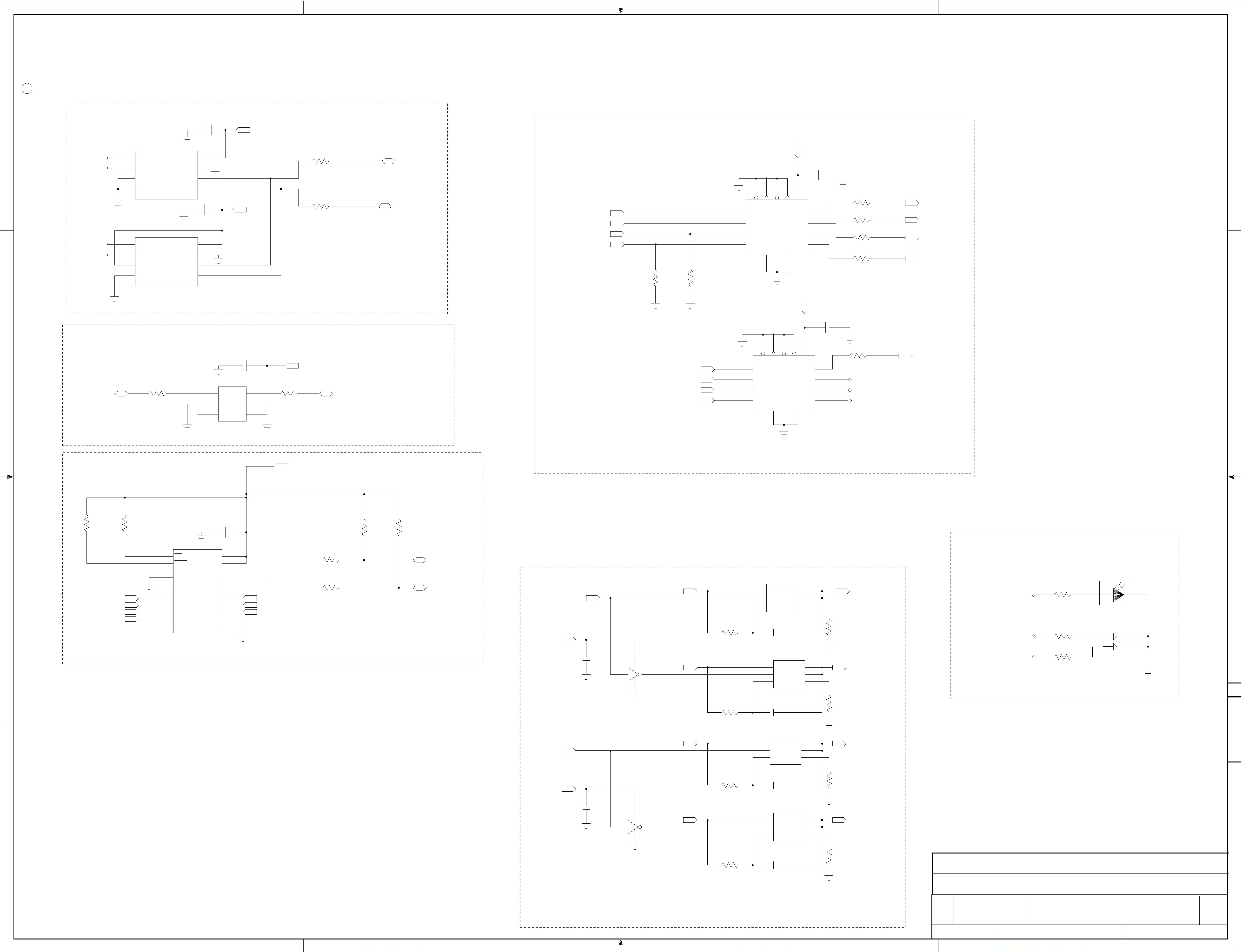

Clock Distribution

N320/N321 6GHz Transceiver

2018

RESET

CLKin_SEL0

CLKin_SEL1

CS

SCK

SDIO

Status_LD1

Status_LD2

Vcc5_DIG

NC-1

NC-2

NC-3

Thermal

Device Control

LMK04828BISQ

CLKin0

CLKin0

CLKin1/FIN/FBCLKin

CLKin1/FIN/FBCLKin

CPout1

OSCin

OSCin

OSCout

OSCout

CPout2

Vcc6_PLL1

Vcc1_VCO

Vcc8_OSCin

Vcc7_OSCout

Vcc10_PLL2

Vcc9_CP2

LDObyp1

LDObyp2

Mux

N

LMK04828BISQ

CLKin

ExtVCO

MUX

or

Feedback for PLL1

Ref CLK for PLL2

Divider

CLKin1 Divider

Detector

FBMux

ExtVCO

CLKin0 Divider

PLL2

FBMux

PLL1

PLL BLOCK

Phase

PLL1

SYNC

SDCLKout1

SDCLKout1

SDCLKout3

SDCLKout3

SDCLKout5

SDCLKout5

SDCLKout7

SDCLKout7

SDCLKout9

SDCLKout9

SDCLKout11

SDCLKout11

SDCLKout13

SDCLKout13

DCLKout0

DCLKout0

DCLKout2

DCLKout2

DCLKout4

DCLKout4

DCLKout6

DCLKout6

DCLKout8

DCLKout8

DCLKout10

DCLKout10

DCLKout12

DCLKout12

VCC12_CG0

Vcc2_CG1

Vcc4_CG2

Vcc11_CG3

Vcc3_SYSREF

LMK04828BISQ

OUTPUT

BLOCk

10%

16V

0.1UF

BLM18EG221

F

10%

16V

0.1UF

10%

16V

0.1UF

10%

16V

0.1UF

BLM18EG221

F

10%

16V

0.1UF

10%

16V

0.1UF

10%

16V

0.1UF

10%

16V

0.1UF

10%

16V

0.1UF

10%

16V

0.1UF

BLM18EG221

F

10%

16V

0.1UF

10%

16V

0.1UF

10%

16V

0.1UF

10%

16V

0.1UF

BLM18EG221

F

10%

16V

0.1UF

10%

16V

0.1UF

10%

16V

0.1UF

1/16W

1K 1%

UFLRSMT

10%0.1UF

16V

Vc

En

GND

Out

Out

Vcc

122.88 MHz

347LB5C1227

1/16W

0 1%

10, 20, or 30 MHz REF input (LVPECL)

for PLL1. Originates at N310 MB and

is supplied to DB via LPAF connector.

This interface is leveraged from the

EISCAT daughterboard.

30.72 MHz REF input (CPRI, LVDS)

for PLL1. Originates at N310 MB

and is supplied to DB via LPAF

connector. This interface is leveraged

from the EISCAT daughterboard.

The output of the external VCXO (LVPECL) is fed back to the LMK04828 as

the "clean" REF input for PLL2. This interconnection circuitry is taken from

the LMK04828 vendor data sheet (p. 96) for LVPECL interfaces.

OSCout provides a buffered copy of OSCin. The output type is programmable to LVDS,

LVPECL, or LVCMOS. NOTE: This port shares functionality with CLKin2, but is not used

in this implementation.

PLL2 LOOP

FILTER

Internal resistor and

capacitor values may be

programmatically selected

from a fixed range of

values to achieve the

desired 3rd- or 4th-order

loop filter response for

PLL2. These internal

components

complement the

external components

mounted near the IC,

as shown here.

The PLL2 loop filter was designed using the TI CLK Design Tool specifically for use

with the LMK04828. It is a 4th-order filter and takes advantage of the internal,

programmable resistors and capacitors.

R3 = R4 = 0.2 kOhm

C3 = C4 = 0.01 nF

Output R2 N2 PLL2 PDF

VCO Loop BW Loop PM

----------------------------------------------------

400 MHz 32 625 (5*125) 3840 kHz 2400 MHz 76.1 kHz 71.2 deg

491.52 MHz 32 640 (2*320) 3840 kHz 2457.6 MHz 79.7 kHz 71.5 deg

500 MHz 128 3125 (5*625) 960 kHz 3000 MHz 20.1 kHz 45.6 deg

The vendor data sheet indicates that

these pins must be bypassed to GND

with the capacitor values shown here.

No details were provided on the func-

tion of these pins or the required vol-

tage rating for these components.

Icc6(MAX)=27mA

Icc8(MAX)=10mA

Icc7(MAX)=52mA

Icc1(MAX)=68mA

Icc10(MAX)=72mA

Icc9(MAX)=19mA

3.3V, LMK, LDO "C"

Icc(MAX)=159mA (est)

2A (0603)

DCR=0.05 Ohms

LAYOUT: Place each capacitor near the

downstream Vcc pins (one per pin).

2A (0603)

DCR=0.05 Ohms

3.3V, LMK, LDO "D"

Icc(MAX)=224mA (est)

LAYOUT: Place each capacitor near the

downstream Vcc pins (one per pin).

to Vcc3, Vcc5, VCXO (CTS345)

Icc5(MAX)=2mA

Icc3(MAX)=68mA

3.3V, LMK, LDO "B"

Icc(MAX)=262.7mA (est)

LAYOUT: Place each capacitor near the

downstream Vcc pins (one per pin).

to Vcc11, Vcc12

3.3V, LMK, LDO "A"

Icc(MAX)=297.7mA (est)

2A (0603)

DCR=0.05 Ohms

LAYOUT: Place each capacitor near the

downstream Vcc pins (one per pin).

to Vcc2, Vcc4

Icc12(MAX)=47.9mA (est)

Icc2(MAX)=116.3mA (est)

Icc4(MAX)=198.2mA (est)

Icc3(MAX)=198.1mA (est)

122.88 MHz

VCXO

Configurable Test

Output

Per data sheet, these "NC"

pins must be left floating.

2A (0603)

DCR=0.05 Ohms

Can be programmed to monitor a variety of

aspects, but is primarily used for lock detect

of PLL1 and PLL2.

C2 = 1.8 nFC1 = 0.018 nF

CTS345 122.88-MHz VCXO EN Truth Table:

Logic '1' output

Logic '0' high impedance

Open (N/C) output

0 Ohm to VCC for output; 1 MOhm to GND

for option to disable during turn-on & debug.

LO SYNC, LVDS

59

20

18

5

58

19

31

U19

65

9

33

8

48

7

U19

12

42

10

46

40

44

43

34

38

11

37

39

45

32

47

36

41

35

4

6

26

63

17

51

25

16

55

24

15

61

49

1

53

29

23

52

28

13

U19

27

60

21

64

62

54

2

57

56

50

30

22

14

3

10V

C135

10UF

20%

2

1

C134

1

2

L75

21

C469

2

1 1

2

C496

2

1

C486

L74

21

C470

2

1 1

C664

2

1

C449

2

1

2

C471 C485

2

1 1

C447

2

1 2

L26

C495

2

1 1

2

C662

1

2

C160 C660

2

1

1

L19

2

1

2

C448 C446

1

2

1

2

C659

R348

2 1

1 3

J10

2

C159

21

2

R175

1/16W

240

0.5%

1

1

3

2

5

4

6

U26

R358

1

2

2

R366

1/16W

1

1M

1%

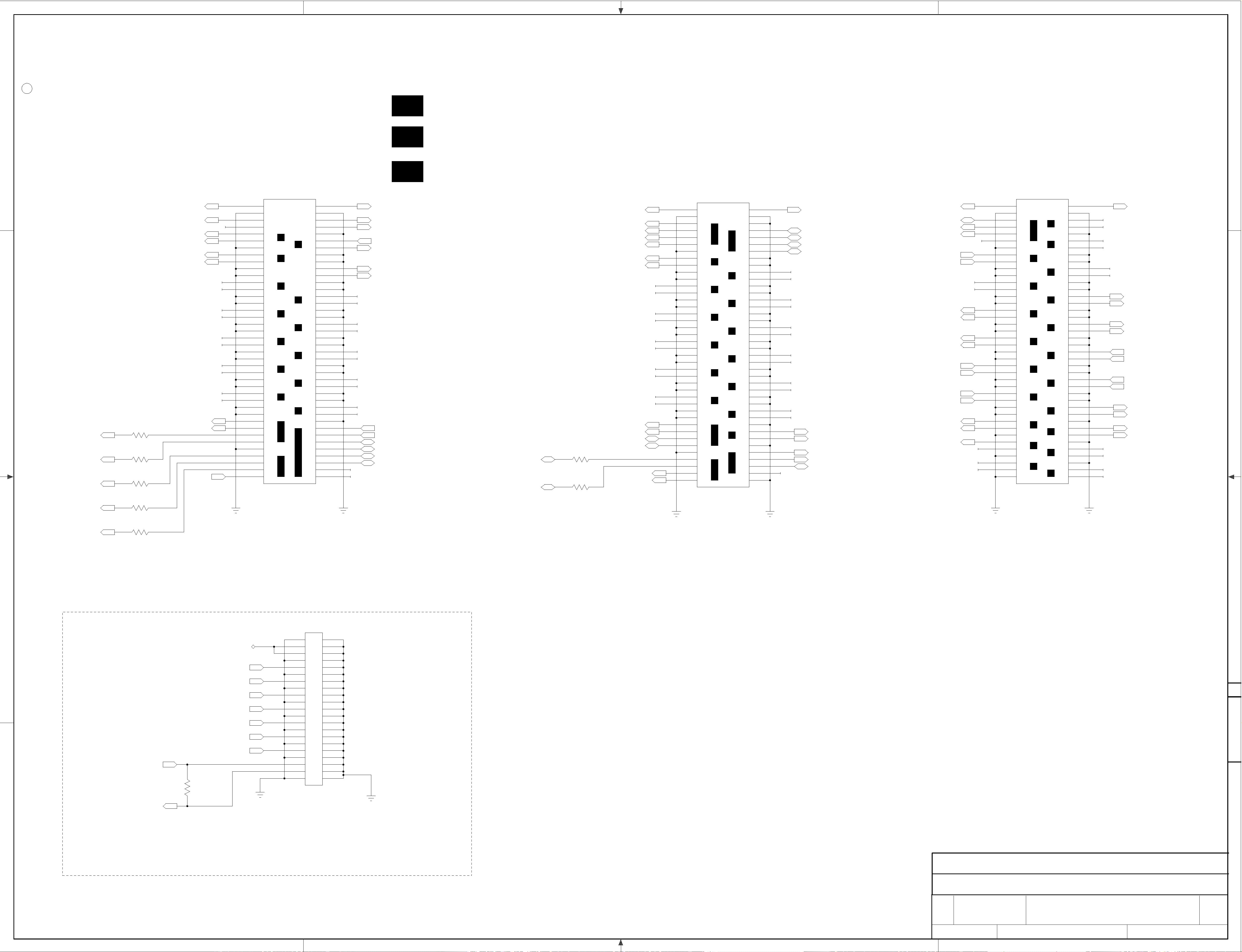

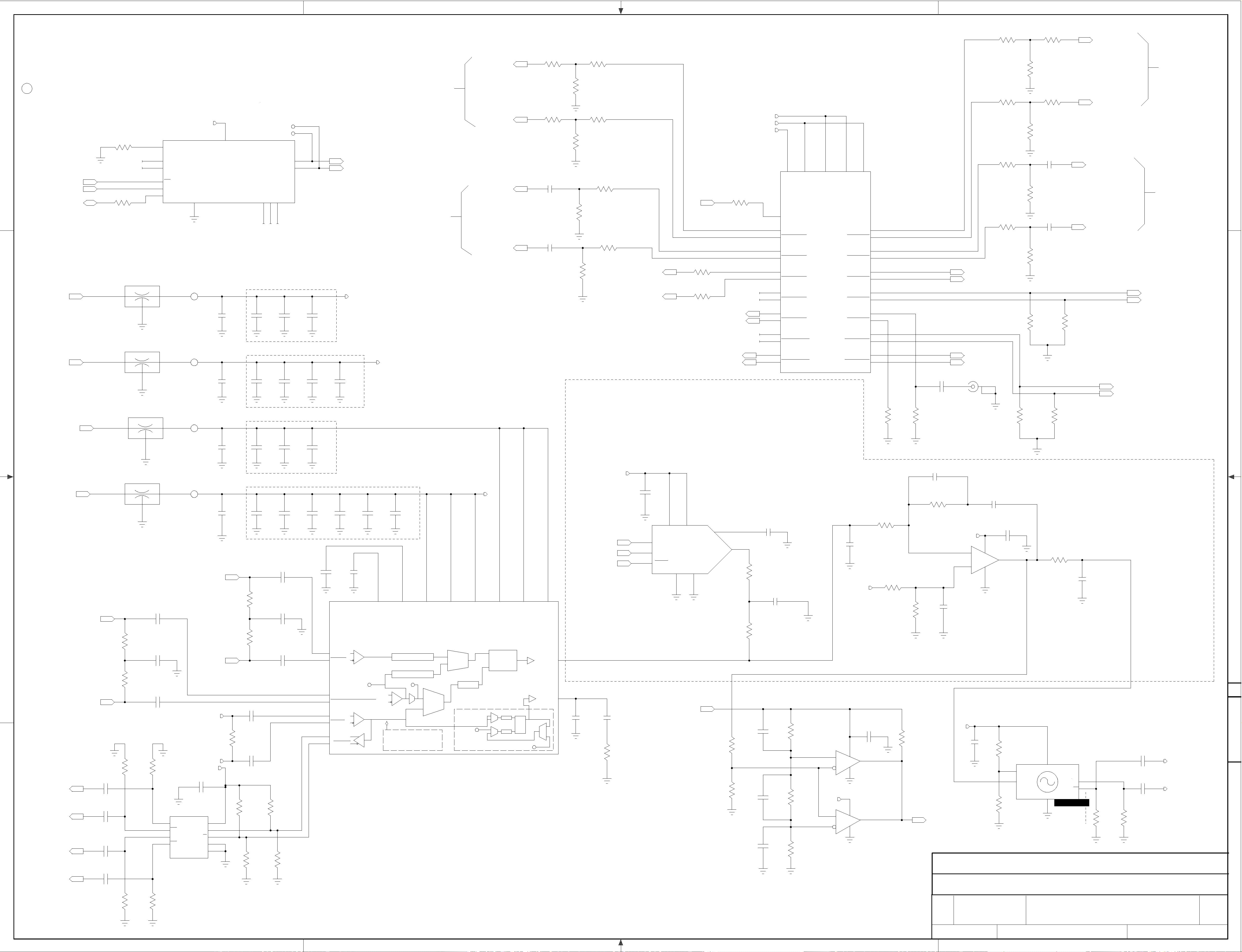

CLKDIST-PLL1-VCXOin

RF_122p88MHzOut_FromCLKDIST_P

CLKDIST-CPout2

3p3V_CLKDIST_LDOC_filt

3p3V_CLKDIST_LDOD_filt

3p3V_CLKDIST_LDOD_filt

3p3V_CLKDIST_LDOD_filt

3p3V_CLKDIST_LDOB_filt

3p3V_CLKDIST_LDOA_filt

3p3V_CLKDIST_LDOB_filt

3p3V_CLKDIST_LDOA_filt

CLKDIST_DAC_DCLK_p

CLKDIST_DAC_DCLK_n

CLKDIST_DAC_SYSREF_p

CLKDIST_DAC_SYSREF_n

CLKDIST_LBLO_TX_p

CLKDIST_LBLO_TX_n

CLKDIST_ADC_SYSREF_p

CLKDIST_ADC_SYSREF_n

CLKDIST_LBLO_RX_p

CLKDIST_LBLO_RX_n

CLKDIST_TestOut_n

CLKDIST_SYNC

NC_LMK_NC1

NC_LMK_NC2

NC_LMK_NC3

CLKDIST_SPI_CS_L

CLKDIST_SPI_SCLK

CLKDIST_Status_LD1

CLKDIST_Status_LD2

NC_LMK_CLKinSEL0

_NCLMK_CLKinSEL1

CLKDIST-CPout1

CLKDIST_TestOut_p

3p3V_CLKDIST_LDOD_filt

LO_SYNC_P

LO_SYNC_N

NC_SDCLKout7p

NC_SDCLKout7n

NC_SDCLKout11p

NC_SDCLKout11n

3p3V_CLKDIST_LDOD_filt

RF_LMK-PLL1-VCXOout_p

RF_LMK-PLL1-VCXOout_n

1%

1/16W33.2

2

R92

1

CLKDIST_SPI_SDIO

P3_3V_CLKDIST_A

P3_3V_CLKDIST_B

P3_3V_CLKDIST_C

P3_3V_CLKDIST_D

R450

2

1

169

0.5%

1/16W

R456

2

1

169

0.5%

1/16W

R309

2

1

169

0.5%

1/16W

R310

2

1

169

0.5%

1/16W

10%0.1UF

16V

C121

21

10%0.1UF

16V

C132

21

10%0.1UF

16V

1 2

C133

USRPIO_RefClk_P

USRPIO_RefClk_N

10%0.1UF

16V

C120

21

CPRI_REFCLK_P

CPRI_REFCLK_N

1

2

0.5%

240

1/16W

R151

1

2

0.5%

240

1/16W

R174

10%0.1UF

16V

C157

21

10%0.1UF

16V

C158

21

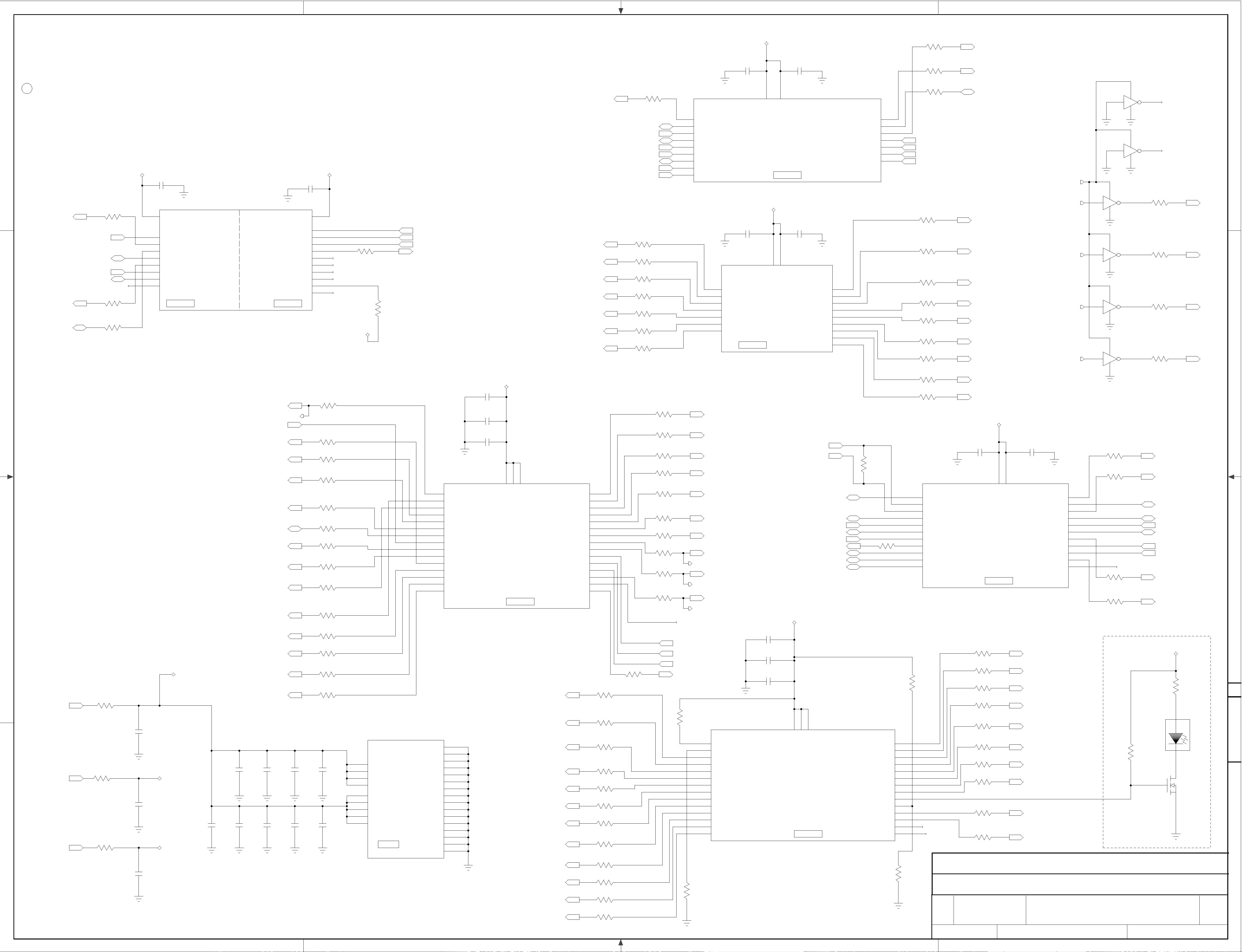

RF_LMK-PLL1-VCXOout_n

RF_LMK-PLL1-VCXOout_p

to LMK04828

OSCin

100, .5%

1/16W

1

2

R134

10%0.1UF

16V

C143

21

10%0.1UF

16V

C144

21

RF_LMK-PLL1-VCXOout_p

RF_LMK-PLL1-VCXOout_n

from VCXO

output

This interconnection circuitry is taken

from the LMK04828 vendor data sheet

(p. 96) for LVPECL interfaces.

to REF IN of

LMX2592 ICs

RF_Tx_LO_REFin_p

0 1%

1/16W

1 2

R111

0 1%

1/16W

1 2

R112

1

2

0.5%

240

1/16W

R325

1

2

0.5%

240

1/16W

R326

C123

21

0.01UF 10%

50V

C122

21

0.01UF 10%

50V

USRPIO_MGTCLK_P

USRPIO_MGTCLK_N

1

2

1/16W

0.5%

169

R355

R153

21

71.5

0.5%

1/16W

0 1%

1/16W

1 2

R156

USRPIO_DEVCLK_N

1

2

1/16W

0.5%

169

R356

R154

21

71.5

0.5%

1/16W

0 1%

1/16W

1 2

R157

USRPIO_DEVCLK_P

1

2

1/16W

0.5%

169

R347

R136

21

71.5

0.5%

1/16W

0 1%

1/16W

1 2

R137

USRPIO_SYSREF_N

1

2

1/16W

0.5%

169

R354

R152

21

71.5

0.5%

1/16W

0 1%

1/16W

1 2

R155

USRPIO_SYSREF_P

2

240

0.5%

1

1/16W

R357

NOTE: The "P" and the "N" signals are intentionally

swapped here to avoid cross-over in the layout

when interfacing with the downstream LMK04828.

10%0.1UF

16V

10%0.1UF

16V

0 1%

1/16W

R109

49.9

1/16W

0.5%

2

1

R110

49.9

1/16W

0.5%

2

1

C450

21

R122

49.9

1/16W

0.5%

2

1

R123

49.9

1/16W

0.5%

2

1

C472

21

TPS7

1

TPS8

1

R135

21

CLKDIST_ADC_DCLK_p

CLKDIST_ADC_DCLK_n

IN/OUT

OUT/IN

GND

4700 PF,25V, +/-20%

YFF15SC1E472MT

C467

2

31

IN/OUT

OUT/IN

GND

4700 PF,25V, +/-20%

YFF15SC1E472MT

C165

2

31

IN/OUT

OUT/IN

GND

4700 PF,25V, +/-20%

YFF15SC1E472MT

C433

2

31

3p3V_CLKDIST_LDOD_filt3p3V_CLKDIST_LDOD_filt

10%

16V

0.1UF

C487

2

1

PHDAC_SPI_SDI

PHDAC_SPI_SCLK

PHDAC_SPI_CS_L

PLL1 Active Loop Filter & Phase-Adjust DAC

-IN

+IN

V-

V+

AD8605ART

U70

5

1

2

3

4

10%0.1UF

16V

C499

21

3p3V_CLKDIST_LDOD_filt

3p3V_CLKDIST_LDOD_filt

0.5%

20K

1/16W

R173

2

1

1/16W

0.5%20K

R172

21

IN/OUT

OUT/IN

GND

4700 PF,25V, +/-20%

YFF15SC1E472MT

C101

2

31

R369

21

330

1/16W

1%

15K, .5%

1/16W

R368

21

R367

21

1.6K

0.1%

1/16W

AD5683R-1

VDD

VLogic

VOUT

SYNC

SCLK

GND

SDI

VREF

ThemGND

U68

9

7

6

3

4

5

8

21

16-BIT

R371

2

1

576K

0.5%

1/10W

R493

2

1

576K

0.5%

1/10W

C497

2

1

18PF

1%

50V

C498

2

1

1800PF

5%

50V

R2 = 4.7 kOhm

R385

2

1

4.7K

0.5%

1/16W

IN+

IN-

VCC

GND

OUT

U96

7

4

8

6

5

LM2903DGKR

IN+

IN-

VCC

GND

OUT

U96

1

4

8

2

3

LM2903DGKR

10%0.1UF

16V

C739

21

R494

2

1

5.1K

5%

1/16W

P3_3V_USRPIOP3_3V_USRPIO

R495

2

1

13.3K

0.5%

1/16W

R496

2

1

5.49K

0.5%

1/16W

R497

2

1

1.2K

0.5%

1/16W

10%

16V

0.1UF

C740

2

1

10%

16V

0.1UF

C741

2

1

10%

16V

0.1UF

C742

2

1

R498

2

1

10K

0.1%

1/16W

R499

2

1

6.49K

1/16W

0.5%

LMK_PLL1_Lock_Detect

Comparator_In

Comparator_In_Scaled

VTH

VTL

Output of op-amp scaled down to

0V-1.3V to comply with comparator.

VTH = 1.1

VTL = 0.2

Pull-up set to provide approximately

0.65 mA of current.

See IC data sheet for

layout guidelines.

Open-collector outputs

connected as "wired AND."

Parallel capacitors of equal value

across each divider resistor are

recommended by TI to reduce

noise and improve speed.

LVDS

LVDS

LVPECL

NET2CLK_P

NET2CLK_N

R507

2

1

127

0.5%

1/16W

R508

2

1

127

0.5%

1/16W

R527

2

1

82.5

0.5%

1/16W

R528

2

1

82.5

0.5%

1/16W

3p3V_CLKDIST_LDOD_filt

Q0

Q0

Q1

Q1

VCC

D

D

VEE

VEE_PAD

U99

9

5

6

7

8

4

3

2

1

MC100LVEP11MNR4G

RF_Tx_LO_REFin_n

RF_Rx_LO_REFin_p

RF_Rx_LO_REFin_n

1

2

R523

169

0.5%

1/16W

1

2

R524

169

0.5%

1/16W

R525

2

1

169

0.5%

1/16W

R526

2

1

169

0.5%

1/16W

10%0.1UF

16V

C743

21

10%0.1UF

16V

C744

21

10%0.1UF

16V

C745

21

10%0.1UF

16V

C746

21

ADD CES FOR DIFF PAIRS

5N4869

5N4942

5N7009

P3_3V_USRPIO

C510

21

50V

5%0.01uF

COG Capacitor

C738

21

0.022UF 5%

50V

C164

2

1

0.1UF

5%

25V

COG Capacitor

COG Capacitor

C507

2

1

16V

20%

1.0UF

Film Capacitor

C519

21

16V

20%1.0UF

Film Capacitor

COG Capacitor

C508

21

0.022UF 5%

50V

C509

2

1

2200PF

5%

50V

COG Capacitor

C142

2

1

10uF

20%

6.3V

C166

2

1

10uF

20%

6.3V

C424

2

1

10uF

20%

6.3V

C434

2

1

10uF

20%

6.3V

C468

2

1

10uF

20%

6.3V

LVPECL

C751

21

0.01UF 10%

50V

C752

21

0.01UF 10%

50V

0 1%

1/16W

R512

21

0 1%

1/16W

R511

21

R522

2

1

240

0.5%

1/16W

R521

2

1

240

0.5%

1/16W

This analog lock-detect circuit was placed in

in the design in case the digital lock detect does

not function properly.

R545

21

33.2

1%

1/20W

R546

21

33.2

1%

1/20W

5

These signals are LVDS but must

be ac-coupled per the data sheet

for the LMK04828.

7

8

9

2

2

2

7

9

20

99

2

2

2

3

3

2

2

2

22

2

20

3

3

8

3

3

4

22

22

22

3

20

20

6

6

6

6

3

3

3

4

2

2

2,22,23,4

10%

16V

0.1UF

1

2

C766

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜

信息提交成功

信息提交成功