没有合适的资源?快使用搜索试试~ 我知道了~

资源推荐

资源详情

资源评论

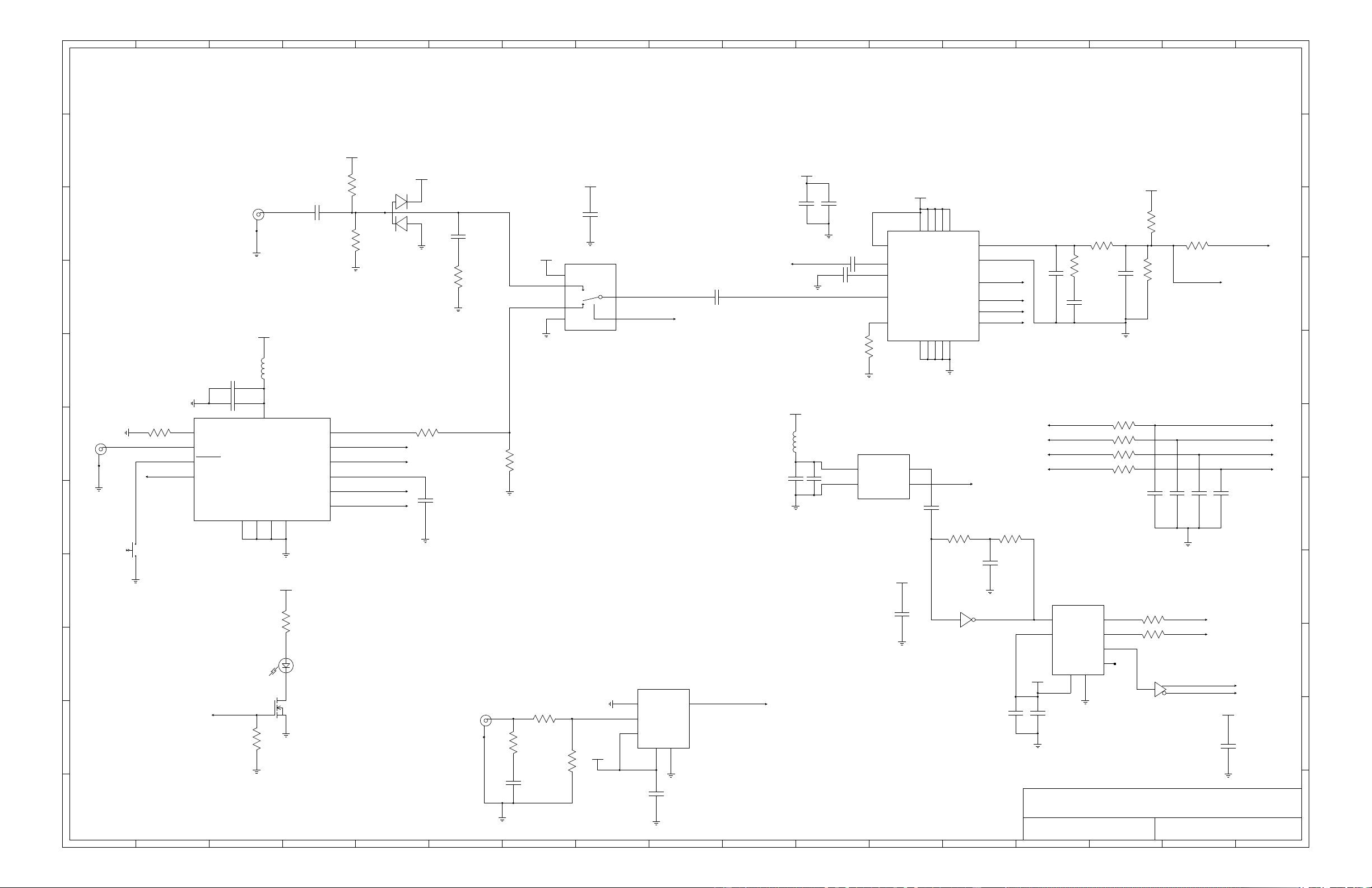

B200 Clock

clock.sch 2

nick, matt

FILE: REVISION:

DRAWN BY: PAGE OF

TITLE

H

G

F

E

D

C

B

A

I

J

K

I

J

K

H

G

F

E

D

C

B

A

1 2 3 4 5 6 7 8 9 10 11

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17

12 13 14 15 16 17

1 8

2

1

345

J100

142−0701−871

C100

0.1uF

SMA External Reference

2

1

345

J104

142−0701−871

PPS_IN_EXT

R102

49.9

R103

1K

3.3V_CLK:1

C103

1000pF

3

A

1

B

6

C

4

Y

5

Vcc

2

GND

SN74AUP1T57

U102

R104

2K

xo_out

3.3V_CLK:1

C105

10uF X5R 6.3V

C109

0.1uF

External PPS

input

PPS_IN_INT

1

GND

2

10MHz_Out

3

Lock_OK

4

PPS_Out

5

PPS_In

6

5V_Out

7

GND

8

3.3V_In

9

GND

10

Antenna

11

GND

12

NMEA_Out

13

Enter_ISP

14

Serial_In

15

Serial_Out

M9107

U100

R100

4.7K

R106

100

gps_lock

C101 0.1uF

gps_txd

gps_rxd

2

1

345

J101

142−0701−871

GPSDO

C102 22uF X5R 6.3V

Q100

1 2

LED100

R108

150

3.3V:1

GPSDO lock LED

gps_lock

R109

10K

C108

47uF 6.3V X5R

C137

180pF

R124 100K

R125

47.0K 1%

C138

2.2nF

C139

82pF

Assume 400Hz/Volt

4kHz loop bandwidth

10MHz compare frequency

5mA CP current

reduce C139 by the load cap of trace + tune

Eff. Kv is adjusted based on the resistor div

formed by R124 and the impedance

of Cat DAC when disabled (if R118 installed)

ADF4001

19

Rset

20

CP

1

CPGND

2

AGND

3

AGND

4

RFIN_B

5

RFIN_A

6

AVDD

7

AVDD

8

REFIN

9

DGND

10

DGND

11

CE

12

SCLK

13

SDA

14

SLE

15

MUXOUT

16

DVDD

17

DVDD

18

VP

21

PAD

U101

3.3V_CLK:1

xo_to_pll

R111

4.7K

pll_sclk_filt

pll_mosi_filt

pll_ce_filt

C112

100pF

L107

MI1206K601R−10

pll_lock_filt

PLL bringup:

1. VCTCXO starts up

2. FX3 brings up transceiver, sets CLKOUT to FPGA

3. FX3 programs FPGA

4. FPGA writes to PLL, initializes PLL

5. PLL locks to external ref if avail.

6. If no ref, PLL tristated via SPI

C106

0.1uF

C107

0.1uF

3.3V_CLK:1

GPS

antenna

C150

0.1uF

L100

MI1206K601R−10

15dBm max. (3.5V into 50 ohms)

R118 DNP

auxdac1

gps_txd_nmea

1 2

S100

JLEAD_SW

LAYOUT:

R110 and C150 Should be close to U101

C151

0.1uF

xo_to_pll

Buffer to FPGA

Place near U104

4

3

5

FIN1001

U105

net=3.3V_CLK:1

net=GND:2

codec_main_clk_p

codec_main_clk_n

C116

0.1uF

C114

0.1uF

3.3V_CLK:1

Place at U105

To transceiver

5V max.

1

CLKIN

2

1G

3

Y0

5

Y2/NC

6

Vcc

4

GND

CDLVC1103PWR

7

Y3/NC

8

Y1/NC

U104

C113

0.1uF

3.3V_CLK:1

C110

10uF X5R 6.3V

3

OUT

1

ENB/TUNE

4

Vcc

2

GND

VCTCXO X100

R113 47

R119 47

R120

1M

R121

1M

3.3V_CLK:1

To PLL RF in

C117

0.1uF

3.3V_CLK:1

R122 510K R123 510K

C118

0.01uF

Place at U106

Self−biasing clock squarer

C119

470pF

2 4

SN74LVC1G04

U106

net=3.3V_CLK:5

net=GND:3

1

2

3

D100

3.3V_CLK:1

R128

10K

R126

10K

3.3V_CLK:1

4

A

6

S

5

Vcc

2

GND

DG4157DL

3

B0

1

B1

U103

ref_sel

3.3V_CLK:1

C111

0.1uF

3.3V_CLK:1

R127

150

R110

49.9

C104

0.1uF

3.3V:1

SN74LVC1G3157 works too

CONFIGURE PLL_LOCK AS OPEN DRAIN!

R101 2.2K

C115

470pF

pll_lock_filt

C120

470pF

C121

470pF

C122

470pF

R105 1K

R107 1K

R112 1K

pll_lock

pll_sclk

pll_mosi

pll_ce

pll_sclk_filt

pll_mosi_filt

pll_ce_filt

vcxo_tune

vcxo_tune

资源评论

东枫科技

- 粉丝: 5550

- 资源: 59

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功