SDRAM Controller Core n2cpu_nii51005

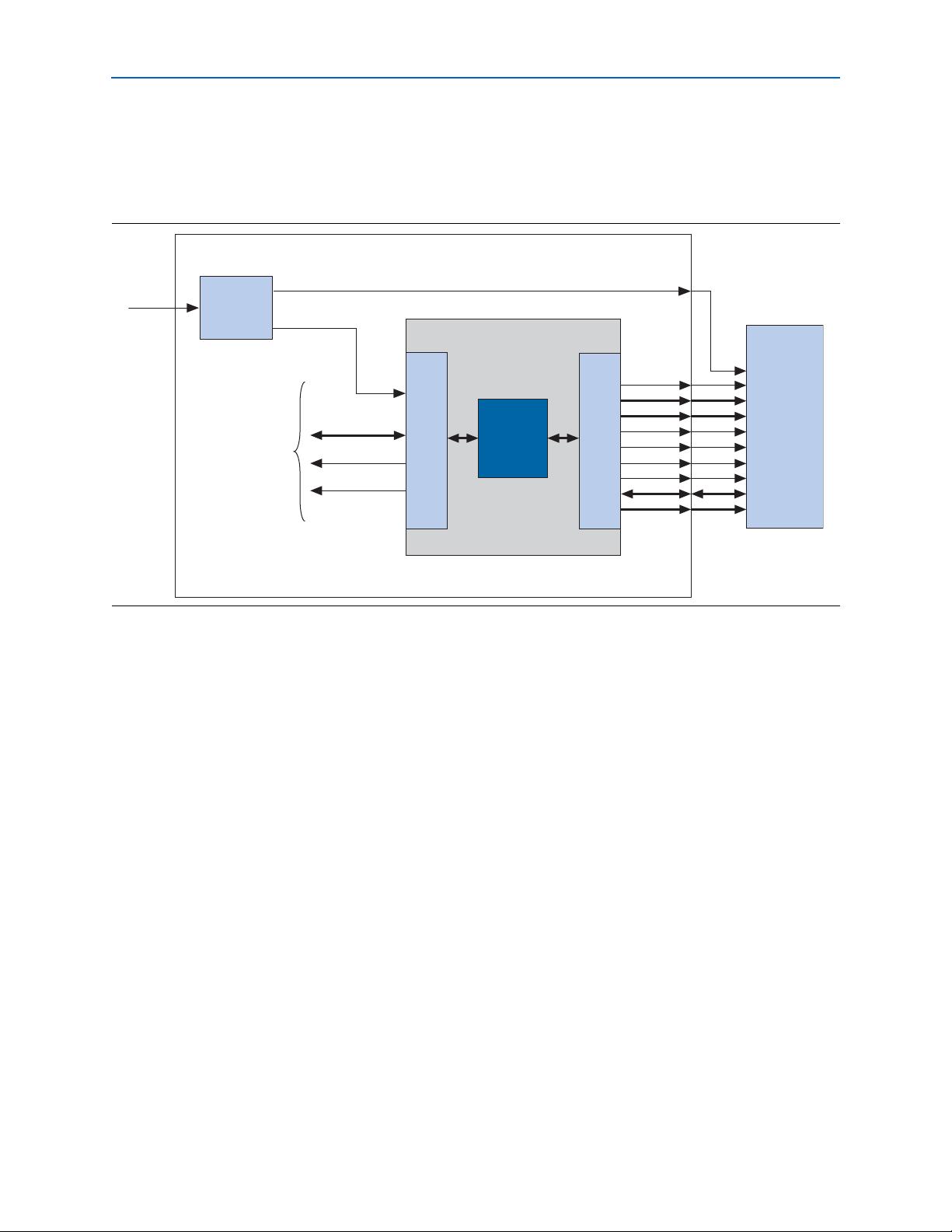

### SDRAM Controller Core n2cpu_nii51005:深入解析 #### 核心概述 SDRAM(同步动态随机存取存储器)在现代计算系统中扮演着至关重要的角色,尤其是在那些需要大量易失性内存且成本敏感的应用场景中。本章节将详细介绍Altera公司Quartus II Handbook Version 9.0 Volume 5中的SDRAM控制器核心n2cpu_nii51005。此控制器核心与Avalon接口集成,提供了连接外部SDRAM芯片的能力,并支持标准的SDRAM,如PC100规范所定义。 #### 功能描述 SDRAM控制器核心通过Avalon Memory-Mapped (Avalon-MM)接口与外部SDRAM进行通信。该核心允许设计者在其Altera设备内部创建自定义系统,这些系统能够轻松地与SDRAM芯片相连。SDRAM虽然价格相对较低,但需要复杂的控制逻辑来执行刷新操作、开行管理以及其他延迟和命令序列。SDRAM控制器核心能够处理所有这些协议需求,从而简化了设计过程。 在内部,该核心表现为一个Avalon-MM从端口,对于其他Avalon-MM主外围设备而言,它呈现出线性内存的形式(扁平地址空间)。这种设计使得控制器可以高效地管理内存访问。 #### 设备支持 SDRAM控制器核心支持各种数据宽度(8位、16位、32位或64位),以及不同大小的内存和多个芯片选择信号。Avalon-MM接口具有延迟感知能力,这意味着读取传输可以被流水线化处理,从而提高性能。此外,该核心还可以选择性地与其它外部Avalon-MM三态设备共享地址和数据总线,这对于I/O引脚数量有限而需要连接多个内存芯片的系统来说是一项非常有用的功能。 #### 在SOPC Builder中的实例化 SDRAM控制器核心是SOPC Builder就绪的,可以轻松地集成到任何由SOPC Builder生成的系统中。这使得开发人员能够快速地将其添加到复杂的设计中,而无需额外编写复杂的接口代码。 #### 硬件仿真考虑 为了确保设计的正确性和可靠性,在硬件实现之前进行仿真测试是非常重要的。本节讨论了在硬件仿真过程中需要注意的一些关键点,包括如何设置测试环境、如何配置SDRAM控制器核心及其外围设备,以及如何验证其功能是否符合预期。 #### 软件编程模型 除了硬件方面之外,软件编程也是成功实现SDRAM控制器的关键因素之一。本节将介绍如何通过软件来访问和控制SDRAM控制器核心,包括如何初始化控制器、如何配置SDRAM的工作模式等。 #### 时钟、PLL和定时考虑 时钟信号对于SDRAM控制器的正常工作至关重要。本节将探讨与SDRAM控制器相关的时钟、PLL(锁相环)和定时方面的问题,包括如何为SDRAM控制器提供稳定可靠的时钟源,以及如何解决由于时序偏差导致的问题。 #### 总结 SDRAM控制器核心n2cpu_nii51005是Altera公司提供的一个强大工具,旨在帮助设计者轻松地在FPGA中实现对SDRAM的有效管理。通过深入了解其功能特点和技术细节,设计者可以更好地利用这一资源来优化其系统的性能和效率。无论是对于初学者还是有经验的工程师来说,掌握这一核心都是十分有价值的。

剩余15页未读,继续阅读

- 粉丝: 0

- 资源: 1

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 为 Go 自动生成的 Google API .zip

- 一组快速入门示例,演示了适用于 Android 和 iOS 的 Google API.zip

- 一款简单但有效的 Go 网站迷你分析器.zip

- 一个线程安全的并发映射.zip

- 一个用于与任意 JSON 交互的 Go 包.zip

- 一个用于 go 的 cron 库.zip

- 基于BJUI + Spring MVC + Spring + Mybatis框架的办公自动化系统设计源码

- 基于百度地图的Java+HTML+JavaScript+CSS高速公路设备管理系统设计源码

- 基于Django Web框架的母婴商城实践项目设计源码

- 一个使用 Go 编程语言和 WebAssembly 构建渐进式 Web 应用程序的包 .zip

信息提交成功

信息提交成功