低功耗之门控时钟设计.docx

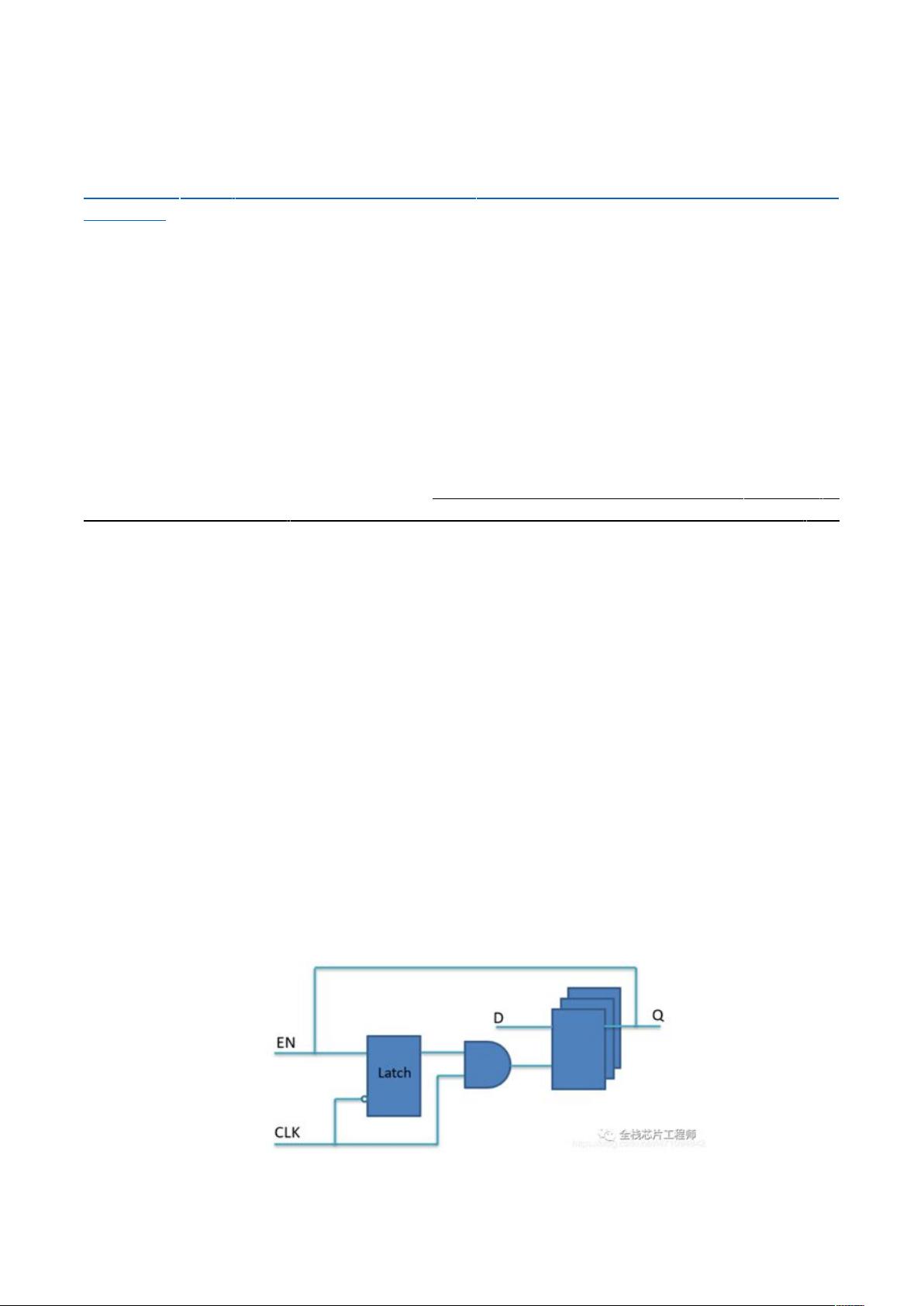

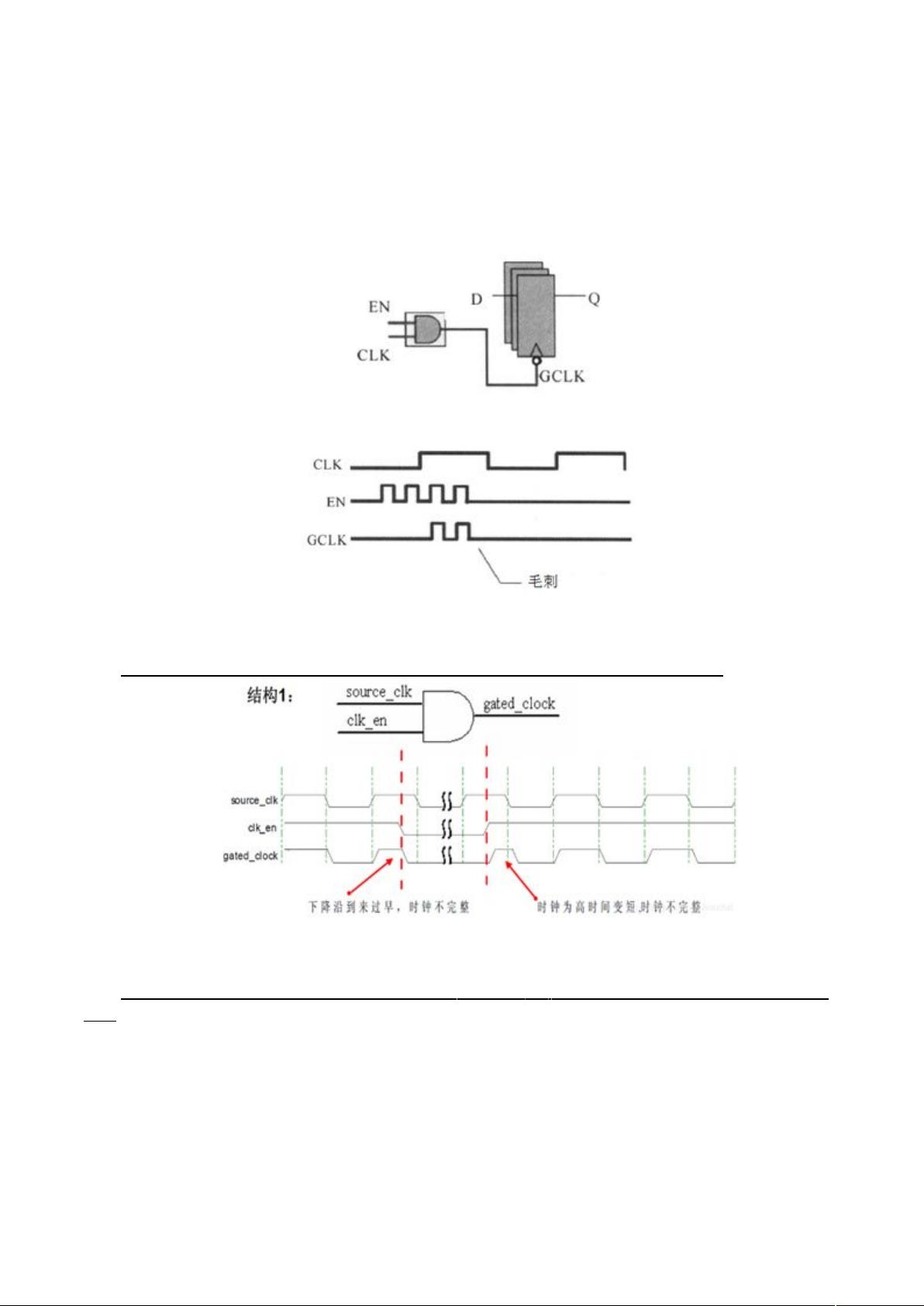

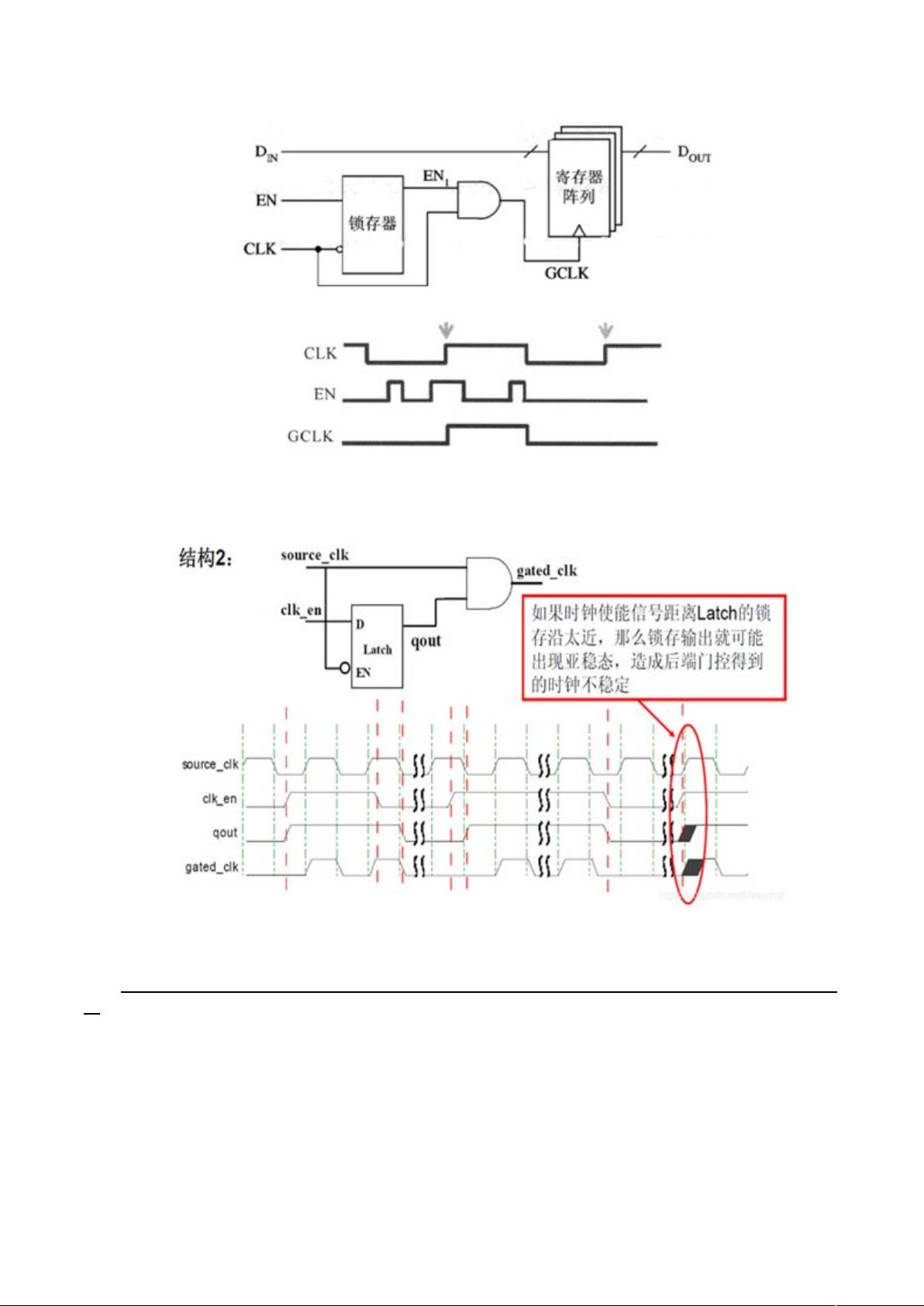

"低功耗之门控时钟设计" 本资源讨论了数字IC设计中低功耗设计的重要手段之一:门控时钟设计(clock gating)。 Clock gating 是一种降低芯片功耗的常用方法,相比 power gating 设计,clock gating 的设计和实现更为简单。 在数字IC设计中,时钟树的翻转行为是功耗的主要来源。门控时钟电路可以有效地降低动态功耗,通过减少时钟树的翻转行为、减少寄存器 clock pin 的翻转行为、减少大量MUX逻辑消耗的功耗,通常可以节省20%-60%的功耗,同时也节省了MUX面积。 门控时钟的用处分两种:一种直接针对寄存器的时钟进行门控,另一种对模块级别的时钟进行门控。其中,寄存器级的门控时钟更灵活,因为在很多时候,我们不能保证刚好将不需要门控的寄存器与需要门控的寄存器分配在不同的模块。 门控时钟单元分成两种:带锁存器(latch based)的门控时钟单元和不带有锁存器(latch free)的门控时钟单元。Latch based的门控时钟单元能避免毛刺,因此更推荐使用。 门控时钟又分为离散的和集成的(ICG)两种。离散的CG单元可以使用set_clock_gating_style命令来实现。ICG的基本结构包括使能信号、时钟信号和门控单元。 在设计门控时钟电路时,需要注意避免毛刺的出现。毛刺是指时钟信号上出现的不稳定的信号跳变,可能会导致系统的不稳定。解决思路是通过一个寄存器或触发器来同步使能信号,并且在时钟clk为高电平时,使能信号不变化。 本资源还讨论了两种常见的门控时钟结构:结构1和结构2。结构1是最简单的门控时钟电路,使用一个使能信号和一个与门来控制时钟的开关。但是,这种方法容易产生毛刺。结构2引入了基于锁存器同步使能信号的门控时钟方案,可以避免毛刺的出现。 本资源提供了详细的门控时钟设计知识,包括门控时钟的原理、类型、结构和实现方法,为数字IC设计师提供了有价值的参考。

剩余17页未读,继续阅读

- 粉丝: 2

- 资源: 1

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 兆瓦充电系统市场分析:2023年全球市场规模大约为19.6百万美元.docx

- 折叠自行车行业深度分析:2023年全球市场规模大约为151820百万美元.docx

- 脂肪酸行业深度分析:2023年全球市场规模大约为12540百万美元.docx

- 正己烷市场分析:2023年全球市场规模大约为900百万美元.docx

- 研学报告.pptx - 大数据技术研究与应用案例深度剖析

- 脂质体维生素补充剂行业分析:2023年全球市场规模大约为169百万美元.docx

- 植物糖原粉市场分析:2023年全球市场规模大约为231百万美元.docx

- 重型编码器行业分析:2023年全球市场规模大约为312百万美元.docx

- 中空纤维透析器行业分析:2023年全球市场规模大约为5992百万美元.docx

- 质子交换膜(PEM)行业分析:2023年全球市场规模大约为1294百万美元.docx

- 自动血红蛋白仪行业深度分析:2023年全球市场规模大约为1131百万美元.docx

- 自动生化仪行业分析:2023年全球市场规模大约为3289百万美元.docx

- 自覆膜标签市场分析:2023年全球市场规模大约为450百万美元.docx

- 工业级水滑石行业分析:亚太是全球最大的市场.docx

- 工业用压缩机市场分析:2023年全球市场规模大约为31360百万美元.docx

- 固态硬盘(SSD)行业市场:2023年全球市场规模大约为29410百万美元.docx

信息提交成功

信息提交成功

评论0