没有合适的资源?快使用搜索试试~ 我知道了~

cmos图像传感器一些应用参考.doc

需积分: 13 4 下载量 91 浏览量

2021-04-20

16:00:32

上传

评论

收藏 1.04MB DOC 举报

温馨提示

cmos图像传感器一些应用参考,适合初学者

资源推荐

资源详情

资源评论

什么是 CMOS 图像传感器?

CMOS:互补性氧化金属半导体 CMOS(Complementary Metal-Oxide

Semiconductor)和 CCD 一样同为在数码相机中可记录光线变化的半导体。CMOS 的

制造技术和一般计算机芯片没什么差别,主要是利用硅和锗这两种元素所做成的半导

体,使其在 CMOS 上共存着带 N(带-电) 和 P(带+电)级的半导体,这两个互补效

应所产生的电流即可被处理芯片纪录和解读成影像。然而,CMOS 的缺点就是太容易

出现杂点, 这主要是因为早期的设计使 CMOS 在处理快速变化的影像时,由于电流变

化过于频繁而会产生过热的现象。

CMOS 图像传感器 IBIS5-B-1300 的驱动时序设计

1.2 工作原理

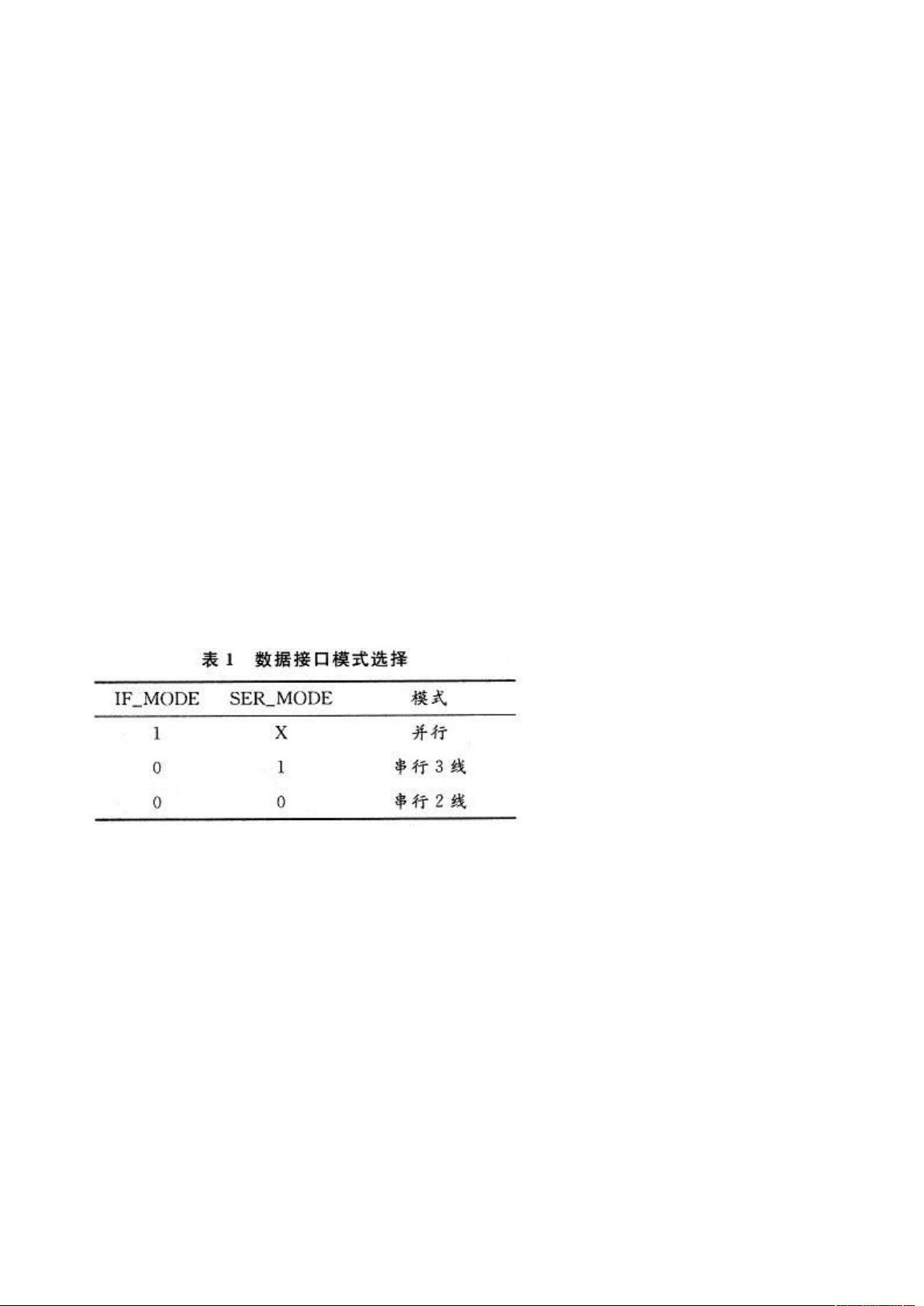

IBIS5-B-1300 内部有 12 个寄存器,提供传感器工作所需的参数及工作方式。对寄存

器写入的数据决定了传感器的工作状态。寄存器的数据写入接口有 3 种:并行接口、

串行三线接口、串行两线接口。可通过芯片的 IF_MODE 和 SER_MODE 管脚接不同

的值来选择不同的数据接口模式(如表 1 所示)。

并行接口使用 16 b 并行输入来载入新的寄存器值。串行 3 线接口(或串转并接口)使用

串行接口将数据移入寄存器缓冲器,当完整的数据字移入寄存器缓冲器时,数据字才

被载入当前正在编码的寄存器。串行 2 线是一个单向的接口,本文暂不做分析。

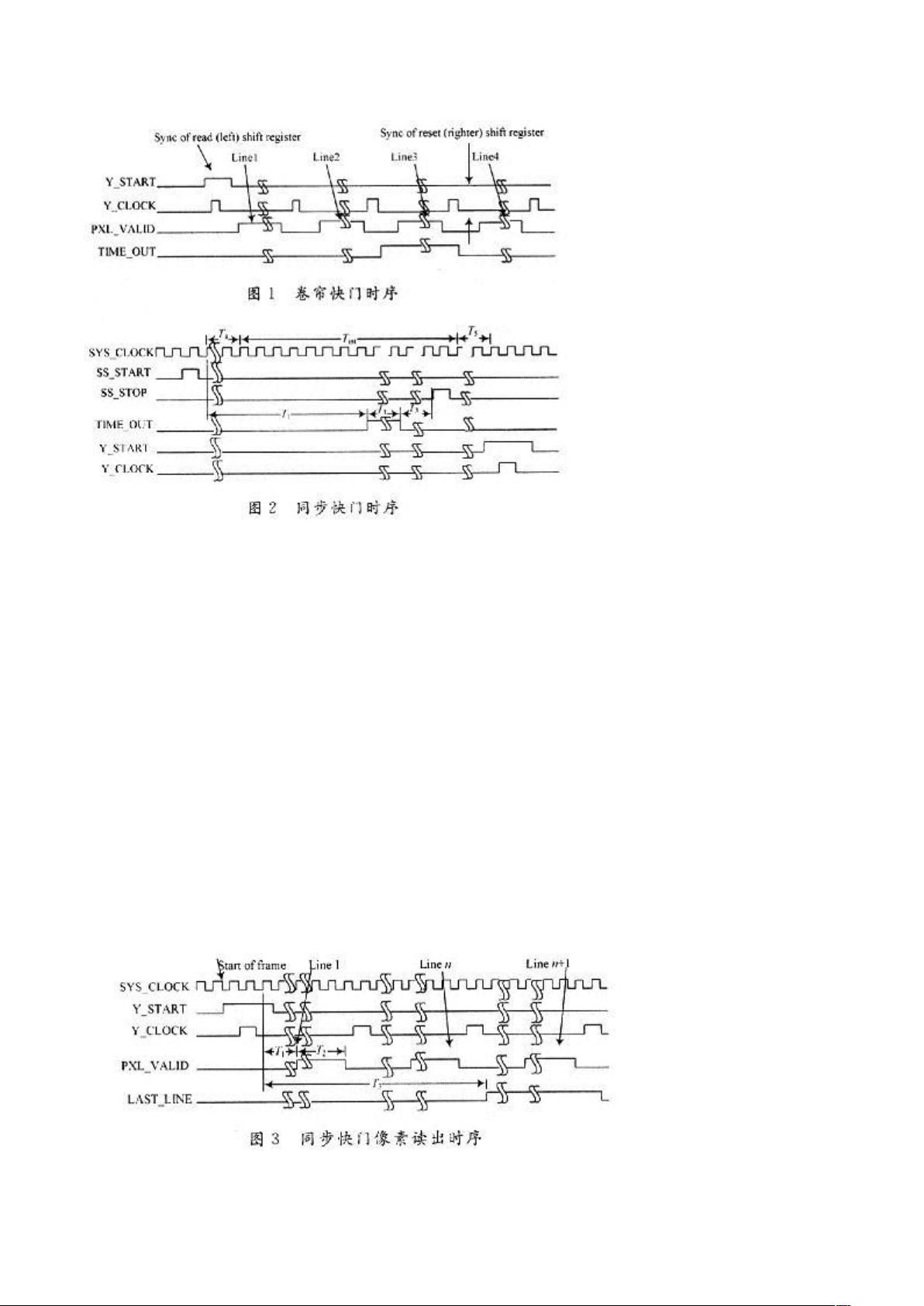

IBIS5-B-1300 具有两种快门方式:卷帘快门和同步快门,用寄存器(0000)的 bitO 进

行设定,“1”为卷帘快门,“0”为同步快门。时序如图 1,图 2 所示。

在卷帘快门模式下,帧频 Frame period=(Nr.Lines×(RBT+Pixel

Period*Nr.Pixels))。

在同步快门模式下,帧频 Frame period=”Tint”+Tread out=”Tint”+

(Nr.Lines×(RBT+Pixel Period*Nr.Pixels))。其中,Tint 为积分(曝光)时间;

Nr.Lines 为每帧读出的行数;Nr.Pixels 为每行读出的像素数;TBT 为行空白时间

(典型值为 3.5ms);Pixel Period 为 1/40MHZ=“25”。

卷帘快门中有两个 y 方向的移位寄存器,一个指向正在被读出的行,另一个指向

正在被复位的行,两个指针由同一时钟 y_clock(行时钟)驱动,它们之间的差值代表了

光积分时间。在卷帘快门模式下,像素的读出和复位同时进行,每行像素的复位和读

出是顺序进行的(见图 3)。像素的积分时间可以通过寄存器 INT_TIME 来修改。在这种

模式下,像素在不同的时刻感光,因而在采集动态图像时会产生模糊。

在同步快门模式下,所有像素的光积分在同一时刻进行的。所有像素同时被复位,

在经过光积分后,像素的值被存储在每个像素的存储节点上,然后逐行依次读出。像

素的光积分和读出是串行的,在像素读出时,积分被禁止,因而可以避免卷帘快门所

产生的动态图像模糊的问题。此外,同步快门支持多斜率积分,可获得比卷帘快门更

高的动态范围。

综上分析,在使用这款成像器芯片时,对快门方式要根据应用的场合进行选择,

在对快速运动的物体进行捕获或要求有高的动态范围时应选择同步快门;而在对图像

的帧速率要求较高或要对图像进行连续采集时应选择卷帘快门。

2 基于 FPGA 的 CMOS 控制时序的设计

2.1 现场可编程门阵列 FPGA

随着集成电路的发展,大规模可编程逻辑器件广泛用于电路设计领域,它具有功

耗低,可靠性高的特点,同时大大减小了电路板的尺寸。FPGA 的内部结构决定了

FPGA 在时序设计方面的优越性。该设计选用 Xilinx 公司的 Spartan3 系列 FPGA 芯

片 XC3$50 作为硬件设计平台。Spar-tan3 基于 VirtexⅡFPGA 架构,采用 90 nm 技

术,8 层金属工艺,内嵌硬核乘法器和数字时钟管理模块。从结构上看,它将逻辑、

存储器、数字运算、数字处理器、I/O 以及系统管理资源完美地结合在一起,使之具

有更高层次、更广泛的应用。

2.2 控制时序的设计

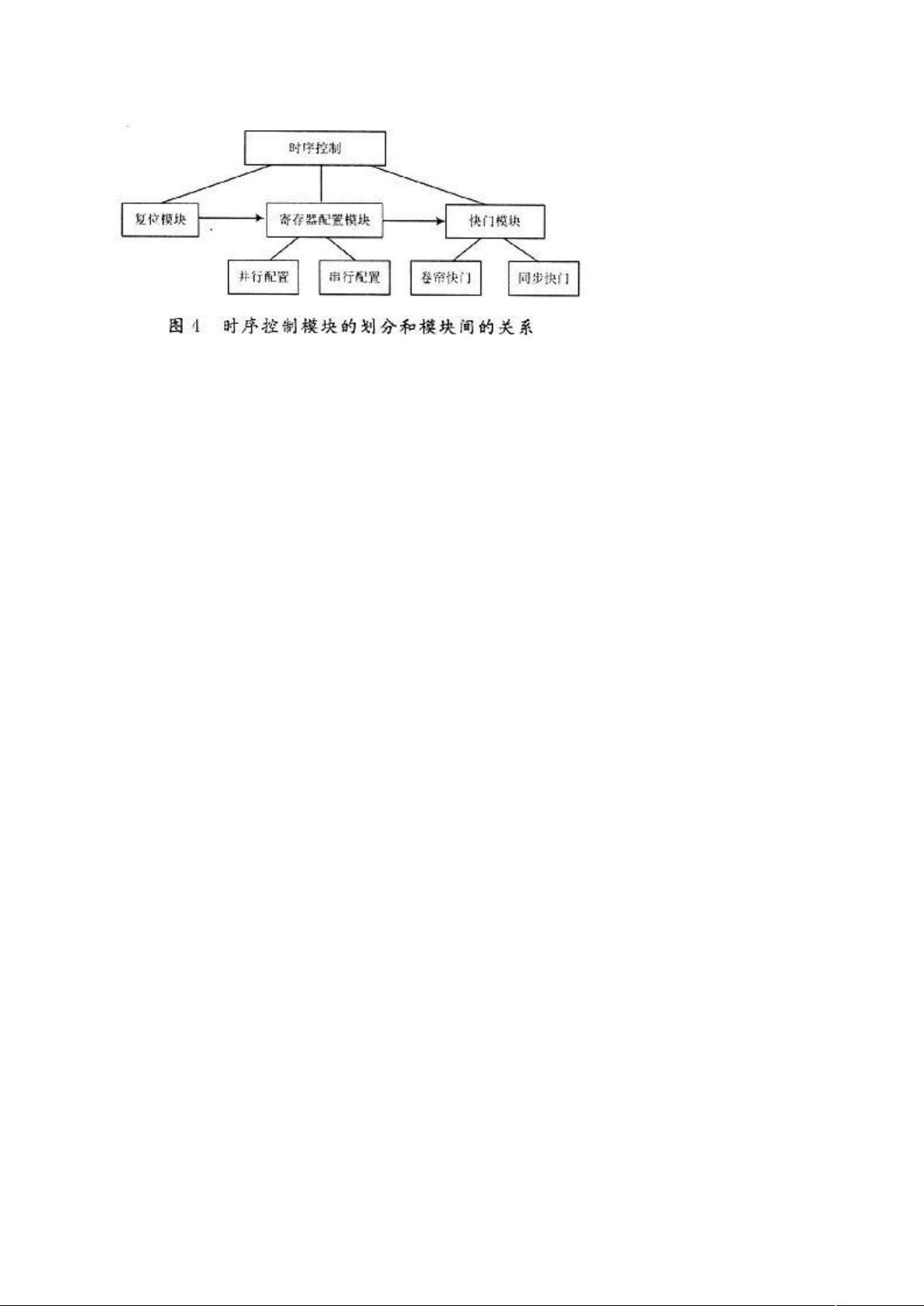

该设计采用 VHDL 硬件描述语言,根据自顶向下的设计方法,将时序控制部分分

为三个模块:复位模块、寄存器配置模块和快门模块。由于寄存器有两种配置方式,

快门模式也有两种,因而后两部分都可以再细分为两个小模块。三个大的模块有严格

的先后关系,必须在前一模块已完成后,才可开始后一模块。

图 4 显示模块的划分及其关系。

复位模块是用来产生图像传感器所需的 SYS_RE_SET 信号,使传感器正常复位,

内部寄存器清零,为寄存器的配置做好准备。

寄存器配置模块是用来配置图像传感器内部的 12 个寄存器,提供传感器工作所需

的参数和方式。其中,参数有积分时间、积分方式(单斜率或多斜率)、X 序列发生器

的时钟间隔、SS 序列发生器的时钟间隔、亚采样方式、开窗位置及大小等。

快门模块用于产生传感器工作所需的一些控制信号,针对快门方式的不同给出所

需的时序控制信号。在同步快门的设计中,该设计采用单斜率积分,在此设计基础上

多斜率积分容易实现。

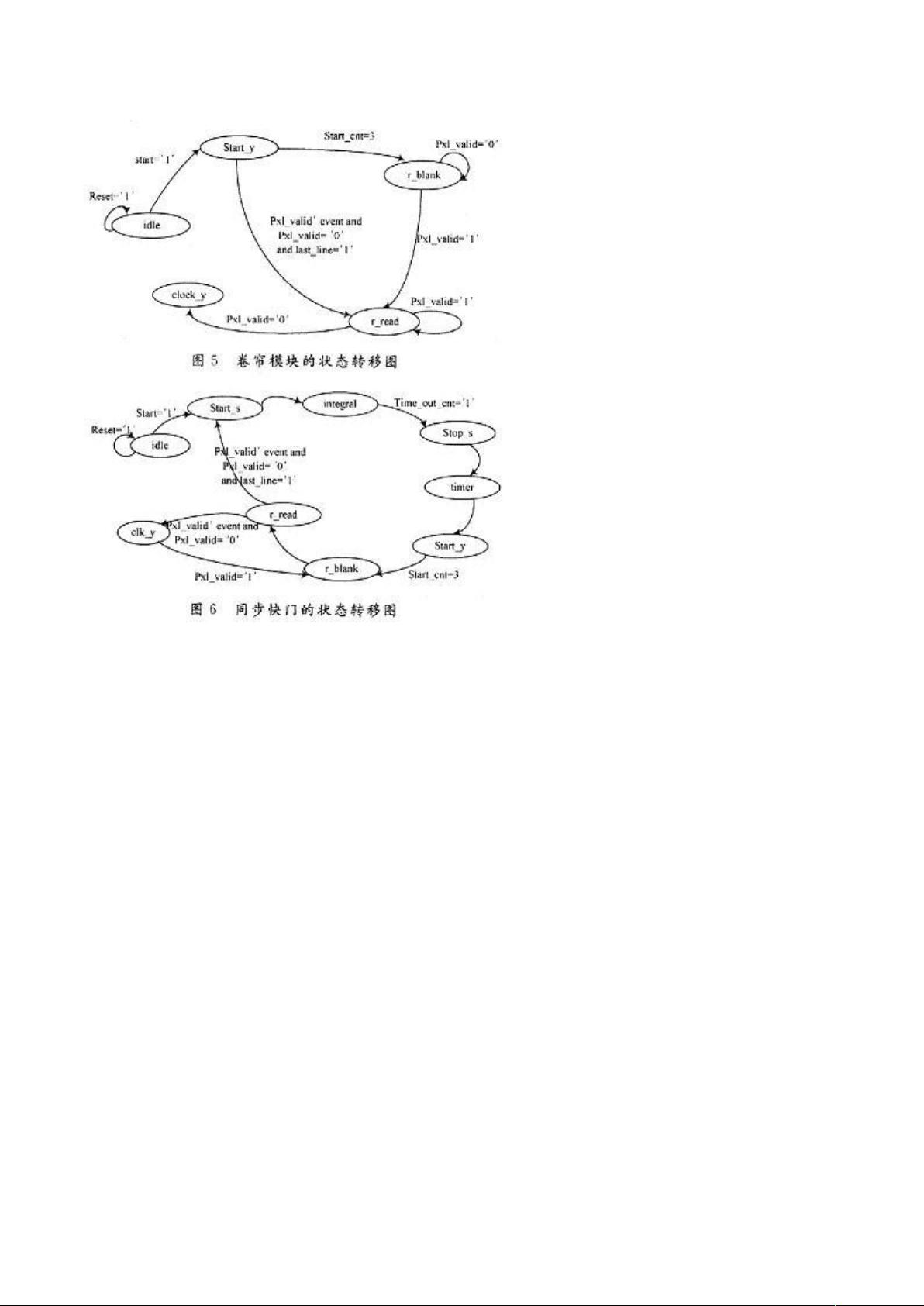

该设计采用 VHDL 对各模块时序进行编程。其中,快门模块使用状态机来实现各

状态之间的转换(图 5 显示了卷帘模块的状态转移图,图 6 显示了同步快门的状态转移

图)。全局时钟和 ADC 时钟采用 DCM 即数字时钟管理单元来实现。

3 实验结果

3.1 仿真结果

时序控制电路设计完毕后,需要对各部分进行功能仿真、逻辑综合以及综合后仿真,

最后对整个系统进行综合、布局布线,完成时序仿真。对各模块编程并仿真通过后,

将各模块加载到主函数 top 中,采用并行的寄存器配置方式,对卷帘和同步两种快门

方式进行仿真,在 Modelsim 中的仿真结果如图 7,图 8 所示。

剩余40页未读,继续阅读

资源评论

qq_24196051

- 粉丝: 0

- 资源: 11

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功