没有合适的资源?快使用搜索试试~ 我知道了~

tps40345-mos管-电感-电容-数值计算

需积分: 5 0 下载量 176 浏览量

2022-05-23

17:43:27

上传

评论

收藏 2.43MB PDF 举报

温馨提示

试读

29页

tps40345-mos管-电感-电容-数值计算

资源详情

资源评论

资源推荐

5

4

3

2

6

7

8

9

BOOT

HDRV

SW

LDRV/OC

FB

COMP

PGOOD

EN/SS

TPS40345

1 10BPVDD

PAD

V

IN

SD

V

OUT

V

IN

Copyright © 2017, Texas Instruments Incorporated

V

OUT

GND

Product

Folder

Order

Now

Technical

Documents

Tools &

Software

Support &

Community

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications,

intellectual property matters and other important disclaimers. PRODUCTION DATA.

English Data Sheet: SLUSD62

TPS40345

ZHCSH69 –DECEMBER 2017

TPS40345 3V 至至 20V 输输入入同同步步降降压压控控制制器器

1

1 特特性性

1

• 输入电压范围:3V 至 20V

• 600kHz 开关频率

• 高侧和低侧 FET R

DS(on)

电流检测

• 可编程热补偿 OCP 电平

• 可编程软启动

• 600mV、1.3% 基准电压

• 电压前馈补偿

• 支持预偏置输出

• 扩频频谱

• 145°C 的热关断保护限制

• 10 引脚 3mm × 3mm VSON 封装,散热垫具有接

地连接

2 应应用用

• 负载点 (POL) 模块

• 打印机

• 数字电视

• 电信

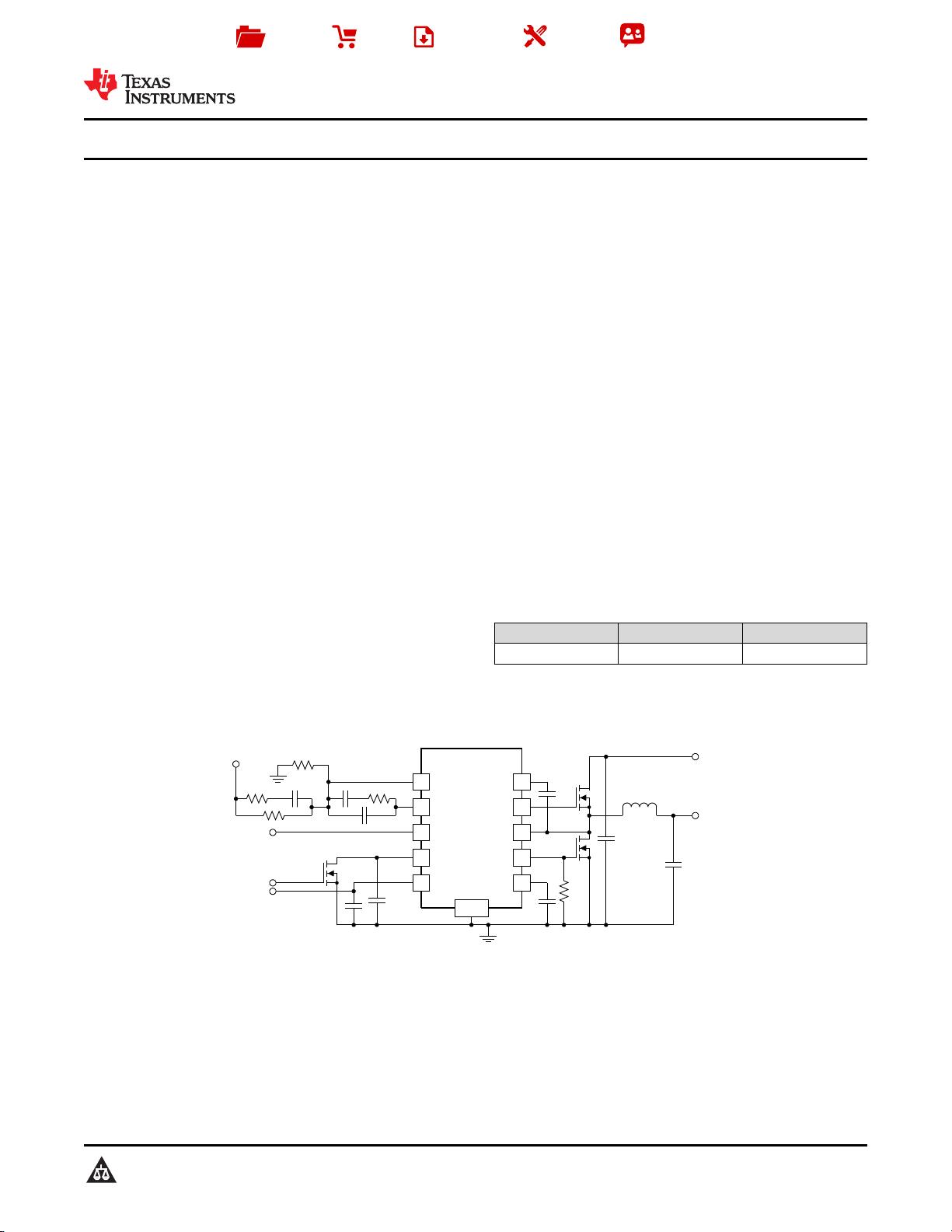

3 说说明明

TPS40345 是一款同步降压控制器,可在 3V 到 20V

的输入电压下工作,可用于成本优化型 应用。此控制

器实现了一种电压模式控制架构,具有输入电压前馈补

偿功能,可对输入电压变化做出即时响应。开关频率设

置为 600kHz。

开关频率中添加了扩频频谱 (FSS) 功能,显著降低了

峰值 EMI 噪声,使其更容易符合 EMI 标准。

TPS40345 可提供各种用户可编程功能,其中包括软

启动、过流保护 (OCP) 电平以及环路补偿。

OCP 电平可以通过从 LDRV 引脚连接到电路接地的单

个外部电阻器进行编程。在初始上电过程

中,TPS40345 可进入校准环节,测量 LDRV 引脚电

压,并设置内部 OCP 电压级。在工作期间,器件可在

通电时通过将已编程 OCP 电压电平与低侧 FET 上的

压降进行比较来确定是否发生过流情况。之

后,TPS40345 会进入关断和重启周期,直到故障消

除为止。

器器件件信信息息

(1)

器器件件型型号号 封封装装 封封装装尺尺寸寸((标标称称值值))

TPS40345 VSON (10) 3.00mm × 3.00mm

(1) 如需了解所有可用封装,请参阅数据表末尾的可订购产品附

录。

简简化化应应用用示示意意图图

2

TPS40345

ZHCSH69 –DECEMBER 2017

www.ti.com.cn

Copyright © 2017, Texas Instruments Incorporated

目目录录

1 特特性性.......................................................................... 1

2 应应用用.......................................................................... 1

3 说说明明.......................................................................... 1

4 修修订订历历史史记记录录 ........................................................... 2

5 Pin Configuration and Functions......................... 3

6 Specifications......................................................... 4

6.1 Absolute Maximum Ratings ...................................... 4

6.2 ESD Ratings.............................................................. 4

6.3 Recommended Operating Conditions....................... 4

6.4 Thermal Information.................................................. 4

6.5 Electrical Characteristics........................................... 5

6.6 Typical Characteristics.............................................. 7

7 Detailed Description.............................................. 9

7.1 Overview ................................................................... 9

7.2 Functional Block Diagram ......................................... 9

7.3 Feature Description................................................... 9

7.4 Device Functional Modes........................................ 12

8 Application and Implementation ........................ 13

8.1 Application Information............................................ 13

8.2 Typical Applications ................................................ 13

9 Power Supply Recommendations...................... 17

10 Layout................................................................... 18

10.1 Layout Guidelines ................................................. 18

10.2 Layout Example .................................................... 19

11 器器件件和和文文档档支支持持 ..................................................... 20

11.1 器件支持................................................................ 20

11.2 文档支持................................................................ 20

11.3 接收文档更新通知 ................................................. 20

11.4 社区资源................................................................ 20

11.5 商标 ....................................................................... 20

11.6 静电放电警告......................................................... 20

11.7 Glossary................................................................ 20

12 机机械械、、封封装装和和可可订订购购信信息息....................................... 20

4 修修订订历历史史记记录录

注:之前版本的页码可能与当前版本有所不同。

日日期期 修修订订版版本本 说说明明

2017 年 12 月 * 初始发行版

5 4 3 2 1

6 7 8 9 10

FB COMP PGOOD EN/SS VDD

BOOT HDRV SW

LDRV/

OC

BP

Thermal Pad

3

TPS40345

www.ti.com.cn

ZHCSH69 –DECEMBER 2017

Copyright © 2017, Texas Instruments Incorporated

5 Pin Configuration and Functions

DRC Package

10-Pin VSON

Top View

Pin Functions

PIN

I/O DESCRIPTION

NAME NO.

BOOT 6 I

Gate drive voltage for the high-side N-channel MOSFET. A 0.1-µF capacitor (typical) must be connected

between this pin and SW. For low input voltage operation, an external Schottky diode from BP to BOOT is

recommended to maximize the gate drive voltage for the high-side.

BP 10 O

Output bypass for the internal regulator. Connect a low ESR bypass ceramic capacitor of 1 µF or greater from

this pin to GND.

COMP 4 O Output of the error amplifier and connection node for loop feedback components.

EN/SS 2 I

Logic level input which starts or stops the controller via an external user command. Letting this pin float turns

the controller on. Pulling this pin low disables the controller. This is also the soft-start programming pin. A

capacitor connected from this pin to GND programs the soft-start time. The capacitor is charged with an

internal current source of 10 µA. The resulting voltage ramp of this pin is also used as a second non-inverting

input to the error amplifier after a 0.8 V (typical) level shift downwards. Output regulation is controlled by the

internal level shifted voltage ramp until that voltage reaches the internal reference voltage of 600 mV – the

voltage ramp of this pin reaches 1.4 V (typical). Optionally, a 267-kΩ resistor from this pin to BP enables the

FSS feature.

FB 5 I

Inverting input to the error amplifier. In normal operation, the voltage on this pin is equal to the internal

reference voltage.

PGOOD 3 O Open-drain power good output.

HDRV 7 O Bootstrapped gate drive output for the high-side N-channel MOSFET.

LDRV/OC 9 O

Gate drive output for the low-side synchronous rectifier N-channel MOSFET. A resistor from this pin to GND

is also used to determine the voltage level for OCP. An internal current source of 10 µA flows through the

resistor during initial calibration and that sets up the voltage trip point used for OCP.

VDD 1 I

Power input to the controller. Bypass VDD to GND with a low ESR ceramic capacitor of at least 1 µF close to

the device.

SW 8 O

Sense line for the adaptive anti-cross conduction circuitry. Serves as common connection for the flying high-

side FET driver.

GND

Thermal

Pad

—

Ground connection to the controller. This is also the thermal pad used to conduct heat from the device. This

connection serves a twofold purpose. The first is to provide an electrical ground connection for the device.

The second is to provide a low thermal impedance path from the device die to the PCB. This pad should be

tied externally to a ground plane.

4

TPS40345

ZHCSH69 –DECEMBER 2017

www.ti.com.cn

Copyright © 2017, Texas Instruments Incorporated

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings

only and functional operation of the device at these or any other condition beyond those included under Recommended Operating

Conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods of time may affect device reliability.

6 Specifications

6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)

(1)

MIN MAX UNIT

VDD –0.3 22 V

SW –3 27 V

SW (< 100 ns pulse width, 10 µJ) –5 V

BOOT –0.3 30 V

HDRV –5 30 V

BOOT-SW, HDRV-SW (differential from BOOT or HDRV to SW) –0.3 7 V

COMP, PGOOD, FB, BP, LDRV, EN/SS –0.3 7 V

Operating junction temperature, T

J

–40 145 °C

Storage temperature, T

stg

–55 150 °C

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

6.2 ESD Ratings

VALUE UNIT

V

(ESD)

Electrostatic discharge

Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001

(1)

±2000

V

Charged-device model (CDM), per JEDEC specification JESD22-C101

(2)

±1500

6.3 Recommended Operating Conditions

MIN NOM MAX UNIT

Input voltage, VDD 3 20 V

Operating junction temperature, T

J

–20 125 °C

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application

report.

6.4 Thermal Information

THERMAL METRIC

(1)

TPS40345

UNITDRC (VSON)

10 PINS

R

θJA

Junction-to-ambient thermal resistance 44.3 °C/W

R

θJC(top)

Junction-to-case (top) thermal resistance 56.1 °C/W

R

θJB

Junction-to-board thermal resistance 19.2 °C/W

ψ

JT

Junction-to-top characterization parameter 0.7 °C/W

ψ

JB

Junction-to-board characterization parameter 19.4 °C/W

R

θJC(bot)

Junction-to-case (bottom) thermal resistance 5.5 °C/W

5

TPS40345

www.ti.com.cn

ZHCSH69 –DECEMBER 2017

Copyright © 2017, Texas Instruments Incorporated

(1) Ensured by design. Not production tested.

6.5 Electrical Characteristics

T

J

= –20°C to 125° C, V

VDD

= 12 V, all parameters at zero power dissipation (unless otherwise noted)

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

VOLTAGE REFERENCE

V

FB

FB input voltage

T

J

= 25°C, 3 V < V

VDD

< 20 V 597 600 603

mV

–20°C < T

J

< 125°C, 3 V < V

VDD

< 20 V 592 600 608

INPUT SUPPLY

V

VDD

Input supply voltage range 3 20 V

IDD

SD

Shutdown supply current V

EN/SS

< 0.2 V 70 100 µA

IDD

Q

Quiescent, nonswitching Let EN/SS float, V

FB

= 1 V 2.5 3.5 mA

ENABLE/SOFT-START

V

IH

High-level input voltage,

EN/SS

0.55 0.7 1 V

V

IL

Low-level input voltage,

EN/SS

0.27 0.3 0.33 V

I

SS

Soft-start source current 8 10 12 µA

V

SS

Soft-start voltage level 0.4 0.8 1.3 V

BP REGULATOR

V

BP

Output voltage I

BP

= 10 mA 6.2 6.5 6.8 V

V

DO

Regulator dropout voltage,

V

VDD

– V

BP

I

BP

= 25 mA, V

VDD

= 3 V 70 110 mV

OSCILLATOR

f

SW

PWM frequency 540 600 660 kHz

V

RAMP

(1)

Ramp amplitude V

VDD

/6.6 V

VDD

/6 V

VDD

/5.4 V

f

SWFSS

Frequency spread-spectrum

frequency deviation

12% f

SW

f

MOD

Modulation frequency 25 kHz

PWM

D

MAX

(1)

Maximum duty cycle V

FB

= 0 V, 3 V < V

VDD

< 20 V 90%

t

ON(min)

(1)

Minimum controllable pulse

width

70 ns

t

DEAD

Output driver dead time

HDRV off to LDRV on 5 25 35

ns

LDRV off to HDRV on 5 25 30

ERROR AMPLIFIER

G

BWP

(1)

Gain bandwidth product 10 24 MHz

A

OL

(1)

Open loop gain 60 dB

I

IB

Input bias current (current

out of FB pin)

V

FB

= 0.6 V 75 nA

I

EAOP

Output source current V

FB

= 0 V 2

mA

I

EAOM

Output sink current V

FB

= 1 V 2

PGOOD

V

OV

Feedback upper voltage limit

for PGOOD

655 675 700

mVV

UV

Feedback lower voltage limit

for PGOOD

500 525 550

V

PGD-HYST

PGOOD hysteresis voltage

at FB

25 40

R

PGD

PGOOD pulldown resistance V

FB

= 0 V, I

FB

= 5 mA 30 70 Ω

I

PGDLK

PGOOD leakage current

550 mV < V

FB

< 655 mV,

V

PGOOD

= 5 V

10 20 µA

剩余28页未读,继续阅读

ltqshs

- 粉丝: 6w+

- 资源: 219

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论0