5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

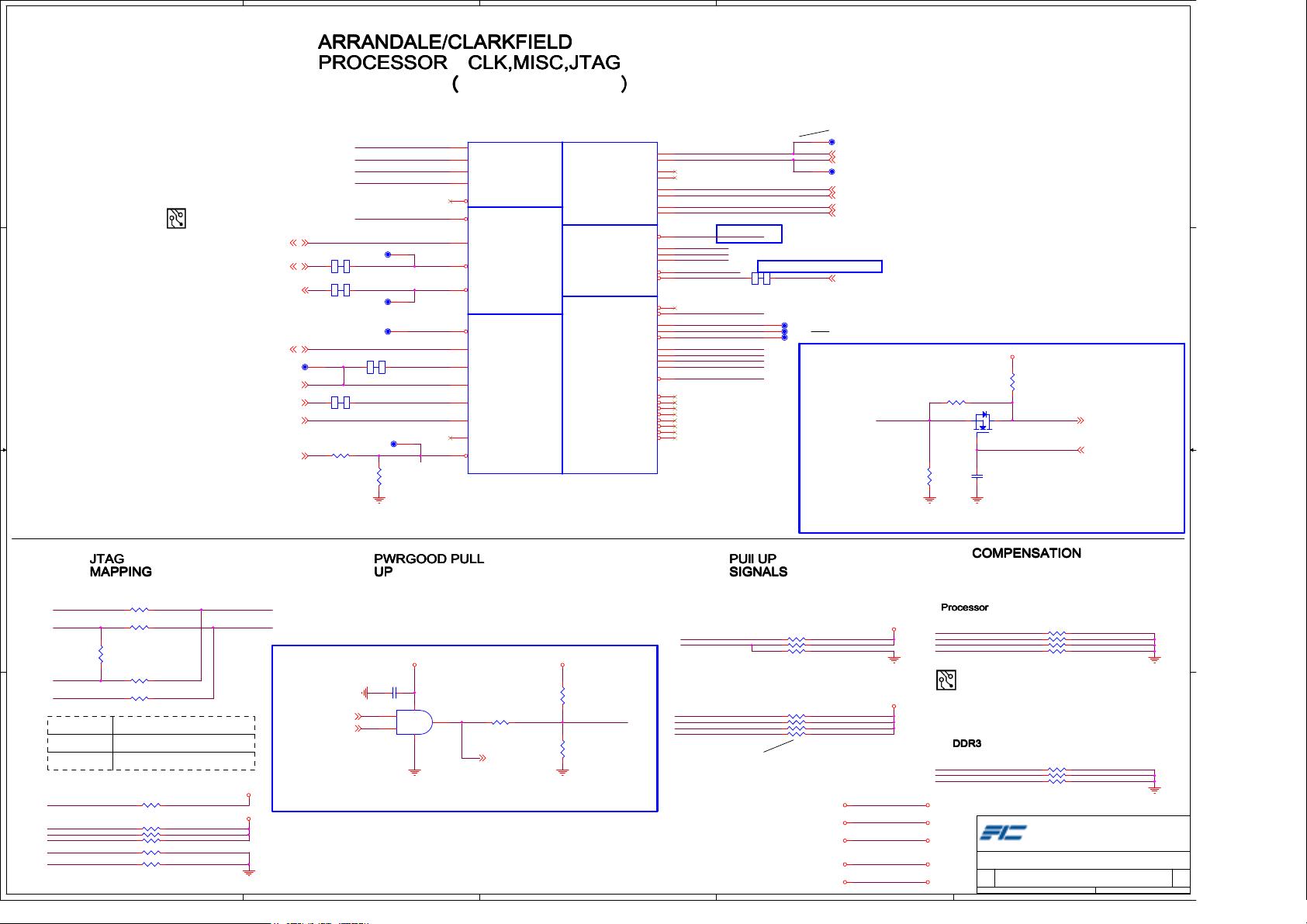

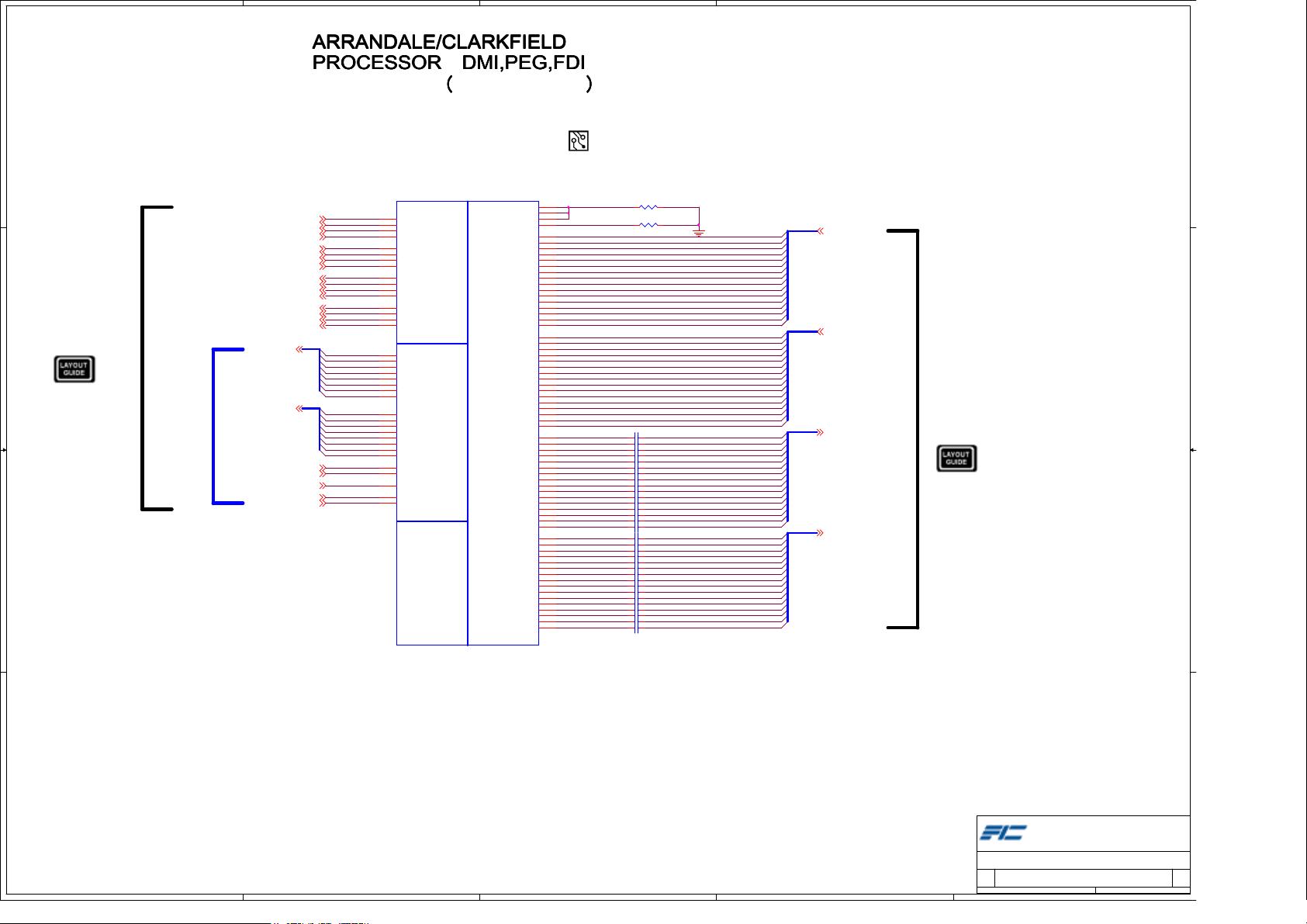

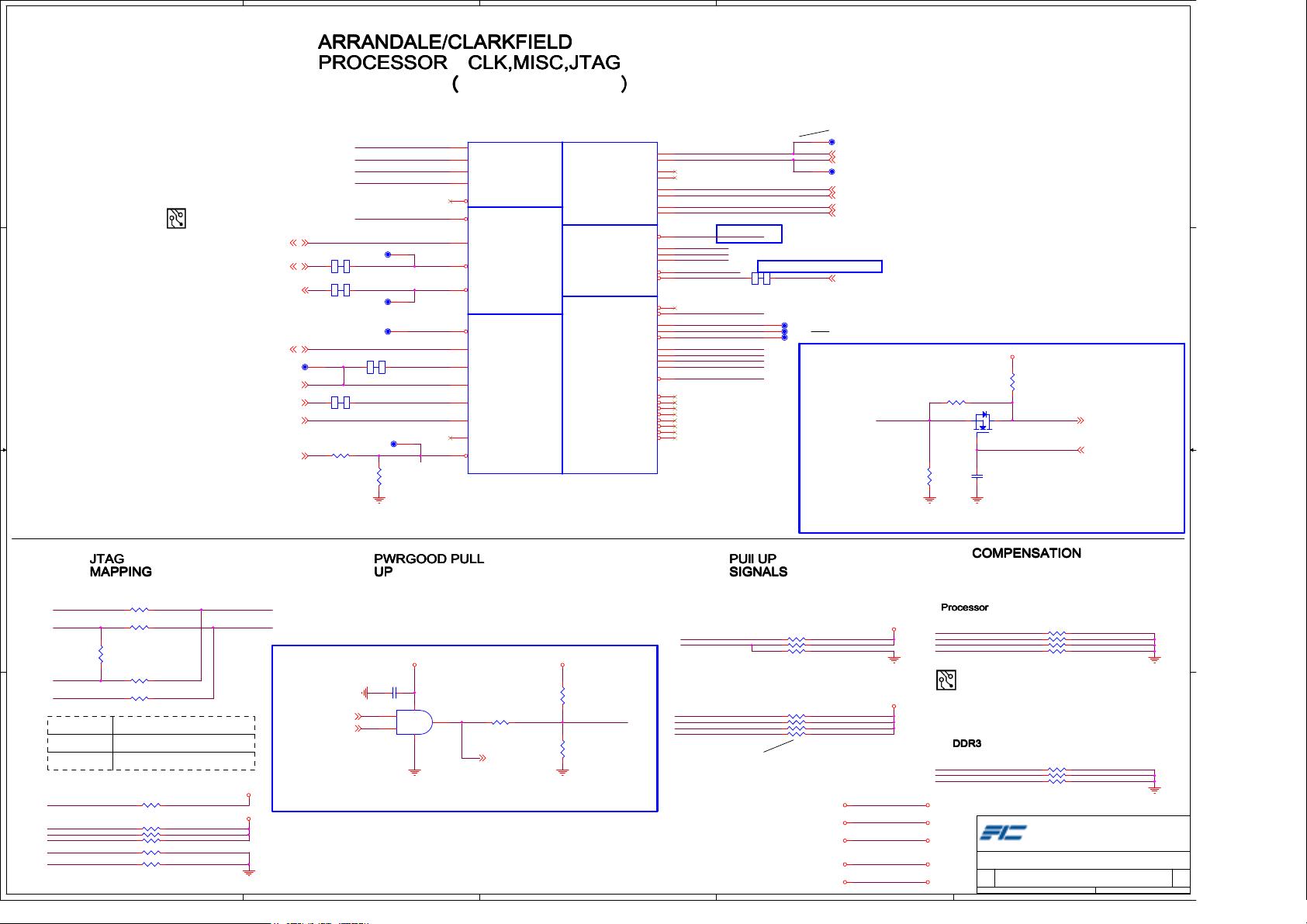

A R R A N D A L E / C L A R K F I E L D

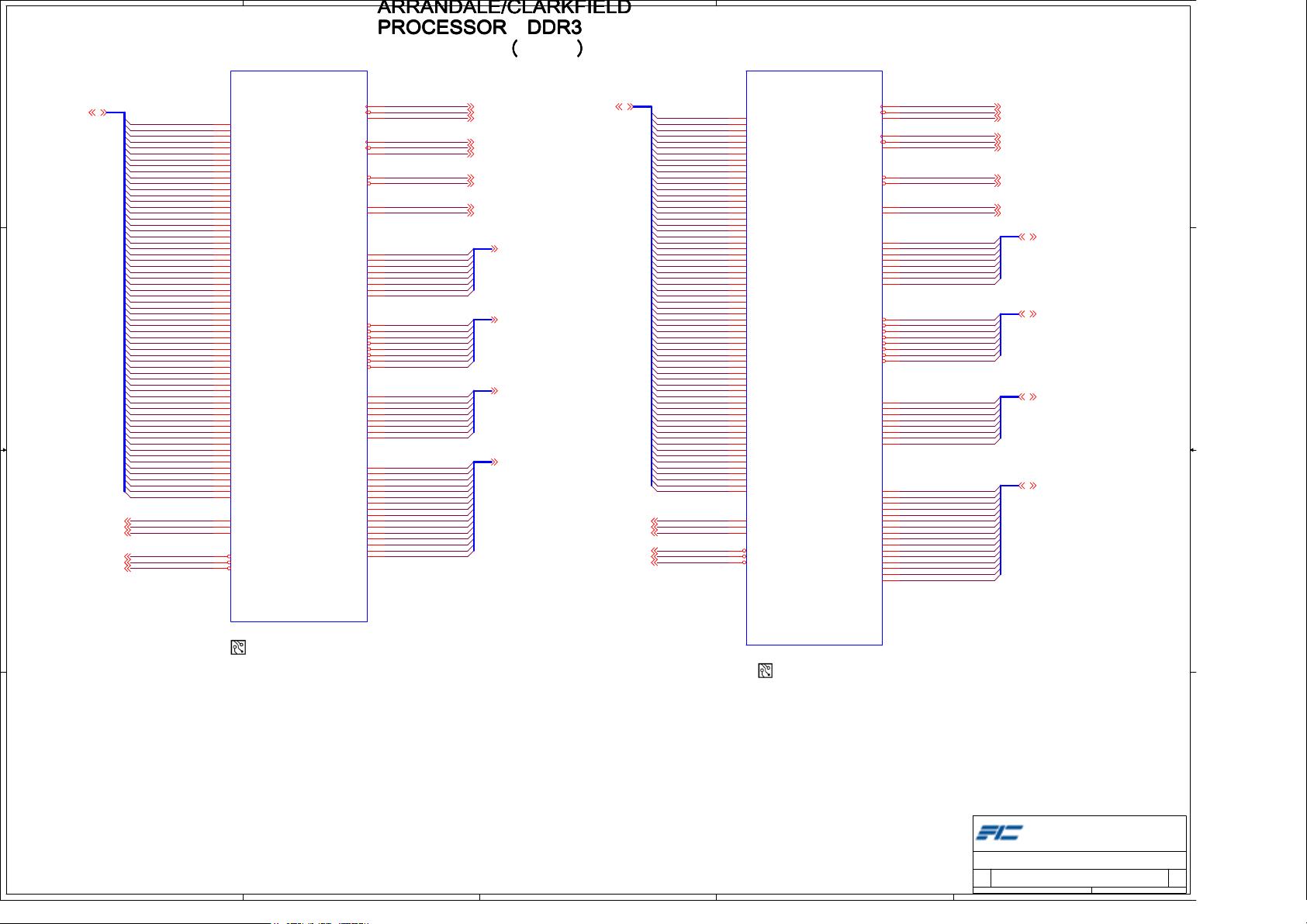

A R R A N D A L E / C L A R K F I E L DA R R A N D A L E / C L A R K F I E L D

A R R A N D A L E / C L A R K F I E L D

P R O C E S S O R

(

C L K , M I S C , J T A G

)

P R O C E S S O R

(

C L K , M I S C , J T A G

)

P R O C E S S O R

(

C L K , M I S C , J T A G

)

P R O C E S S O R

(

C L K , M I S C , J T A G

)

P r o c e s s o r

P r o c e s s o rP r o c e s s o r

P r o c e s s o r

D D R 3

D D R 3D D R 3

D D R 3

J T A G

J T A GJ T A G

J T A G

M A P P I N G

M A P P I N GM A P P I N G

M A P P I N G

Scan Chain

(Default)

CPU Only

GMCH Only

STUFF -> R193, R194, R217

NO STUFF -> R195, R216

STUFF -> R193, R195

NO STUFF -> R194,R216,R217

STUFF -> R216, R217

NO STUFF -> R193,R194,R195

P U l l U P

P U l l U PP U l l U P

P U l l U P

S I G N A L S

S I G N A L SS I G N A L S

S I G N A L S

C O M P E N S A T I O N

C O M P E N S A T I O NC O M P E N S A T I O N

C O M P E N S A T I O N

All COMP use 10-mils trace width for routing less than 500 mils,

or 20-mils trace width for routing between 500 and 1000 mils;

Keep 20-mils spacing to other signals to minimize crosstalk

P W R G O O D P U L L

P W R G O O D P U L LP W R G O O D P U L L

P W R G O O D P U L L

U P

U PU P

U P

Layout note:Zo=50 ohm,

15'' max for PECI

0311

0312 add follow check list

MoW WW14 Update

Voltage Divider Ratio

0420 Add EC path

PDG V1.5 Update

Voltage Divider Ratio

PDG V1.5 Update

0311

PDG V1.5 Update

VTTPWRGOOD Comes from EC

should be level shift to 1.1VDDM_VTT

H_PROCHOT# Comes from EC

have to "OD" type

V0.2 0731 CHANGE NET

FOR S3 power reduce

V0.2 0801 Change to NU

V0.2 0801 Change to 750 ohm

3.3.4 SM_DRAMPWROK to Processor Should Be Held Low during S3

AND gate is used to provide DRAMPWRGD signal to CPU during S3 exit

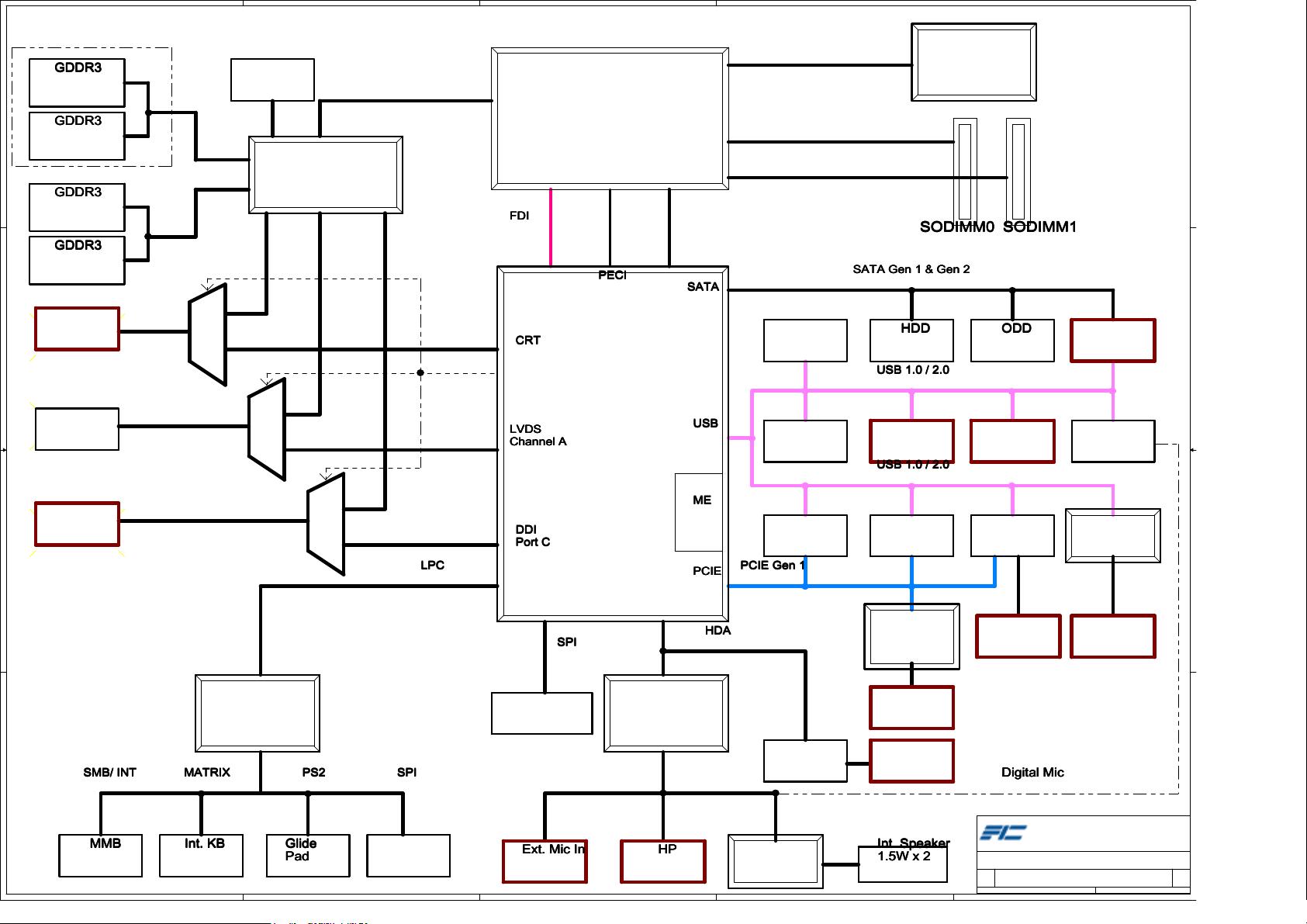

BLOCK 5

V0.2 0804

V0.2 0814 Change NET

V0.2 0812 DELETE NET

V0.2 0804 SM_DRAMRST# Should Be Held High during S3

VGS<1.5V

Use a 3.3V SUS well GPIO form PCH or 3.3V GPIO form embedded controller

fet is uded to isolate DDR RESET from CPU to memory during suspend

BLOCK 3 and BLOCK6

V0.2 change to 1.1S_PGD

PROCESSOR CLK/MISC/JTAG(P09110)

0.2

5FL.,NO.300,Yang Guang St.,NeiHu

114 TAIPEI, TAIWAN ,ROC

(886-2) 8751-8751

C

4 60Wednesday, August 19, 2009

PCA50D (Intel Calpella +AMD GPU M92-M)

Title

Size Document Number Rev

Date: Sheet of

First International Computer, Inc.

H_COMP3

H_COMP2

H_COMP1

H_COMP0

H_CATERR#

H_PROCHOT#_D

VDDPWRGOOD_R

SYS_AGENT_PWROK

PLT_RST#_R

CPUDRAM_RST

SM_RCOMP_0

SM_RCOMP_1

SM_RCOMP_2

PM_EXTTS#[1]

XDP_PREQ#

XDP_TCLK

XDP_TMS

XDP_TRST#

XDP_TDI_R

XDP_TDO_R

XDP_TDI_M

XDP_TDO_M

XDP_DBRESET#

H_CPURST#_R

1.1VDDM_VTT

H_CATERR#

H_PROCHOT#_D

H_CPURST#_R

H_COMP0

H_COMP1

H_COMP2

H_COMP3

SM_RCOMP_1

SM_RCOMP_0

SM_RCOMP_2

XDP_TMS

XDP_TDI_R

XDP_PREQ#

XDP_TCLK

XDP_TDO_M XDP_TDO

XDP_TDO_R

XDP_TDI_M

XDP_TDI_R XDP_TDI

XDP_DBRESET#

3VDDM

PM_EXTTS#[0]

PM_EXTTS#[0]

PM_EXTTS#[1]

H_THRMTRIP#_R

XDP_TRST#

XDP_TDO_R

VDDPWRGOOD_R

3VDDA

CPUDRAM_RST

1.5VDDS

DDR_1.5_VDDQ

H_PECI[19]

H_PROCHOT#[48,55]

H_THRMTRIP#[19]

H_PM_SYNC[16]

H_CPUPWRGD[19]

PM_DRAM_PWRGD[16]

H_VTTPWRGD[23]

PLTRST#[18,24,39,41,42,43,48]

PM_EXTTS#1_R [12,13]

BCLK_CPU_P [19]

BCLK_CPU_N [19]

CLK_EXP_P [15]

CLK_EXP_N [15]

1.1VDDM_VTT[6,7,19,20,21,54,55]

CLK_DP_P [15]

CLK_DP_N [15]

3VDDM[10,11,12,13,14,15,16,17,18,19,20,21,23,24,25,28,33,34,35,36,37,39,41,42,43,46,47,48,52,54,55,56,57]

1.1VDDM_PWRGD[23,48,54]

1.5VDDM_PWRGD[23]

1.5M_1.1M_PWRGD [53]

3VDDA[14,15,16,18,19,21,23,33,39,41,42,43,46,47,48,52,53]

DRAMRST_CNTRL_PCH [12,13,19]

DDR3_DRAMRST# [12,13]

1.5VDDS[7,12,13,53]

DDR_1.5_VDDQ[7,23]

1.1VDDM_VTT

1.1VDDM_VTT

DDR_1.5_VDDQ

3VDDM

3VDDM

1.1VDDM_VTT

1.1VDDM_VTT

3VDDA

3VDDA

1.5VDDS

1.5VDDS

DDR_1.5_VDDQ

U70

DL-IC NC7S08P5X_NL SC70 5PIN FAIRCHILD LR

1

2

53

4

TP5

1

R219

SHW 0 5% 1/16W 0402

R186

SHW 0 5% 1/16W 0402

TP8

1

R217 0Ω 5% 1/16W SMT0402 LR

TP11

1

TP9

1

C1137 0.1uF 10V 10% SMT0402 X5R LR

TP7

1

R191 49.9Ω 1% 1/16W SMT0402 LR

R187

10KΩ 5% 1/16W SMT0402 LR

R1076

1KΩ 5% 1/16W SMT0402 LR

R190 20Ω 1% 1/16W SMT0402 LRR189 12.4KΩ 1% 1/16W SMT0402 LR(NU)

R1075

1.5KΩ 1% 1/16W SMT0402 LR

R210

SHW 0 5% 1/16W 0402

R194

0Ω 5% 1/16W SMT0402 LR

R223 68Ω 5% 1/16W SMT0402 LR(NU)

R123 49.9Ω 1% 1/16W SMT0402 LR

R224 51Ω 5% 1/16W SMT0402 LR

R185 49.9Ω 1% 1/16W SMT0402 LR

R222 20Ω 1% 1/16W SMT0402 LR

R215 51Ω 5% 1/16W SMT0402 LR(NU)

C1135

470pF 50V 10% SMT0402 X7R LR

R203 100Ω 1% 1/16W SMT0402 LR

TP10

1

R220 68Ω 5% 1/16W SMT0402 LR

R205 130 Ω 1% 1/16W SMT0402 LR

Q123

TRANS M-FET-N BSS138_NL 50V 0.22A SOT-23 3PIN FAIRCHILD LR

D

G

S

R195 0Ω 5% 1/16W SMT0402 LR(NU)

R216 0Ω 5% 1/16W SMT0402 LR(NU)

R214

SHW 0 5% 1/16W 0402

R218 RES 1KΩ 5% 1/16W SMT0402 LR

R1080

100KΩ 1% 1/16W SMT0402 LR

R193 0Ω 5% 1/16W SMT0402 LR

R225 51Ω 5% 1/16W SMT0402 LR(NU)

R221 750Ω 1% 1/16W SMT0402 LR

R1077

0Ω 5% 1/16W SMT0402 LR(NU)

R208

750Ω 1% 1/16W SMT0402 LR

TP6

1

TP4

1

R196 51Ω 5% 1/16W SMT0402 LR(NU)

R183

SHW 0 5% 1/16W 0402

R192 51Ω 5% 1/16W SMT0402 LR(NU)

R188

10KΩ 5% 1/16W SMT0402 LR

R229 51Ω 5% 1/16W SMT0402 LR

R204 24.9Ω 1% 1/16W SMT0402 LR

R201

1.5KΩ 1% 1/16W SMT0402 LR

TP18

1

TP19

1

R184

RES 1.1KΩ 1% 1/16W SMT0402 LR(NU)

CLOCKS

MISC THERMAL

PWR MANAGEMENT

DDR3

MISC

JTAG & BPM

U13B

mPGA989B

AM1

AN1

F6

AL1

B16

A16

AT30

AR30

D16

E16

A17

A18

AK14

AT23

AT15

AN26

AK15

AP26

AN14

AN27

AK13

AM15

AL14

AN15

AP15

AT28

AP27

AN28

AP28

AT27

AT29

AR27

AR29

AP29

AN25

AJ22

AK22

AK24

AJ24

AJ25

AH22

AK23

AH23

AT24

AL15

AM26

G16

AT26

AH24

SM_RCOMP[1]

SM_RCOMP[2]

SM_DRAMRST#

SM_RCOMP[0]

BCLK#

BCLK

BCLK_ITP#

BCLK_ITP

PEG_CLK#

PEG_CLK

DPLL_REF_SSCLK#

DPLL_REF_SSCLK

CATERR#

COMP3

PECI

PROCHOT#

THERMTRIP#

RESET_OBS#

VCCPWRGOOD_1

VCCPWRGOOD_0

SM_DRAMPWROK

VTTPWRGOOD

RSTIN#

PM_EXT_TS#[0]

PM_EXT_TS#[1]

PRDY#

PREQ#

TCK

TMS

TRST#

TDI

TDO

TDI_M

TDO_M

DBR#

BPM#[0]

BPM#[1]

BPM#[2]

BPM#[3]

BPM#[4]

BPM#[5]

BPM#[6]

BPM#[7]

COMP2

PM_SYNC

TAPPWRGOOD

COMP1

COMP0

SKTOCC#

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜

信息提交成功

信息提交成功