Table of Contents

1 特性................................................................................... 1

2 应用................................................................................... 2

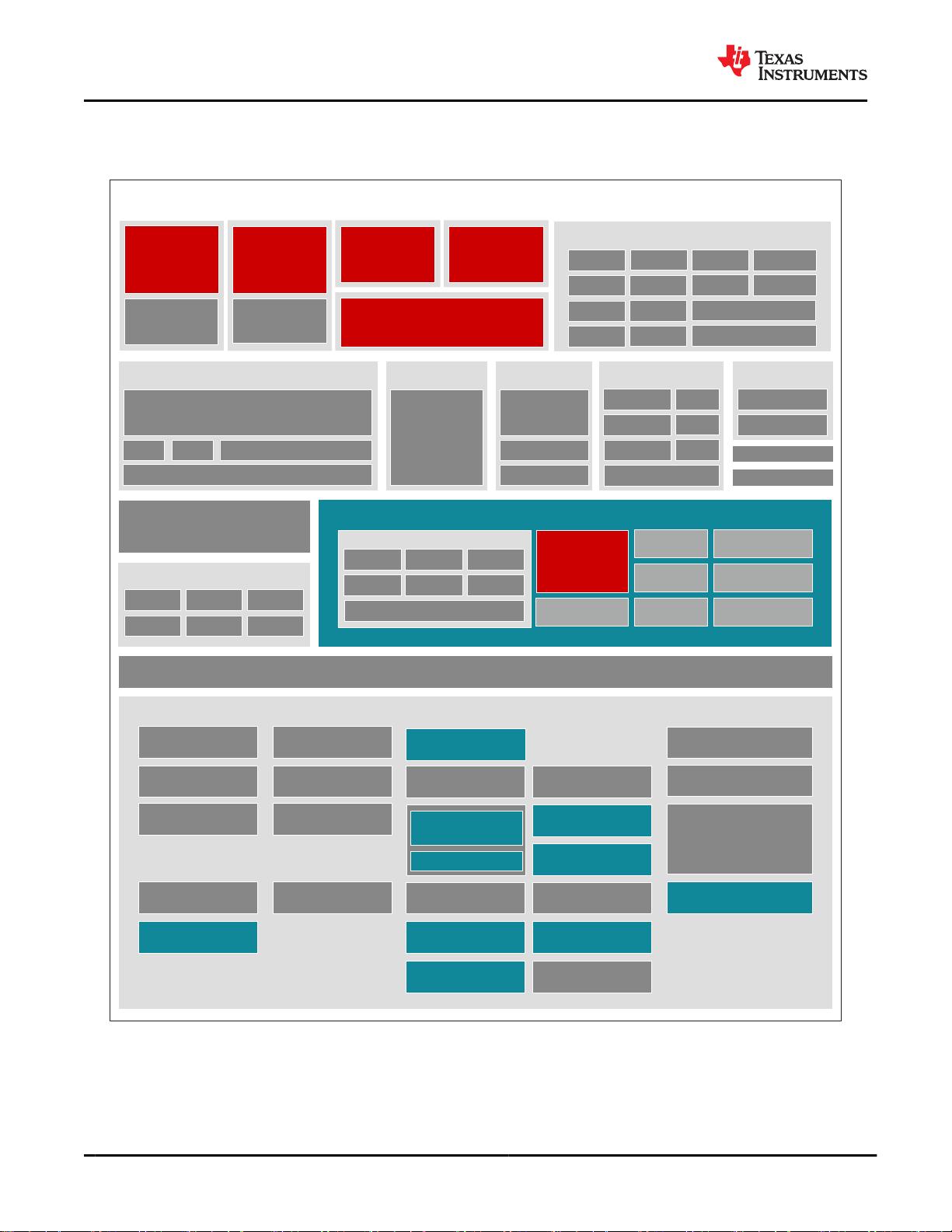

3 说明................................................................................... 3

3.1 功能模块图.................................................................. 4

4 Revision History.............................................................. 5

5 Device Comparison......................................................... 9

5.1 Related Products...................................................... 12

6 Terminal Configuration and Functions........................13

6.1 Pin Diagram.............................................................. 13

6.2 Pin Attributes.............................................................14

6.3 Signal Descriptions................................................... 82

6.4 Pin Multiplexing.......................................................138

6.5 Connections for Unused Pins................................. 153

7 Specifications.............................................................. 156

7.1 Absolute Maximum Ratings.................................... 156

7.2 ESD Ratings........................................................... 160

7.3 Power-On-Hour (POH) Limits................................. 160

7.4 Recommended Operating Conditions.....................160

7.5 Operating Performance Points................................163

7.6 Power Consumption Summary............................... 163

7.7 Electrical Characteristics.........................................164

7.8 VPP Specifications for One-Time Programmable

(OTP) eFuses............................................................171

7.9 Thermal Resistance Characteristics....................... 173

7.10 Timing and Switching Characteristics................... 174

8 Detailed Description....................................................291

8.1 Overview................................................................. 291

8.2 Processor Subsystems........................................... 292

8.3 Accelerators and Coprocessors..............................293

8.4 Other Subsystems.................................................. 295

9 Applications and Implementation.............................. 304

9.1 Power Supply Mapping........................................... 304

9.2 Device Connection and Layout Fundamentals....... 307

9.3 Peripheral- and Interface-Specific Design

Information................................................................ 309

10 Device and Documentation Support........................314

10.1 Device Nomenclature............................................314

10.2 Tools and Software............................................... 316

10.3 Documentation Support........................................ 317

10.4 支持资源................................................................317

10.5 Trademarks........................................................... 317

10.6 Electrostatic Discharge Caution............................317

10.7 术语表................................................................... 317

11 Mechanical, Packaging, and Orderable

Information.................................................................. 318

11.1 Packaging Information.......................................... 318

4 Revision History

Changes from July 22, 2021 to August 27, 2021 (from Revision I (July 2021) to Revision J

(August 2021)) Page

• 通篇:删除了引用的“DMIPS”.........................................................................................................................1

• (Device Comparison): Deleted "MCU Island with Lockstep Arm Cortex-R5Fs" row, as info in Lockstep and

Safety Targeted rows. ........................................................................................................................................ 9

• (Pin Attributes): Updated Buffer Types for MCU_PORz and PORz to FS Reset..............................................14

• Updated USB0/1_RCALIB note to indicate the pin must be connected with an external resistor to VSS even

when unused.................................................................................................................................................. 106

• Updated REXT pin note to show it should always be connected through an external resistor to VSS, even

when unused.................................................................................................................................................. 106

• Added clarification notes to MMC1_SDCD and MMC2_SDCD signals about pulled down requirement........112

• Updated CSI0 Signal Descriptions and CSI1 Signal Descriptions to show the RCALIB pins must be

connected to VSS through the external resistor even when unused.............................................................. 128

• (DSI_TX0 Signal Descriptions): Updated RCALIB pin description to show the pin must be connected to VSS

through an external resistor even when unused.............................................................................................129

• Added note indicting power balls should be connected to voltage specified in Recommended Operating

Conditions when unused................................................................................................................................ 134

• Added SERDES[0:4]_REXT rows in Connections for Unused Pins, these pins need to be connected to VSS

when unused.................................................................................................................................................. 153

• Showed VMON balls should be connected to PWR if unused in Connections for Unused Pins. Also added

note specifying MMC1_SDCD and MMC2_SDCD should be pulled down to function properly ....................153

• Showed CSI[1:0]_RXRCALIB, DSI_TXRCALIB, USB[1:0]_RCALIB pins should be connected to VSS is

unused in Connections for Unused Pins ........................................................................................................153

• Updated Specifications and removed note saying specifications are preliminary.......................................... 156

• (Speed Grade Maximum Frequency): Updated/Changed LPDDR4 frequency for L and E speed grades from

"4266" and "3733" MT/s to "3733" and "3200" MT/s, respectively................................................................. 163

www.ti.com.cn

TDA4VM-Q1, TDA4VM

ZHCSKP3J – FEBRUARY 2019 – REVISED AUGUST 2021

Copyright © 2021 Texas Instruments Incorporated

Submit Document Feedback

5

Product Folder Links: TDA4VM-Q1 TDA4VM

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜

信息提交成功

信息提交成功

评论6