A

A

B

B

C

C

D

D

E

E

1 1

2 2

3 3

4 4

Title

Size Document Number Rev

Date: Sheet of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

LA-8224P

0.2

Cover Sheet

Custom

1 59Thursday, October 27, 2011

2011/07/12 2012/12/31

Title

Size Document Number Rev

Date: Sheet of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

LA-8224P

0.2

Cover Sheet

Custom

1 59Thursday, October 27, 2011

2011/07/12 2012/12/31

Title

Size Document Number Rev

Date: Sheet of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

LA-8224P

0.2

Cover Sheet

Custom

1 59Thursday, October 27, 2011

2011/07/12 2012/12/31

Compal Confidential

QCL40 MB Schematic Document

2011.09.28

Rev: 0.2

Compal Electronics, Inc.

LA-8224P

1

1

2

2

3

3

4

4

5

5

A A

B B

C C

D D

Title

Size Document Number Rev

Date: Sheet of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

LA-8224P

0.2

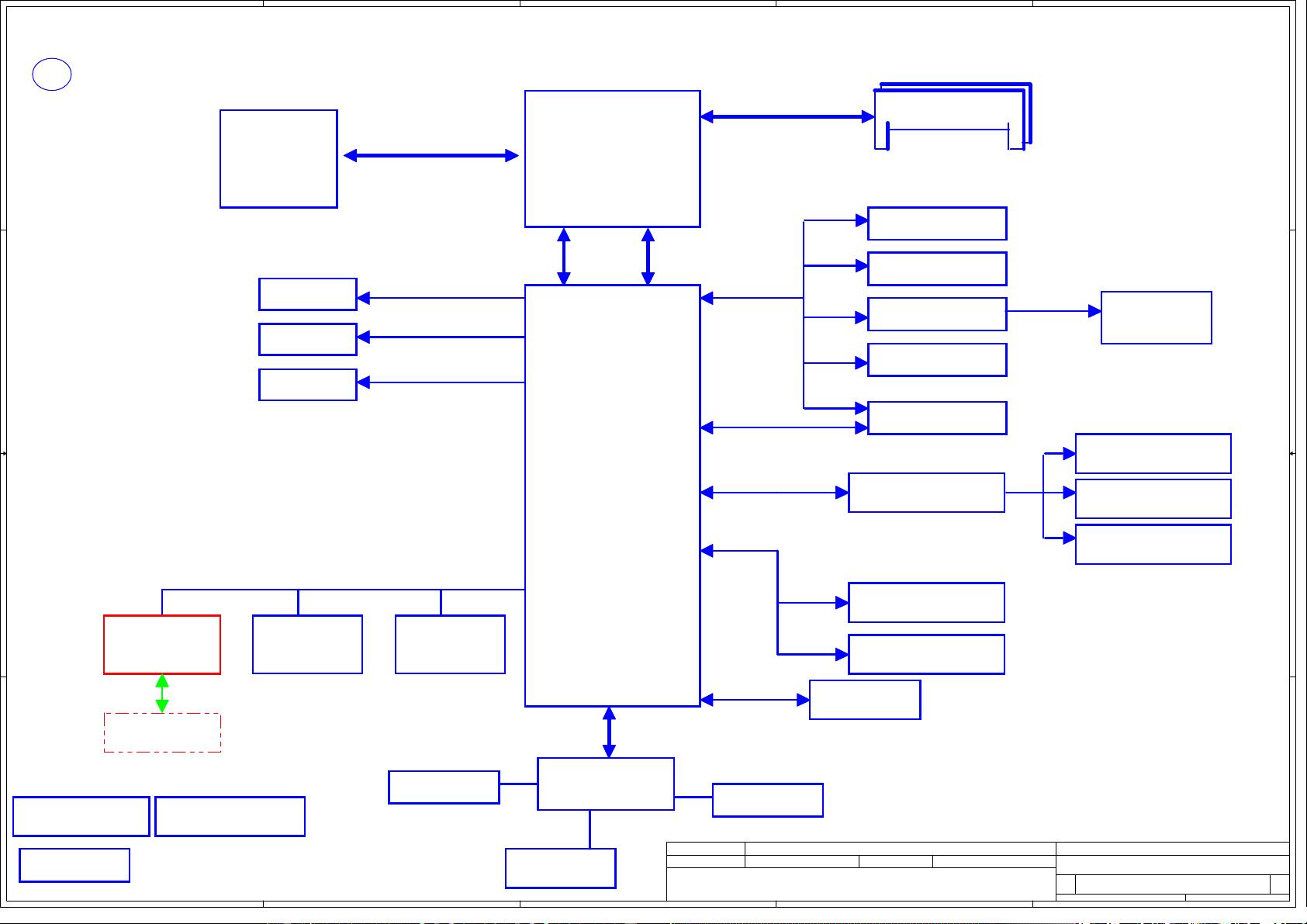

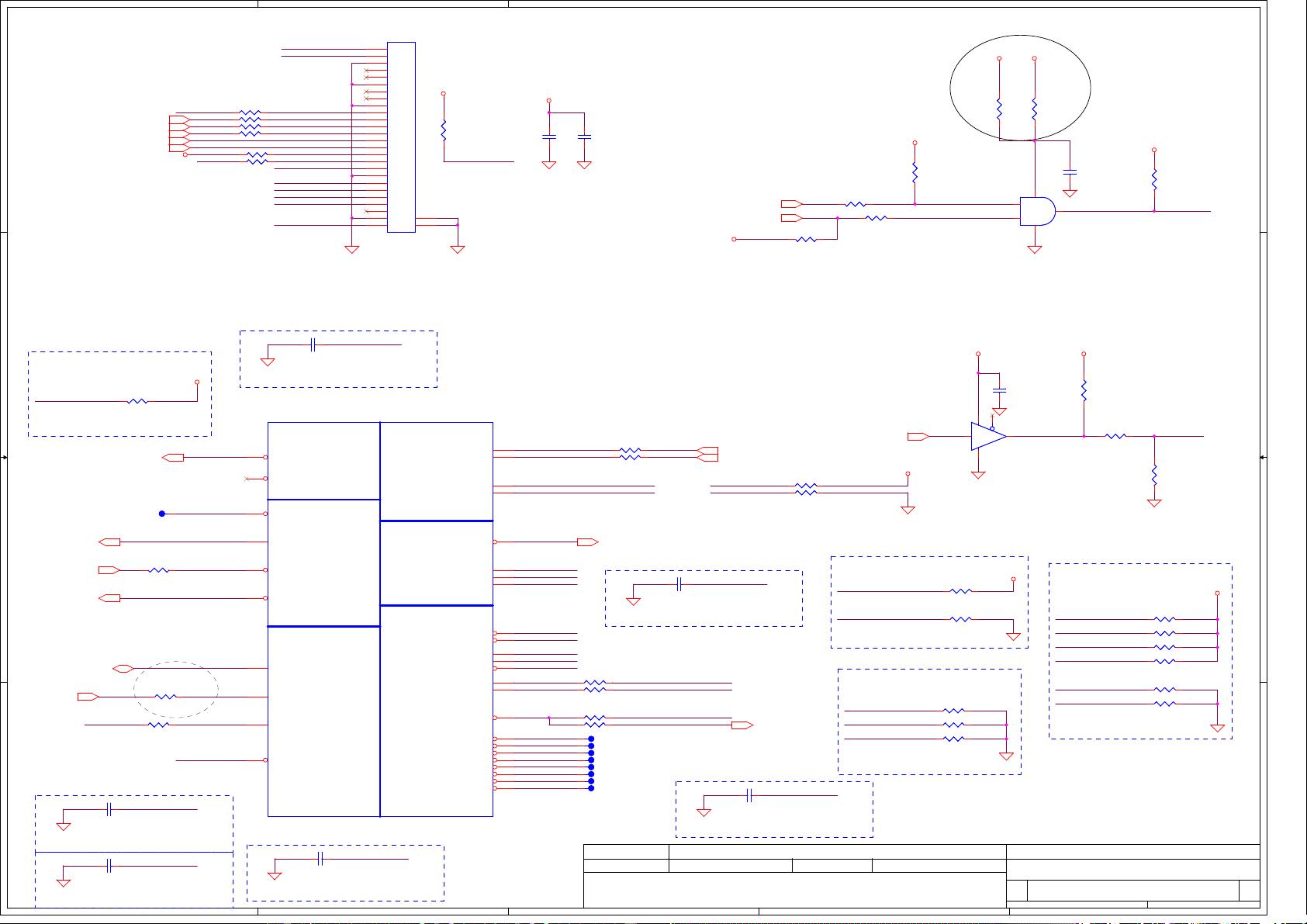

Block Diagram

Custom

2 59Thursday, October 27, 2011

2011/07/12 2012/12/31

Compal Electronics, Inc.

Title

Size Document Number Rev

Date: Sheet of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

LA-8224P

0.2

Block Diagram

Custom

2 59Thursday, October 27, 2011

2011/07/12 2012/12/31

Compal Electronics, Inc.

Title

Size Document Number Rev

Date: Sheet of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

LA-8224P

0.2

Block Diagram

Custom

2 59Thursday, October 27, 2011

2011/07/12 2012/12/31

Compal Electronics, Inc.

Compal Confidential

Fan Control

Mobile

Processor

LPC BUS

DC/DC Interface CKT.

page 39

Touch Pad CONN.

Int. KBD

Page 29,41

ENE KB9012QF

10/100/1000 LAN

Realtek GbE

PCI-e

QCL40

Page 10, 11

Page 37

Page 4 ~ 9

Page 32

LCD conn

BANK 0, 1, 2, 3

DDR3-SO-DIMM X 2

DDR3 1333/1600MHz 1.5V

Dual Channel

CRT Conn

Realtek

ALC269

Audio Jack (HP)

USB2.0

Azalia

Ivy Bridge

Page 38

Page 38

Page 30

Page 30

Page 35

HDMI

Mini Card-1

Page 40

WLAN

Bluetooth

LVDS, EDID, DISPOFF#, PWM

rPGA 988B Socket

Page 39

SPI ROM

256KB

+VCC_CORE, +VCCP,

+VCC_GFXCORE_AVG, +1.5V_CPU_VDDQ,

+1.8VS, _VCCSA

+1.5V, +0.75VS

Page 33

+3VLP/+3VALW

Page 12

SPI ROM

4MB+2MB

SPI

FCBGA 989 Balls

PCH

PANTHER-POINT

Intel

Page 12 ~ 19

+1.05VS, +1.8VS, +3VS,

+3V_PCH, +5V_PCH, +RTCVCC,

+VCCAFDI_VRM

100MHz

100MHz

5GB/s

FDI x8

DMI x4

2.7GT/s

(UMA)

HM77

port 0

port 2port 1

RGB, HV Sync, DDC

RTL8111F

HDMI, DDC

Audio Jack (MIC)

Speaker Connector

Page 33

PCB P/N for Load BOM

USB Board

port 4

Page 33

USB conn x1

SATA

port 0,1

Card Reader

RTS5137

Page 34

port 10

LAN/CRT Board

port 2

Page 30

port 8

Reserve KB930F

USB3.0

USB3.0 conn x2

port 1,2

Page 36

Camera

Page 31

2.5" SATA HDD Connector

SATA ODD Connector

Page 31

MiniCard-2

Page 40

port 9

PEG 16X

Memory Card Slot

SD/MMC

Page 34

Page 20 ~ 28

Page 33

Page 33

LS-4221P

USB/B

External board

Page 33

NV

N13M-GE1

Gb1B-64

23x23mm

port 4

page 36

ASM1042 USB3.0

Controller

Page 37

USB3.0 conn x2

ZZZ1

PCB-MB

DA80000QT00

ZZZ1

PCB-MB

DA80000QT00

A

A

1 1

Title

Size Document Number Rev

Date: Sheet of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

LA-8224P

0.2

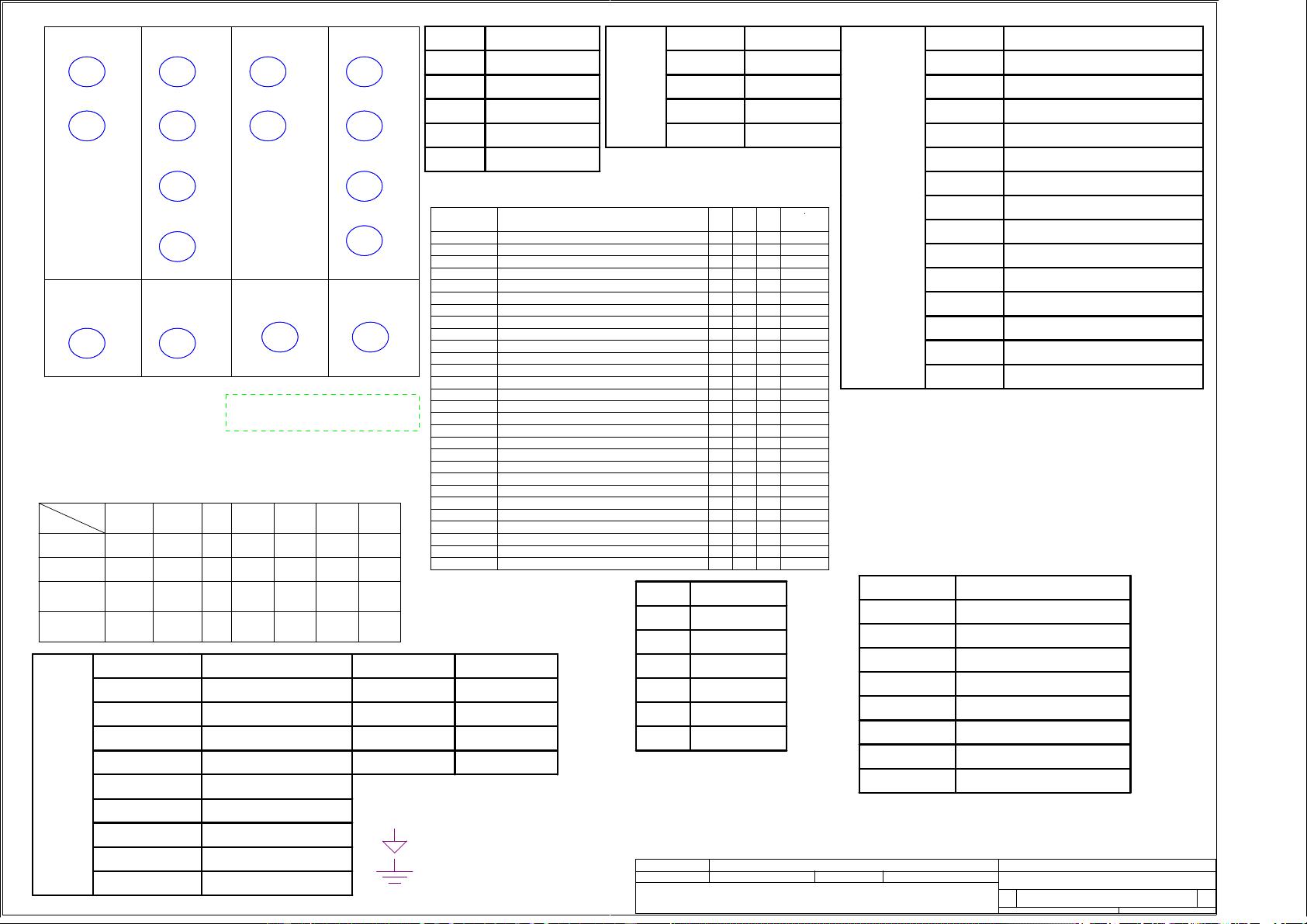

Notes List

C

3 59Thursday, October 27, 2011

2011/07/12 2012/12/31

Title

Size Document Number Rev

Date: Sheet of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

LA-8224P

0.2

Notes List

C

3 59Thursday, October 27, 2011

2011/07/12 2012/12/31

Title

Size Document Number Rev

Date: Sheet of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

LA-8224P

0.2

Notes List

C

3 59Thursday, October 27, 2011

2011/07/12 2012/12/31

Symbol Note :

: means Digital Ground

: means Analog Ground

PCH

EC_SMB_CK2

SOURCE

KB930

MINI1 BATT SODIMM

SMBUS Control Table

PCH_SMBCLK

PCH_SMBDATA PCH

EC_SMB_DA2

EC_SMB_CK1

EC_SMB_DA1

KB930

PCH_SMLCLK

PCH

X

X

X X

X

X

X

X

X

V

X

PCH_SMLDATA

V

CAMERA

JMINI1 (WLAN)

8

9

10

Bluetooth

11

2

3

1

4

USB2 PORT

0

DESTINATION

6

5

7

12

13

PCH

X

ODD

HDD

SATA5

SATA4

SATA3

SATA2

SATA1

DESTINATION

SATA0

SATA

MINI CARD WLAN

Lane 7

Lane 8

Lane 5

Lane 6

PCI EXPRESS

Lane 1

DESTINATION

Lane 2

Lane 3

Lane 4

10/100/1G LAN

None

None

None

CLKOUT_PCIE7 None

NoneCLKOUT_PCIE6

CLKOUT_PCIE4

CLKOUT_PCIE5

CLKOUT_PCIE1

CLKOUT_PCIE2

CLKOUT_PCIE3

CLKOUT_PCIE0

DESTINATIONDIFFERENTIAL

CLK

CLKOUT_PEG_B

FLEX CLOCKS DESTINATION

CLKOUTFLEX1

CLKOUTFLEX2

CLKOUTFLEX3

CLKOUTFLEX010/100/1G LAN

None

V

Card Reader

Compal Electronics, Inc.

PCH_LOOPBACK

EC

PCI0

CLKOUT

None

PCI1

PCI2

PCI3

DESTINATION

CLK_SD_48M

PCI4

LPC Debug Port

DGPU

V

V

X

X

None

V

X

EC

X

X

X

V

None

USB2

None

None

None

None

MINI CARD WLAN

None

None

None

None

None

None

None

None

None

None

None

None

DIS@:

VGA componet

9012@:

EC(ENE 9012 chip)

XDP@:

Intel debug port

4

3

2

DESTINATION

1

None

USB3 PORT

None

USB2.0+3.0

USB2.0+3.0

USB2.0+3.0

USB2.0+3.0

PCH

930@:

EC(ENE 930 chip)

None

None

VRAMX16X8 VRAMX16X4 VRAMX8X8

X76@:

None

N13P-GS N13P-GL N13M-GE1 N13M-GE1 x8

GS@ GL@ GE@ GE8@

+1.5VSG

+5VS_ODD

+1.5V

+VCCP

+1.05VSG

+1.8VS

+1.5V_CPU_VDDQ

ON

+1.05VS ON

ON

OFF

ON

OFF

ON

ON

OFF

OFF

ON

1.5V power rail for N13P,VRAM

5V power rail for SATA ODD

1.8V power rail for CPU,PCH

1.05V power rail for CPU VCCIO,PCH

1.05V power rail for N13P

1.5V power rail for DDR3 system memory

1.5V power rail CPU VDDQ

1.05V power rail for PCH

+5VS

OFF

ON

OFF

5V power rail for HDD,AUDIO,FAN,Touch PAD

+5V_PCH

+5VALW ON

ON

OFF

ON

5V power rail for PCH suspend well plane

5V always on power rail

+3VSG

+LCDVDD

ON

OFF OFF

ON

OFF OFF3.3V power rail for VGA

3.3V power rail for LCD

+3VS

3.3V power rail for DDR SPI,PCH,HDD,Audio,Card Reader

ON

+3VALW ON3.3V always on power rail

B+

Voltage Rails

VIN

BATT+

S1 S3 S5

N/A N/A N/A

N/AN/AN/A

Power Plane Description

Adapter power supply (19V)

Battery power supply (12.6V)

AC or battery power rail for power circuit

+LAN_IO OFF

ON3.3V power rail for ethernet

+3VS_WLAN ON

OFF3.3V power rail for WLAN/BT Combo

+3V_PCH ON

OFF OFF3.3V power rail for PCH suspend well plane

Deep

S3

N/A

N/A

N/A N/A N/A N/A

+3VLP

3.3V power rail for 51ON power management

ON ON ON ON

ON ON

AC/ON; DC/OFF

OFF

OFF OFF

ON

OFF OFF OFF

OFF

OFF

ON

AC/ON; DC/OFF

ON

OFF

OFF

OFF

OFF OFF OFF

OFF OFF OFF

OFF OFF

OFF OFF OFF

ON

OFF OFF OFF

ON

OFF OFF OFF

+1.5VS

+0.75VS

+VCCSA

+VCC_CORE

+VCC_GFXCORE_AXG

1.5V power rail for PCH,WLAN/BT combo

0.75V power rail for DDR VREF

VCCSA for CPU system agent

CORE Voltage for CPU

1.5V power rail for N13P,VRAM

ON

OFF OFF OFF

ON

OFF OFF OFF

ON

ON

ON

OFF

OFF

OFF

OFF

OFF

OFF

OFF

OFFOFF

+VGA_CORE

CORE Voltage for N13P Graphics ON OFF OFF

ON

OFF OFF OFF

ON

USB3.0 by PCH

IU3@:

USB3.0 controller IC

USB30@:

USB3.0 controller

USB3.0 controller

AI@:

AI Charger

Non AI Charger

NAI@:

GE8@:

N13M-GE1_GB1b

ON

N13M-GE1 x8N13M-GE1N13P-GLN13P-GS

ER39

ZZZ4

1G HYN

X76L04@ZZZ4

1G HYN

X76L04@

ZZZ

2G SAM

X76L01@ZZZ

2G SAM

X76L01@

ZZZ5

1G SAM

X76L05@ZZZ5

1G SAM

X76L05@

U10

N13M-GE1 x8

GE8@U10

N13M-GE1 x8

GE8@

ZZZ8

2G ELP

X76L08@ZZZ8

2G ELP

X76L08@

U10

N13P-GL

GL@U10

N13P-GL

GL@

ZZZ10

4G HYN

X76L10@ZZZ10

4G HYN

X76L10@

ZZZ11

2G HYN

X76L11@ZZZ11

2G HYN

X76L11@ ZZZ3

1G SAM

X76L03@ZZZ3

1G SAM

X76L03@

ZZZ6

1G HYN

X76L06@ZZZ6

1G HYN

X76L06@

U10

N13M-GE1

GE@U10

N13M-GE1

GE@

ZZZ7

2G HYN

X76L07@ZZZ7

2G HYN

X76L07@

ZZZ12

2G SAM

X76L12@ZZZ12

2G SAM

X76L12@

U10

N13P-GS

GS@U10

N13P-GS

GS@

ZZZ2

2G HYN

X76L02@ZZZ2

2G HYN

X76L02@

ZZZ9

4G ELP

X76L09@ZZZ9

4G ELP

X76L09@

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

FDI_CTX_PRX_N1

FDI_CTX_PRX_N4

FDI_CTX_PRX_N6

FDI_CTX_PRX_P1

FDI_CTX_PRX_P6

FDI_FSYNC0

FDI_CTX_PRX_N0

FDI_CTX_PRX_N2

FDI_CTX_PRX_N3

FDI_CTX_PRX_N5

FDI_CTX_PRX_N7

FDI_CTX_PRX_P0

FDI_CTX_PRX_P2

FDI_CTX_PRX_P3

FDI_CTX_PRX_P4

FDI_CTX_PRX_P5

FDI_CTX_PRX_P7

FDI_LSYNC0

FDI_LSYNC1

FDI_FSYNC1

FDI_INT

PEG_COMP

EDP_COMP

PCIE_CTX_GRX_N13

PCIE_CTX_GRX_N14

PCIE_CTX_GRX_N15

PCIE_CTX_GRX_N11

PCIE_CTX_GRX_N8

PCIE_CTX_GRX_N12

PCIE_CTX_GRX_N10

PCIE_CTX_GRX_N7

PCIE_CTX_GRX_N6

PCIE_CTX_GRX_N5

PCIE_CTX_GRX_N9

PCIE_CTX_GRX_N4

PCIE_CTX_GRX_N3

PCIE_CTX_GRX_N0

PCIE_CTX_GRX_N1

PCIE_CTX_GRX_N2

PCIE_CTX_GRX_P14

PCIE_CTX_GRX_P8

PCIE_CTX_GRX_P13

PCIE_CTX_GRX_P12

PCIE_CTX_GRX_P15

PCIE_CTX_GRX_P11

PCIE_CTX_GRX_P10

PCIE_CTX_GRX_P7

PCIE_CTX_GRX_P4

PCIE_CTX_GRX_P5

PCIE_CTX_GRX_P6

PCIE_CTX_GRX_P9

PCIE_CTX_GRX_P0

PCIE_CTX_GRX_P1

PCIE_CTX_GRX_P2

PCIE_CTX_GRX_P3

PCIE_CTX_C_GRX_P8

PCIE_CTX_C_GRX_P14

PCIE_CTX_C_GRX_P13

PCIE_CTX_C_GRX_P10

PCIE_CTX_C_GRX_P11

PCIE_CTX_C_GRX_P15

PCIE_CTX_C_GRX_P12

PCIE_CTX_C_GRX_P0

PCIE_CTX_C_GRX_P6

PCIE_CTX_C_GRX_P9

PCIE_CTX_C_GRX_P5

PCIE_CTX_C_GRX_P4

PCIE_CTX_C_GRX_P7

PCIE_CTX_C_GRX_P3

PCIE_CTX_C_GRX_P2

PCIE_CTX_C_GRX_P1

PCIE_CTX_C_GRX_N15

PCIE_CTX_C_GRX_N0

PCIE_CTX_C_GRX_N10

PCIE_CTX_C_GRX_N5

PCIE_CTX_C_GRX_N8

PCIE_CTX_C_GRX_N4

PCIE_CTX_C_GRX_N6

PCIE_CTX_C_GRX_N7

PCIE_CTX_C_GRX_N13

PCIE_CTX_C_GRX_N1

PCIE_CTX_C_GRX_N9

PCIE_CTX_C_GRX_N3

PCIE_CTX_C_GRX_N11

PCIE_CTX_C_GRX_N14

PCIE_CTX_C_GRX_N2

PCIE_CTX_C_GRX_N12

PCIE_GTX_C_CRX_N15

PCIE_GTX_C_CRX_N8

PCIE_GTX_C_CRX_N14

PCIE_GTX_C_CRX_N10

PCIE_GTX_C_CRX_N5

PCIE_GTX_C_CRX_N9

PCIE_GTX_C_CRX_N0

PCIE_GTX_C_CRX_P4

PCIE_GTX_C_CRX_P8

PCIE_GTX_C_CRX_P0

PCIE_GTX_C_CRX_P15

PCIE_GTX_C_CRX_P13

PCIE_GTX_C_CRX_P14

PCIE_GTX_C_CRX_P9

PCIE_GTX_C_CRX_P12

PCIE_GTX_C_CRX_P1

PCIE_GTX_C_CRX_N13

PCIE_GTX_C_CRX_N12

PCIE_GTX_C_CRX_N11

PCIE_GTX_C_CRX_N7

PCIE_GTX_C_CRX_N6

PCIE_GTX_C_CRX_N4

PCIE_GTX_C_CRX_N3

PCIE_GTX_C_CRX_N2

PCIE_GTX_C_CRX_N1

PCIE_GTX_C_CRX_P11

PCIE_GTX_C_CRX_P10

PCIE_GTX_C_CRX_P7

PCIE_GTX_C_CRX_P6

PCIE_GTX_C_CRX_P5

PCIE_GTX_C_CRX_P3

PCIE_GTX_C_CRX_P2

PCIE_GTX_CRX_P0

PCIE_GTX_CRX_P1

PCIE_GTX_CRX_P2

PCIE_GTX_CRX_P3

PCIE_GTX_CRX_P4

PCIE_GTX_CRX_P5

PCIE_GTX_CRX_P6

PCIE_GTX_CRX_P7

PCIE_GTX_CRX_P8

PCIE_GTX_CRX_P9

PCIE_GTX_CRX_P10

PCIE_GTX_CRX_P11

PCIE_GTX_CRX_P12

PCIE_GTX_CRX_P13

PCIE_GTX_CRX_P14

PCIE_GTX_CRX_P15

PCIE_GTX_CRX_N0

PCIE_GTX_CRX_N1

PCIE_GTX_CRX_N2

PCIE_GTX_CRX_N3

PCIE_GTX_CRX_N4

PCIE_GTX_CRX_N5

PCIE_GTX_CRX_N6

PCIE_GTX_CRX_N7

PCIE_GTX_CRX_N8

PCIE_GTX_CRX_N9

PCIE_GTX_CRX_N10

PCIE_GTX_CRX_N11

PCIE_GTX_CRX_N12

PCIE_GTX_CRX_N13

PCIE_GTX_CRX_N14

PCIE_GTX_CRX_N15

DMI_CTX_PRX_P014

DMI_CRX_PTX_P014

DMI_CTX_PRX_N114

DMI_CRX_PTX_N114

DMI_CTX_PRX_P314

DMI_CRX_PTX_P314

DMI_CTX_PRX_P214

DMI_CTX_PRX_N014

DMI_CRX_PTX_N314

DMI_CRX_PTX_P214

DMI_CTX_PRX_N314

DMI_CTX_PRX_P114

DMI_CRX_PTX_N014

DMI_CRX_PTX_N214

DMI_CRX_PTX_P114

DMI_CTX_PRX_N214

FDI_CTX_PRX_N014

FDI_CTX_PRX_N114

FDI_CTX_PRX_N214

FDI_CTX_PRX_N314

FDI_CTX_PRX_N414

FDI_CTX_PRX_N514

FDI_CTX_PRX_N614

FDI_CTX_PRX_N714

FDI_CTX_PRX_P014

FDI_CTX_PRX_P114

FDI_CTX_PRX_P214

FDI_CTX_PRX_P314

FDI_CTX_PRX_P414

FDI_CTX_PRX_P514

FDI_CTX_PRX_P614

FDI_CTX_PRX_P714

FDI_FSYNC014

FDI_FSYNC114

FDI_INT14

FDI_LSYNC014

FDI_LSYNC114

PCIE_CTX_C_GRX_P[0..15] 20

PCIE_CTX_C_GRX_N[0..15] 20

PCIE_GTX_C_CRX_P[0..15] 20

PCIE_GTX_C_CRX_N[0..15] 20

+1.05VS

+1.05VS

Title

Size Document Number Rev

Date: Sheet of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

LA-8224P

0.2

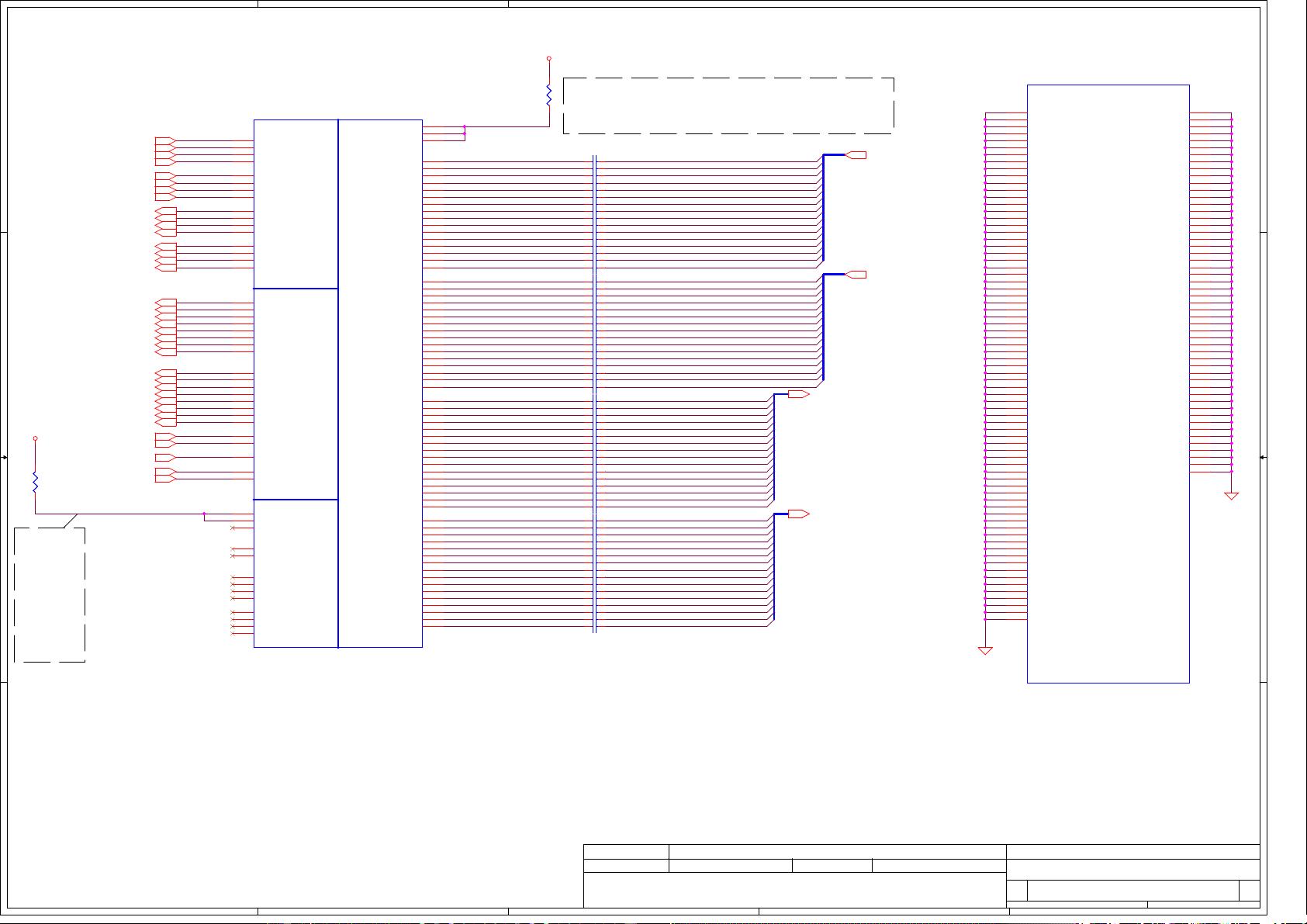

PROCESSOR(1/6) DMI,FDI,PEG

Custom

4 59Thursday, October 27, 2011

2011/07/12 2012/12/31

Title

Size Document Number Rev

Date: Sheet of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

LA-8224P

0.2

PROCESSOR(1/6) DMI,FDI,PEG

Custom

4 59Thursday, October 27, 2011

2011/07/12 2012/12/31

Title

Size Document Number Rev

Date: Sheet of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

LA-8224P

0.2

PROCESSOR(1/6) DMI,FDI,PEG

Custom

4 59Thursday, October 27, 2011

2011/07/12 2012/12/31

PEG_ICOMPI and RCOMPO signals should be shorted and routed

with - max length = 500 mils - typical impedance = 43 mohms

PEG_ICOMPO signals should be routed with - max length = 500 mils

- typical impedance = 14.5 mohms

eDP_COMPIO

and ICOMPO

signals

should be

shorted

near balls

and routed

with

typical

impedance

<25 mohms

Compal Electronics, Inc.

C34 0.22U_0402_10V6KDIS@ C34 0.22U_0402_10V6KDIS@

1 2

C64 0.22U_0402_10V6KDIS@ C64 0.22U_0402_10V6KDIS@

1 2

C22 0.22U_0402_10V6KDIS@ C22 0.22U_0402_10V6KDIS@

1 2

C61 0.22U_0402_10V6KDIS@ C61 0.22U_0402_10V6KDIS@

1 2

C47 0.22U_0402_10V6KDIS@ C47 0.22U_0402_10V6KDIS@

1 2

C2 0.22U_0402_10V6KDIS@ C2 0.22U_0402_10V6KDIS@

1 2

C7 0.22U_0402_10V6KDIS@ C7 0.22U_0402_10V6KDIS@

1 2

C33 0.22U_0402_10V6KDIS@ C33 0.22U_0402_10V6KDIS@

1 2

C20 0.22U_0402_10V6KDIS@ C20 0.22U_0402_10V6KDIS@

1 2

C50 0.22U_0402_10V6KDIS@ C50 0.22U_0402_10V6KDIS@

1 2

C58 0.22U_0402_10V6KDIS@ C58 0.22U_0402_10V6KDIS@

1 2

C9 0.22U_0402_10V6KDIS@ C9 0.22U_0402_10V6KDIS@

1 2

C46 0.22U_0402_10V6KDIS@ C46 0.22U_0402_10V6KDIS@

1 2

C29 0.22U_0402_10V6KDIS@ C29 0.22U_0402_10V6KDIS@

1 2

C12 0.22U_0402_10V6KDIS@ C12 0.22U_0402_10V6KDIS@

1 2

C23 0.22U_0402_10V6KDIS@ C23 0.22U_0402_10V6KDIS@

1 2

C14 0.22U_0402_10V6KDIS@ C14 0.22U_0402_10V6KDIS@

1 2

C32 0.22U_0402_10V6KDIS@ C32 0.22U_0402_10V6KDIS@

1 2

C52 0.22U_0402_10V6KDIS@ C52 0.22U_0402_10V6KDIS@

1 2

C53 0.22U_0402_10V6KDIS@ C53 0.22U_0402_10V6KDIS@

1 2

C62 0.22U_0402_10V6KDIS@ C62 0.22U_0402_10V6KDIS@

1 2

C16 0.22U_0402_10V6KDIS@ C16 0.22U_0402_10V6KDIS@

1 2

C3 0.22U_0402_10V6KDIS@ C3 0.22U_0402_10V6KDIS@

1 2

C6 0.22U_0402_10V6KDIS@ C6 0.22U_0402_10V6KDIS@

1 2

C60 0.22U_0402_10V6KDIS@ C60 0.22U_0402_10V6KDIS@

1 2

C27 0.22U_0402_10V6KDIS@ C27 0.22U_0402_10V6KDIS@

1 2

C43 0.22U_0402_10V6KDIS@ C43 0.22U_0402_10V6KDIS@

1 2

C44 0.22U_0402_10V6KDIS@ C44 0.22U_0402_10V6KDIS@

1 2

C25 0.22U_0402_10V6KDIS@ C25 0.22U_0402_10V6KDIS@

1 2

C45 0.22U_0402_10V6KDIS@ C45 0.22U_0402_10V6KDIS@

1 2

VSS

JCPU1I

TYCO_2013620-2_IVY BRIDGE

CONN@

VSS

JCPU1I

TYCO_2013620-2_IVY BRIDGE

CONN@

VSS161

T35

VSS162

T34

VSS163

T33

VSS164

T32

VSS165

T31

VSS166

T30

VSS167

T29

VSS168

T28

VSS169

T27

VSS170

T26

VSS171

P9

VSS172

P8

VSS173

P6

VSS174

P5

VSS175

P3

VSS176

P2

VSS177

N35

VSS178

N34

VSS179

N33

VSS180

N32

VSS181

N31

VSS182

N30

VSS183

N29

VSS184

N28

VSS185

N27

VSS186

N26

VSS187

M34

VSS188

L33

VSS189

L30

VSS190

L27

VSS191

L9

VSS192

L8

VSS193

L6

VSS194

L5

VSS195

L4

VSS196

L3

VSS197

L2

VSS198

L1

VSS199

K35

VSS200

K32

VSS201

K29

VSS202

K26

VSS203

J34

VSS204

J31

VSS205

H33

VSS206

H30

VSS207

H27

VSS208

H24

VSS209

H21

VSS210

H18

VSS211

H15

VSS212

H13

VSS213

H10

VSS214

H9

VSS215

H8

VSS216

H7

VSS217

H6

VSS218

H5

VSS219

H4

VSS220

H3

VSS221

H2

VSS222

H1

VSS223

G35

VSS224

G32

VSS225

G29

VSS226

G26

VSS227

G23

VSS228

G20

VSS229

G17

VSS230

G11

VSS231

F34

VSS232

F31

VSS233

F29

VSS234

F22

VSS235

F19

VSS236

E30

VSS237

E27

VSS238

E24

VSS239

E21

VSS240

E18

VSS241

E15

VSS242

E13

VSS243

E10

VSS244

E9

VSS245

E8

VSS246

E7

VSS247

E6

VSS248

E5

VSS249

E4

VSS250

E3

VSS251

E2

VSS252

E1

VSS253

D35

VSS254

D32

VSS255

D29

VSS256

D26

VSS257

D20

VSS258

D17

VSS259

C34

VSS260

C31

VSS261

C28

VSS262

C27

VSS263

C25

VSS264

C23

VSS265

C10

VSS266

C1

VSS267

B22

VSS268

B19

VSS269

B17

VSS270

B15

VSS271

B13

VSS272

B11

VSS273

B9

VSS274

B8

VSS275

B7

VSS276

B5

VSS277

B3

VSS278

B2

VSS279

A35

VSS280

A32

VSS281

A29

VSS282

A26

VSS283

A23

VSS284

A20

VSS285

A3

C63 0.22U_0402_10V6KDIS@ C63 0.22U_0402_10V6KDIS@

1 2

C57 0.22U_0402_10V6KDIS@ C57 0.22U_0402_10V6KDIS@

1 2

C51 0.22U_0402_10V6KDIS@ C51 0.22U_0402_10V6KDIS@

1 2

C56 0.22U_0402_10V6KDIS@ C56 0.22U_0402_10V6KDIS@

1 2

C17 0.22U_0402_10V6KDIS@ C17 0.22U_0402_10V6KDIS@

1 2

C26 0.22U_0402_10V6KDIS@ C26 0.22U_0402_10V6KDIS@

1 2

C15 0.22U_0402_10V6KDIS@ C15 0.22U_0402_10V6KDIS@

1 2

R1

24.9_0402_1%

R1

24.9_0402_1%

12

C49 0.22U_0402_10V6KDIS@ C49 0.22U_0402_10V6KDIS@

1 2

C38 0.22U_0402_10V6KDIS@ C38 0.22U_0402_10V6KDIS@

1 2

C37 0.22U_0402_10V6KDIS@ C37 0.22U_0402_10V6KDIS@

1 2

C28 0.22U_0402_10V6KDIS@ C28 0.22U_0402_10V6KDIS@

1 2

C8 0.22U_0402_10V6KDIS@ C8 0.22U_0402_10V6KDIS@

1 2

C13 0.22U_0402_10V6KDIS@ C13 0.22U_0402_10V6KDIS@

1 2

C55 0.22U_0402_10V6KDIS@ C55 0.22U_0402_10V6KDIS@

1 2

C10 0.22U_0402_10V6KDIS@ C10 0.22U_0402_10V6KDIS@

1 2

C40 0.22U_0402_10V6KDIS@ C40 0.22U_0402_10V6KDIS@

1 2

C30 0.22U_0402_10V6KDIS@ C30 0.22U_0402_10V6KDIS@

1 2

C41 0.22U_0402_10V6KDIS@ C41 0.22U_0402_10V6KDIS@

1 2

C21 0.22U_0402_10V6KDIS@ C21 0.22U_0402_10V6KDIS@

1 2

C36 0.22U_0402_10V6KDIS@ C36 0.22U_0402_10V6KDIS@

1 2

R2

24.9_0402_1%

R2

24.9_0402_1%

12

C24 0.22U_0402_10V6KDIS@ C24 0.22U_0402_10V6KDIS@

1 2

C18 0.22U_0402_10V6KDIS@ C18 0.22U_0402_10V6KDIS@

1 2

C42 0.22U_0402_10V6KDIS@ C42 0.22U_0402_10V6KDIS@

1 2

C1 0.22U_0402_10V6KDIS@ C1 0.22U_0402_10V6KDIS@

1 2

C35 0.22U_0402_10V6KDIS@ C35 0.22U_0402_10V6KDIS@

1 2

C59 0.22U_0402_10V6KDIS@ C59 0.22U_0402_10V6KDIS@

1 2

C39 0.22U_0402_10V6KDIS@ C39 0.22U_0402_10V6KDIS@

1 2

C54 0.22U_0402_10V6KDIS@ C54 0.22U_0402_10V6KDIS@

1 2

C11 0.22U_0402_10V6KDIS@ C11 0.22U_0402_10V6KDIS@

1 2

PCI EXPRESS* - GRAPHICS

DMI

Intel(R) FDI

eDP

JCPU1A

TYCO_2013620-2_IVY BRIDGE

CONN@

PCI EXPRESS* - GRAPHICS

DMI

Intel(R) FDI

eDP

JCPU1A

TYCO_2013620-2_IVY BRIDGE

CONN@

DMI_RX#[0]

B27

DMI_RX#[1]

B25

DMI_RX#[2]

A25

DMI_RX#[3]

B24

DMI_RX[0]

B28

DMI_RX[1]

B26

DMI_RX[2]

A24

DMI_RX[3]

B23

DMI_TX#[0]

G21

DMI_TX#[1]

E22

DMI_TX#[2]

F21

DMI_TX#[3]

D21

DMI_TX[0]

G22

DMI_TX[1]

D22

DMI_TX[3]

C21

DMI_TX[2]

F20

FDI0_TX#[0]

A21

FDI0_TX#[1]

H19

FDI0_TX#[2]

E19

FDI0_TX#[3]

F18

FDI1_TX#[0]

B21

FDI1_TX#[1]

C20

FDI1_TX#[2]

D18

FDI1_TX#[3]

E17

FDI0_TX[0]

A22

FDI0_TX[1]

G19

FDI0_TX[2]

E20

FDI0_TX[3]

G18

FDI1_TX[0]

B20

FDI1_TX[1]

C19

FDI1_TX[2]

D19

FDI1_TX[3]

F17

FDI0_FSYNC

J18

FDI1_FSYNC

J17

FDI_INT

H20

FDI0_LSYNC

J19

FDI1_LSYNC

H17

PEG_ICOMPI

J22

PEG_ICOMPO

J21

PEG_RCOMPO

H22

PEG_RX#[0]

K33

PEG_RX#[1]

M35

PEG_RX#[2]

L34

PEG_RX#[3]

J35

PEG_RX#[4]

J32

PEG_RX#[5]

H34

PEG_RX#[6]

H31

PEG_RX#[7]

G33

PEG_RX#[8]

G30

PEG_RX#[9]

F35

PEG_RX#[10]

E34

PEG_RX#[11]

E32

PEG_RX#[12]

D33

PEG_RX#[13]

D31

PEG_RX#[14]

B33

PEG_RX#[15]

C32

PEG_RX[0]

J33

PEG_RX[1]

L35

PEG_RX[2]

K34

PEG_RX[3]

H35

PEG_RX[4]

H32

PEG_RX[5]

G34

PEG_RX[6]

G31

PEG_RX[7]

F33

PEG_RX[8]

F30

PEG_RX[9]

E35

PEG_RX[10]

E33

PEG_RX[11]

F32

PEG_RX[12]

D34

PEG_RX[13]

E31

PEG_RX[14]

C33

PEG_RX[15]

B32

PEG_TX#[0]

M29

PEG_TX#[1]

M32

PEG_TX#[2]

M31

PEG_TX#[3]

L32

PEG_TX#[4]

L29

PEG_TX#[5]

K31

PEG_TX#[6]

K28

PEG_TX#[7]

J30

PEG_TX#[8]

J28

PEG_TX#[9]

H29

PEG_TX#[10]

G27

PEG_TX#[11]

E29

PEG_TX#[12]

F27

PEG_TX#[13]

D28

PEG_TX#[14]

F26

PEG_TX#[15]

E25

PEG_TX[0]

M28

PEG_TX[1]

M33

PEG_TX[2]

M30

PEG_TX[3]

L31

PEG_TX[4]

L28

PEG_TX[5]

K30

PEG_TX[6]

K27

PEG_TX[7]

J29

PEG_TX[8]

J27

PEG_TX[9]

H28

PEG_TX[10]

G28

PEG_TX[11]

E28

PEG_TX[12]

F28

PEG_TX[13]

D27

PEG_TX[14]

E26

PEG_TX[15]

D25

eDP_AUX

C15

eDP_AUX#

D15

eDP_TX[0]

C17

eDP_TX[1]

F16

eDP_TX[2]

C16

eDP_TX[3]

G15

eDP_TX#[0]

C18

eDP_TX#[1]

E16

eDP_TX#[2]

D16

eDP_TX#[3]

F15

eDP_COMPIO

A18

eDP_HPD#

B16

eDP_ICOMPO

A17

C4 0.22U_0402_10V6KDIS@ C4 0.22U_0402_10V6KDIS@

1 2

C5 0.22U_0402_10V6KDIS@ C5 0.22U_0402_10V6KDIS@

1 2

C48 0.22U_0402_10V6KDIS@ C48 0.22U_0402_10V6KDIS@

1 2

C31 0.22U_0402_10V6KDIS@ C31 0.22U_0402_10V6KDIS@

1 2

C19 0.22U_0402_10V6KDIS@ C19 0.22U_0402_10V6KDIS@

1 2

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

H_THERMTRIP#

H_PROCHOT#_R

H_PM_SYNC

H_CPUPWRGD

VDDPWRGOOD_R

BUF_CPU_RST#

SM_RCOMP1

SM_RCOMP2

SM_RCOMP0

XDP_PRDY#

XDP_PREQ#

XDP_TCK

XDP_TMS

XDP_TRST#

H_DRAMRST#

XDP_DBRESET#

XDP_TDI

XDP_TDO

XDP_TDI_R

XDP_TDO_R

XDP_BPM#1

XDP_BPM#2

XDP_BPM#3

XDP_BPM#4

XDP_BPM#5

XDP_BPM#6

XDP_BPM#7

XDP_TCK

XDP_TRST#

XDP_TMS

XDP_TDI_R

XDP_PREQ#

BUFO_CPU_RST# BUF_CPU_RST#

SM_RCOMP1

SM_RCOMP2

SM_RCOMP0

XDP_TDO_R

XDP_DBRESET#_R1

CLK_CPU_DPLL#_R

SYS_PWROK_XDP

H_CPUPWRGD_R

VDDPWRGOOD

CLK_CPU_DMI_R

CLK_CPU_DMI#_R

H_CATERR#

H_PECI

D_PWG

VDDPWRGOOD

S_PWG

CLK_CPU_DPLL_R

H_PROCHOT#

+VCCP_XDP

XDP_TCK

XDP_TMS

XDP_TDI

XDP_TDO

XDP_DBRESET#

XDP_TRST#

XDP_RST#_RPLT_RST#

CLK_CPU_ITP#

CLK_CPU_ITP

SYS_PWROK_XDP

XDP_HOOK2

CFD_PWRBTN#_XDP

H_CPUPWRGD H_CPUPWRGD_XDP

XDP_PREQ#

XDP_PRDY#

XDP_BPM#0

XDP_DBRESET#_R1

XDP_DBRESET#_R1

VDDPWRGOOD_R

H_DRAMRST#

H_PECI

H_CPUPWRGD_R

BUF_CPU_RST#

CLK_CPU_DPLL_R

CLK_CPU_DPLL#_R

H_CPUPWRGD_R

H_SNB_IVB#16

H_PM_SYNC14

H_THERMTRIP#16

H_CPUPWRGD16

H_PROCHOT#40,43

H_DRAMRST# 6

CLK_CPU_DMI# 13

CLK_CPU_DMI 13

PM_DRAM_PWRGD14

PLT_RST#15,32,36,40,41

H_PECI40

SYSTEM_PWROK14

XDP_DBRESET#_R 12,14

CLK_CPU_ITP#13

CLK_CPU_ITP13

VGATE14,51

CFG07

PBTN_OUT#14,40

+1.05VS

+1.05VS

+3VS

+1.05VS

+3VALW

+1.5V_CPU_VDDQ

+3VS

+3VALW

+3V_PCH

+3VS

+1.05VS

+1.05VS

+3V_PCH

+1.05VS

Title

Size Document Number Rev

Date: Sheet of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

LA-8224P

0.2

PROCESSOR(2/6) PM,XDP,CLK

Custom

5 59Thursday, October 27, 2011

2011/07/12 2012/12/31

Title

Size Document Number Rev

Date: Sheet of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

LA-8224P

0.2

PROCESSOR(2/6) PM,XDP,CLK

Custom

5 59Thursday, October 27, 2011

2011/07/12 2012/12/31

Title

Size Document Number Rev

Date: Sheet of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

LA-8224P

0.2

PROCESSOR(2/6) PM,XDP,CLK

Custom

5 59Thursday, October 27, 2011

2011/07/12 2012/12/31

Place near JXDP1

PU/PD for JTAG signals

DDR3 Compensation Signals

Compal Electronics, Inc.

Processor Pullups

Reserve for EMI please close to JCPU1

Reserve for EMI please close to JCPU1

Reserve for EMI please close to JCPU1

Reserve for EMI please close to JCPU1

Reserve for EMI please close to JCPU1

Reserve for EMI please close to JCPU1

ER17

ER20

ER20

ER20

R34140_0402_1% R34140_0402_1%

1 2

C421 100P_0402_50V8J

@

C421 100P_0402_50V8J

@

1 2

U1

74AHC1G09GW TSSOP 5P

U1

74AHC1G09GW TSSOP 5P

A

1

B

2

G

3

O

4

P

5

R267

0_0402_5%

@

R267

0_0402_5%

@

1 2

C68 100P_0402_50V8J

@

C68 100P_0402_50V8J

@

1 2

T9 PAD@ T9 PAD@

R2851_0402_5% @ R2851_0402_5% @

1 2

C72 100P_0402_50V8J

@

C72 100P_0402_50V8J

@

1 2

C66

0.1U_0402_16V4Z~D

XDP@

C66

0.1U_0402_16V4Z~D

XDP@

1

2

R3351_0402_5% R3351_0402_5%

1 2

C71 100P_0402_50V8J

@

C71 100P_0402_50V8J

@

1 2

R15

75_0402_5%

R15

75_0402_5%

12

R35 0_0402_5% XDP@R35 0_0402_5% XDP@

1 2

T3 PAD@ T3 PAD@

T4 PAD@ T4 PAD@

R3251_0402_5% R3251_0402_5%

1 2

R2651_0402_5% R2651_0402_5%

1 2

R19 0_0402_5%R19 0_0402_5%

1 2

R23

56_0402_5%

R23

56_0402_5%

1 2

JXDP1

ACES_87152-26051

CONN@

JXDP1

ACES_87152-26051

CONN@

1

1

2

2

3

3

4

4

5

5

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

G1

27

G2

28

R20

0_0402_5%

@

R20

0_0402_5%

@

12

R2510K_0402_5% R2510K_0402_5%

1 2

C65

0.1U_0402_16V4Z~D

C65

0.1U_0402_16V4Z~D

1

2

R9

0_0402_5%@

R9

0_0402_5%@

1 2

R1662_0402_5% R1662_0402_5%

1 2

R684

0_0402_5%

R684

0_0402_5%

1 2

R37 0_0402_5%R37 0_0402_5%

1 2

C69

0.1U_0402_16V4Z

C69

0.1U_0402_16V4Z

1

2

T5 PAD@ T5 PAD@

R31 0_0402_5% XDP@R31 0_0402_5% XDP@

1 2

R17

43_0402_1%

R17

43_0402_1%

1 2

C426 100P_0402_50V8J

@

C426 100P_0402_50V8J

@

1 2

R30 0_0402_5% XDP@R30 0_0402_5% XDP@

1 2

R14

200_0402_1%

R14

200_0402_1%

1 2

T7 PAD@ T7 PAD@

R3

10K_0402_5%

R3

10K_0402_5%

12

R18 0_0402_5%R18 0_0402_5%

1 2

T8 PAD@ T8 PAD@

T1

PAD

@

T1

PAD

@

R3825.5_0402_1% R3825.5_0402_1%

1 2

R71K_0402_5% XDP@ R71K_0402_5% XDP@

1 2

T2 PAD@ T2 PAD@

C70 100P_0402_50V8J

@

C70 100P_0402_50V8J

@

1 2

CLOCKS

MISCTHERMALPWR MANAGEMENT

DDR3

MISC

JTAG & BPM

JCPU1B

TYCO_2013620-2_IVY BRIDGE

CONN@

CLOCKS

MISCTHERMALPWR MANAGEMENT

DDR3

MISC

JTAG & BPM

JCPU1B

TYCO_2013620-2_IVY BRIDGE

CONN@

SM_RCOMP[1]

A5

SM_RCOMP[2]

A4

SM_DRAMRST#

R8

SM_RCOMP[0]

AK1

BCLK#

A27

BCLK

A28

DPLL_REF_CLK#

A15

DPLL_REF_CLK

A16

CATERR#

AL33

PECI

AN33

PROCHOT#

AL32

THERMTRIP#

AN32

SM_DRAMPWROK

V8

RESET#

AR33

PRDY#

AP29

PREQ#

AP27

TCK

AR26

TMS

AR27

TRST#

AP30

TDI

AR28

TDO

AP26

DBR#

AL35

BPM#[0]

AT28

BPM#[1]

AR29

BPM#[2]

AR30

BPM#[3]

AT30

BPM#[4]

AP32

BPM#[5]

AR31

BPM#[6]

AT31

BPM#[7]

AR32

PM_SYNC

AM34

SKTOCC#

AN34

PROC_SELECT#

C26

UNCOREPWRGOOD

AP33

R21

1K_0402_1%

R21

1K_0402_1%

1 2

R120_0402_5% XDP@ R120_0402_5% XDP@

1 2

R100_0402_5% XDP@ R100_0402_5% XDP@

1 2

R2951_0402_5% R2951_0402_5%

1 2

T6 PAD@ T6 PAD@

U2

SN74LVC1G07DCKR_SC70-5

U2

SN74LVC1G07DCKR_SC70-5

A

2

Y

4

1

NC

G

3

P

5

R2751_0402_5% R2751_0402_5%

1 2

R36

130_0402_1%

R36

130_0402_1%

1 2

R8

1K_0402_5%

@

R8

1K_0402_5%

@

12

R60_0402_5% XDP@ R60_0402_5% XDP@

1 2

R4

200_0402_1%

R4

200_0402_1%

12

R11 0_0402_5%R11 0_0402_5%

1 2

R51K_0402_5%

XDP@

R51K_0402_5%

XDP@

1 2

C67

0.1U_0402_16V4Z~D

XDP@

C67

0.1U_0402_16V4Z~D

XDP@

1

2

R241K_0402_5% R241K_0402_5%

1 2

R22

1K_0402_1%

R22

1K_0402_1%

1 2

R13

1K_0402_5%

XDP@ R13

1K_0402_5%

XDP@

1 2

R39200_0402_1% R39200_0402_1%

1 2

R576

0_0402_5%

R576

0_0402_5%

1 2