没有合适的资源?快使用搜索试试~ 我知道了~

存储器设计存储器设计.doc

1.该资源内容由用户上传,如若侵权请联系客服进行举报

2.虚拟产品一经售出概不退款(资源遇到问题,请及时私信上传者)

2.虚拟产品一经售出概不退款(资源遇到问题,请及时私信上传者)

版权申诉

0 下载量 25 浏览量

2022-07-06

04:23:41

上传

评论

收藏 1.27MB DOC 举报

温馨提示

试读

22页

存储器设计存储器设计

资源推荐

资源详情

资源评论

课 程 设 计 报 告

课程设计名称:计算机组成原理课程设计

课程设计题目:存储器设计

院(系):

专 业:

班 级:

学 号:

姓 名:

指导教师:

完成日期:

-I-

目 录

第 1 章 总体设计方案 ...................................................................................................1

1.1 设计原理 .................................................................................................................1

1.2 设计思路 .................................................................................................................1

1.3 设计环境..................................................................................................................2

第 2 章 详细设计方案 ...................................................................................................5

2.1 顶层方案图的设计与实现 ...................................................................................5

2.1.1 创建顶层图形设计文件 ...................................................................................5

2.1.2 器件的选择与引脚锁定 ...................................................................................5

2.1.3 编译、综合、适配 ...........................................................................................6

2.2 功能模块的设计与实现 .......................................................................................6

2.2.1 RAM256*1 存储器模块的设计与实现...........................................................7

2.2.2 RAM1K*1 存储器模块的设计与实现 ............................................................8

2.2.3 RAM1K*4 存储器模块的设计与实现 ..........................................................10

2.2.4 RAM4K*4 存储器模块的设计与实现 ..........................................................11

2.3 仿真调试 .............................................................................................................13

第 3 章 编程下载与硬件测试.....................................................................................15

3.1 编程下载 .............................................................................................................15

3.2 硬件测试及结果分析 .........................................................................................15

参考文献 .........................................................................................................................18

附录(电路原理图) .....................................................................................................19

-1-

第 1 章 总体设计方案

1.1 设计原理

当一片 RAM(或 ROM)不能满足存储容量位数(或字数)要求时,需要多片存储

芯片进行扩展,形成一个容量更大、字数位数更多的存储器。扩展方法根据需要

有位扩展、字扩展和字位同时扩展 3 种。

(1)位扩展

若一个存储器的字数用一片集成芯片已经够用,而位数不够用,则用“位扩

展”方式将多片该型号集成芯片连接成满足要求的存储器。扩展的方法是将多片

同型号的存储器芯片的地址线、读/写控制线(

WR

)和时钟信号相应连在一起,而

将其数据线分别引出接到存储器的数据总线上。

(2)字扩展

若每一片存储器的数据位数够而字线数不够时,则需要采用“字线扩展”的

方式将多片该种集成芯片连接成满足要求的存储器。扩展的方法是将各个芯片的

数据线、地址线和读写(

WR

)控制线分别接在一起,用译码器和时钟信号选择集

成芯片。

(3)字、位同时扩展

在很多情况下,要组成的存储器比现有的存储芯片的字数、位数都多,需要字

位同时进行扩展。扩展时可以先计算出所需芯片的总数及片内地址线、数据线的

条数,再用前面介绍的方法进行扩展,先进行位扩展,再进行字扩展。

1.2 设计思路

用 1K×4 位的 RAM 集成芯片若干片,构成一个 8k×8 位的 RAM

需要 RAM 的片数=(8k×8 位)/(1k×4 位)=16(片)

因为 1K×4 位的 RAM 容量 1024×8 位,表明片内字数 1024=2

10

,所以地址

线有 10 条,即(A

0

~A

19

),每字 4 位,数据线有 4 条(D

0

~D

3

)。

而存储容量为 8K×8 位的 RAM,即字数 8K=2

13

,所以地址线有 13 条,即

-2-

(A

0

~A

12

),每字 8 位,数据线有 8 条(D

0

~D

7

)。存储器的底层、顶层的设计都采用

原理图设计输入方式,经编译、调试后形成*.bit 文件并下载到 XCV200 可编程逻

辑芯片中,经硬件测试验证设计的正确性。存储器的设计框图如图 1.1 所示。

图 1.1 存储器的设计框图

1.3 设计环境

(1)硬件环境

•伟福 COP2000 型计算机组成原理实验仪

COP2000 计算机组成原理实验系统由实验平台、开关电源、软件三大部分组

成实验平台上有寄存器组 R0-R3、运算单元、累加器 A、暂存器 B、直通/左移/右

移单元、地址寄存器、程序计数器、堆栈、中断源、输入/输出单元、存储器单元、

微地址寄存器、指令寄存器、微程序控制器、组合逻辑控制器、扩展座、总线插

孔区、微动开关/指示灯、逻辑笔、脉冲源、20 个按键、字符式 LCD、RS232 口。

COP2000 计算机组成原理实验系统各单元部件都以计算机结构模型布局,清

晰明了,系统在实验时即使不借助 PC 机,也可实时监控数据流状态及正确与否,

实验系统的软硬件对用户的实验设计具有完全的开放特性,系统提供了微程序控

制器和组合逻辑控制器两种控制器方式, 系统还支持手动方式、联机方式、模拟

方式三种工作方式,系统具备完善的寻址方式、指令系统和强大的模拟调试功能。

(2)EDA 环境

•Xilinx foundation f3.1 设计软件

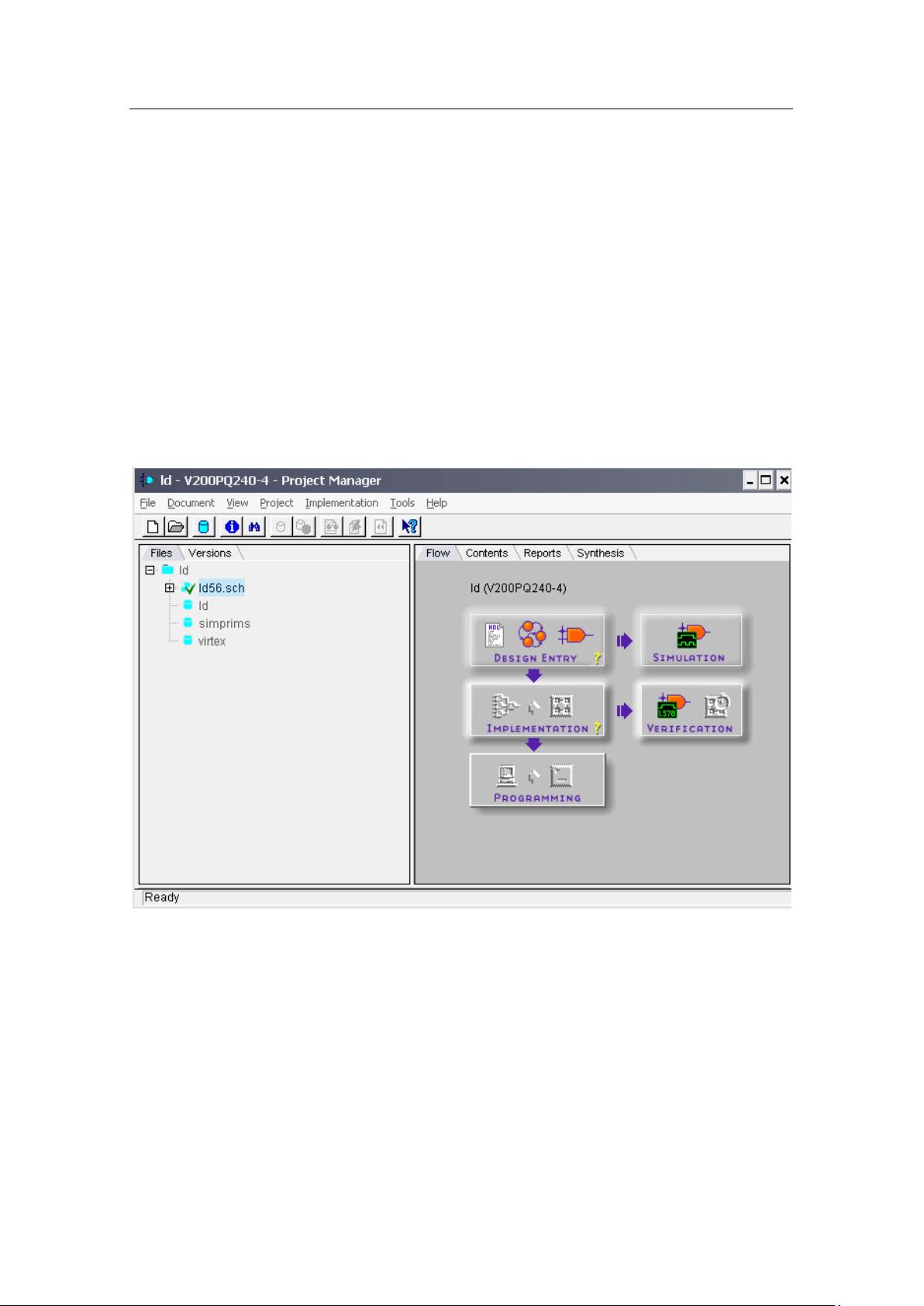

Xilinx foundation f3.1 是 Xilinx 公司的可编程期间开发工具,该平台(如图 1.2

8K×8 位的 RAM 存储器

4K×4 位的 RAM 存储器

1K×4 位的 RAM 存储器

1K×1 位的 RAM 存储器

256×1 位的 RAM 存储器

-3-

所示)功能强大,主要用于百万逻辑门设计。该系统由设计入口工具、设计实现

工具、设计验证工具三大部分组成。

设计入口工具包括原理图编辑器、有限状态机编辑器、硬件描述语言(HDL)

编辑器、LogiBLOX 模块生成器、Xilinx 内核生成器等软件。其功能是:接收各种

图形或文字的设计输入,并最终生成网络表文件。设计实现工具包括流程引擎、

限制编辑器、基片规划器、FPGA 编辑器、FPGA 写入器等软件。设计实现工具用

于将网络表转化为配置比特流,并下载到器件。设计验证工具包括功能和时序仿

真器、静态时序分析器等,可用来对设计中的逻辑关系及输出结果进行检验,并

详尽分析各个时序限制的满足情况。

图 1.2 Xilinx foundation f3.1 设计平台

•COP2000 集成调试软件

COP2000 集成开发环境是为 COP2000 实验仪与 PC 机相连进行高层次实验

的配套软件,它通过实验仪的串行接口和 PC 机的串行接口相连,提供汇编、反

汇编、编辑、修改指令、文件传送、调试 FPGA 实验等功能,该软件在 Windows

下运行。COP2000 集成开发环境界面如图 1.3 所示。

剩余21页未读,继续阅读

资源评论

omyligaga

- 粉丝: 54

- 资源: 2万+

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功