VerilogHDL简明教程_清华大学

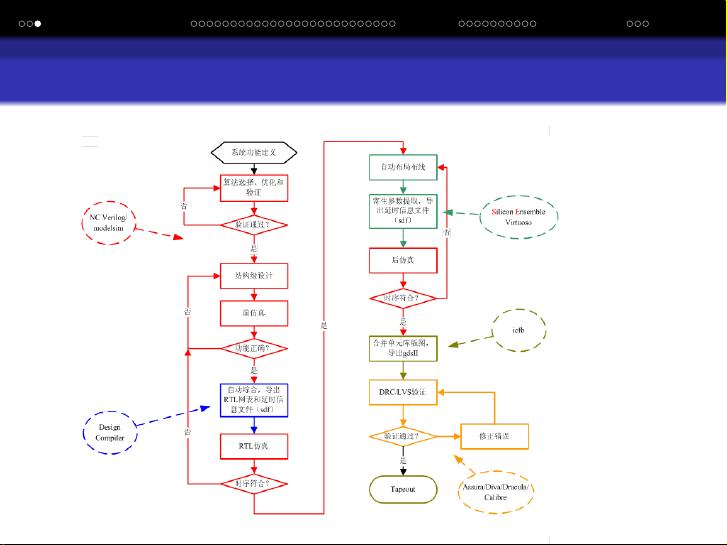

### Verilog HDL简明教程 #### Verilog HDL简介 **Verilog HDL**是一种广泛应用于数字系统设计中的硬件描述语言(Hardware Description Language),它采用类似于C语言的语法结构,能够支持从算法级、结构级、寄存器传输级(RTL)、门级到开关级等不同抽象级别的设计。通过层次化的数字系统建模方式,设计师可以轻松地对系统进行分层设计,从而更好地管理复杂度。此外,Verilog HDL还具有设计与工艺无关的特点,这意味着设计者可以利用多种综合工具将设计从RTL级转换为门级网表。 **历史发展:** - **1983年**,由Gateway Design Automation公司首次开发,主要用于其模拟器产品。 - **1989年**,Cadence Design Systems公司收购了Gateway Design Automation。 - **1990年**,Verilog HDL语言被开放给公众使用,并成立了Open Verilog International (OVI)组织。 - **1995年**,Verilog HDL成为IEEE标准(IEEE Std 1364-1995)。 - **2001年**,进行了重大修订,成为IEEE Std 1364-2001。 - **2002年**,定义了可综合子集(IEEE Std 1364.1-2002)。 #### Verilog HDL结构、语法与电路设计 **基本结构:** Verilog HDL的基本单位是**模块**,每个模块定义了一个特定的功能单元。模块内包含输入端口、输出端口、内部信号以及具体的逻辑操作。模块之间可以通过端口连接实现层次化的系统构建。 **电路设计:** - **组合逻辑**:组合逻辑的设计主要依靠连续性赋值语句(assign)或阻塞型过程赋值语句(always/initial)。例如,对于一个简单的二选一多路选择器,可以使用`assign`语句实现: ```verilog assign out = sel ? a : b; ``` - **时序逻辑**:时序逻辑通常涉及到时钟信号和存储单元,需要使用非阻塞型过程赋值语句(always/initial)。例如,在一个简单的时序逻辑电路中,可以定义如下: ```verilog always @(posedge clk) begin if (sel) out <= a; else out <= b; end ``` **层次建模:** Verilog HDL支持自顶向下(top-down)和自底向上(bottom-up)的设计方法。通过将复杂系统分解成多个小的模块,可以在不同的抽象级别上进行设计和优化。例如,可以定义一个顶层模块,并在其中实例化多个子模块: ```verilog module Top (Port); Module01 u01 (Port); endmodule ``` **测试与验证:** 为了确保设计的正确性,Verilog HDL支持在设计阶段就进行仿真和验证。这通常通过编写测试平台来实现,测试平台会向设计提供一系列测试激励,并观察输出响应是否符合预期。 **综合:** 综合是指将高层次的抽象设计转换为低层次的门级网表的过程。Verilog HDL提供了丰富的语法规则和支持工具,使得设计师能够方便地进行综合操作。 **有限状态机:** 有限状态机(Finite State Machine, FSM)是一种常用的设计模式,特别适用于时序逻辑的设计。通过定义不同的状态和转移条件,FSM可以实现复杂的控制逻辑。 #### 除法器设计实例 在本部分,我们将会详细介绍如何使用Verilog HDL设计一个除法器。设计过程主要包括确定设计目标、选择算法、实现RTL代码并进行验证。 **设计目标:** - 实现一个能处理特定位宽数据的除法器。 - 支持无符号和有符号的整数运算。 - 能够在有限的时间内完成计算。 **算法与结构:** 除法器的设计通常基于二进制除法算法。根据设计的具体需求,可以选择迭代算法或者并行算法。迭代算法虽然实现简单,但计算速度较慢;而并行算法虽然速度快,但硬件资源消耗较大。 **RTL实现与验证:** - 使用Verilog HDL编写除法器的RTL代码。 - 设计测试平台,编写测试激励。 - 验证除法器的正确性,确保在各种边界条件下都能得到正确的结果。 #### 工具及参考资源 **仿真和综合工具:** 常用的Verilog HDL仿真工具有ModelSim、NC-Verilog等,综合工具如Synopsys Design Compiler、Xilinx ISE等。这些工具可以帮助设计者快速地完成设计、仿真和综合工作。 **参考资源:** - Verilog HDL官方文档 - IEEE Std 1364-2001 - 各种在线论坛和社区 - 专业书籍,如《Digital Design and Computer Architecture》 通过上述内容的学习和实践,设计者不仅能够掌握Verilog HDL的基本语法和结构,还能学会如何使用该语言来实现复杂的数字系统设计任务。

剩余42页未读,继续阅读

- 粉丝: 422

- 资源: 4

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 个人实习的终极无敌面经

- 新年主题下的计算机资源利用与探索

- lianjia2.csv

- 2022年江苏省职业院校技能大赛中职网络搭建与应用赛项公开赛卷技能要求

- 毕设和企业适用springboot企业资源规划类及健康管理监控平台源码+论文+视频.zip

- 小功率调幅发射机设计报告(含各级电路的计算与调试)

- 基于 SSM + Shiro + Dubbo 的 RESTful Web 应用快速启动器资料齐全+详细文档.zip

- 基于 dubbo 实现的分布式电商平台资料齐全+详细文档.zip

- 基于 spring、dubbo 的分布式服务架构资料齐全+详细文档.zip

- 基于dubbo redis分布式定时回调服务资料齐全+详细文档.zip

- 基于atomikos的分布式事务管理资料齐全+详细文档.zip

- 基于Dubbo 2.6.6版本源码注释资料齐全+详细文档.zip

- 基于dubbo+sqlhint来实现的特殊数据库操作(比如:SQL语句路由)资料齐全+详细文档.zip

- 基于dubbo+zookeeper将”优雅的SSM框架“拆分为分布式架构资料齐全+详细文档.zip

- 基于dubbo、spring扩展实现的接入层灰度、服务层灰度、mq灰度、外部调用灰度,支持多套灰度环境(灰度系统)资料齐全+详细文档.zip

- 基于dubbo2.6.4的Dubbo TraceId的设置获取传递工具包资料齐全+详细文档.zip

信息提交成功

信息提交成功