SRAM 使用的是 ISSI 的 61LV5128,8 位宽,19 条地址线。FPGA 内部有一个地址

产生计数单元,因此数据读操作时输出管脚的时序起点就是这些地址产生单元。

因为希望快速读 SRAM,所以状态机代码读 SRAM 是第一个时钟周期送地址

(SRAM 的 OE#信号始终接地),第二个时钟周期读数据。系统时钟使用的是

50MHz(20ns),SRAM 的标称读写速度可以达到 8ns。感觉上 20ns 操作一个 8ns

的 SRAM 似乎很可行。

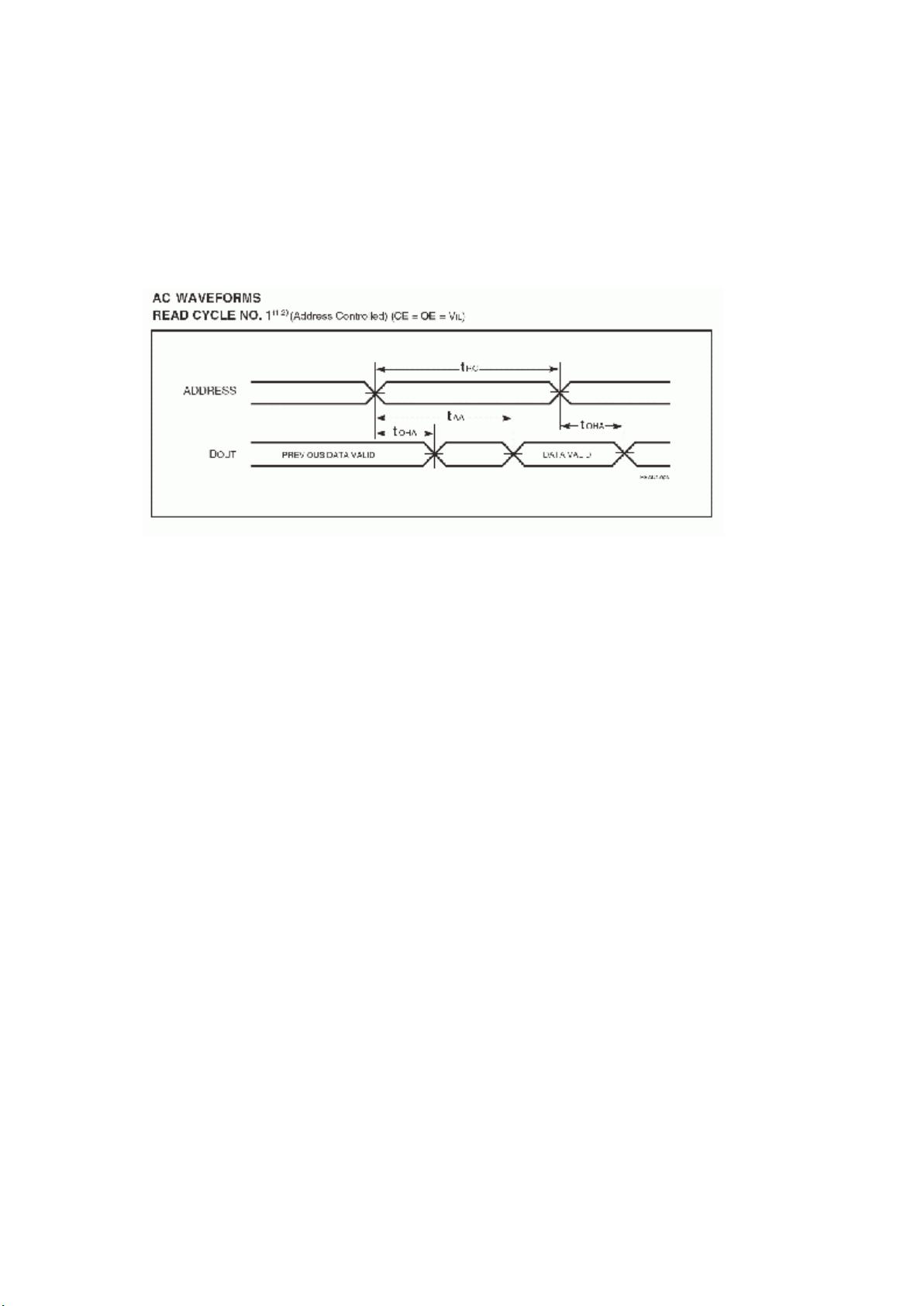

上面 SRAM 的读时序中,tRC=8ns,也就是说地址稳定后最多等待 8ns 数据总线

上的数据是有效的(上面的说明只是相对于 SRAM 管脚而言,不考虑其它条件)。

那么在地址稳定后的 0—8ns 之间的数据可能是有效的也可能是无效的我们无从

得知(也许不到 8ns 数据就已经有效了,可以说 8ns 是一个很保守的读取时间),

但是 8ns 以后一直到数据地址发生变化的 tOHA 时间内的数据一定是稳定的。

上面罗嗦了一大堆,下面步入正题。我们要计算 FPGA 和 SRAM 的数据总线

接口上的 input delay 值,按照公式:Input max/min delay = 外部器件的 max/min

Tco + 数据的 PCB 延时 – PCB 时钟偏斜。

我们先计算一下地址总线最终稳定在 SRAM 输入管脚的时间,应该是 FPGA

内部时钟的 launch edge 开始到 FPGA 输出管脚的延时加上地址总线在 PCB 上从

FPGA 管脚到 SRAM 管脚的延时。前者的值为 5.546ns—9.315ns(由 FPGA 时序分

析得到,不包括 launch edge 的 clock network delay),后者的值为 0.081ns—

0.270ns(由 PCB 走线长度换算得到)。那么地址总线最终稳定在 SRAM 输入管

脚的时间 max=9.585ns,min=5.627ns。

其次,我们可以从 SRAM 的 datasheet 查到(也就是上面的时序图的 tRC)

地址稳定后 Tco=8ns 数据稳定在 SRAM 数据总线的输出管脚上。数据总线从 SRAM

管脚到达 FPGA 输入管脚的 PCB 延时为 0.085ns—0.220ns。

从上面的一堆数据里,我们需要理出一条思路。首先需要对这个时序进行

建模,和 FPGA 内部的寄存器到寄存器的路径和类似,这个时序模型也是从 FPGA

内部寄存器(输出管脚)到 FPGA 内部寄存器(输入管脚),不同的是这个寄存

器到寄存器间的路径不仅在 FPGA 内部,而是先从寄存器的输出端到 FPGA 的输

出管脚,再从 PCB 走线到外部器件 SRAM 的输入管脚,然后经过了 SRAM 内部的

Tco 时间后,又从 SRAM 的输出管脚经 PCB 走线达到 FPGA 的输入管脚,这个输

入管脚还需要有一些逻辑走线后才达到 FPGA 内部寄存器的输入端。整个模型就

是这样,下面看这个输入管脚的 Input delay 如何取值。大体的这个路径如下图,