2. 在实际应用中若用 74LS20 来实现 Y= AB 时,多余的输入端应接高电平还是低电平?

3. 在全加器电路中,当 A =0,S *=1,C =1 时 C =?

1. 通过实验你觉得用小规模集成电路和中规模集成电路来设计组合逻辑电路哪个更方

2. 能否以一片 74LS151 为核心来设计全加器?

答:不能以一片 74LS151 为核心来设计全加器。

3. 以 74LS138 和门电路来设计全减器,选用 TTL 或 CMOS 门电路那种更合适?

答:选用 TTL 门电路。

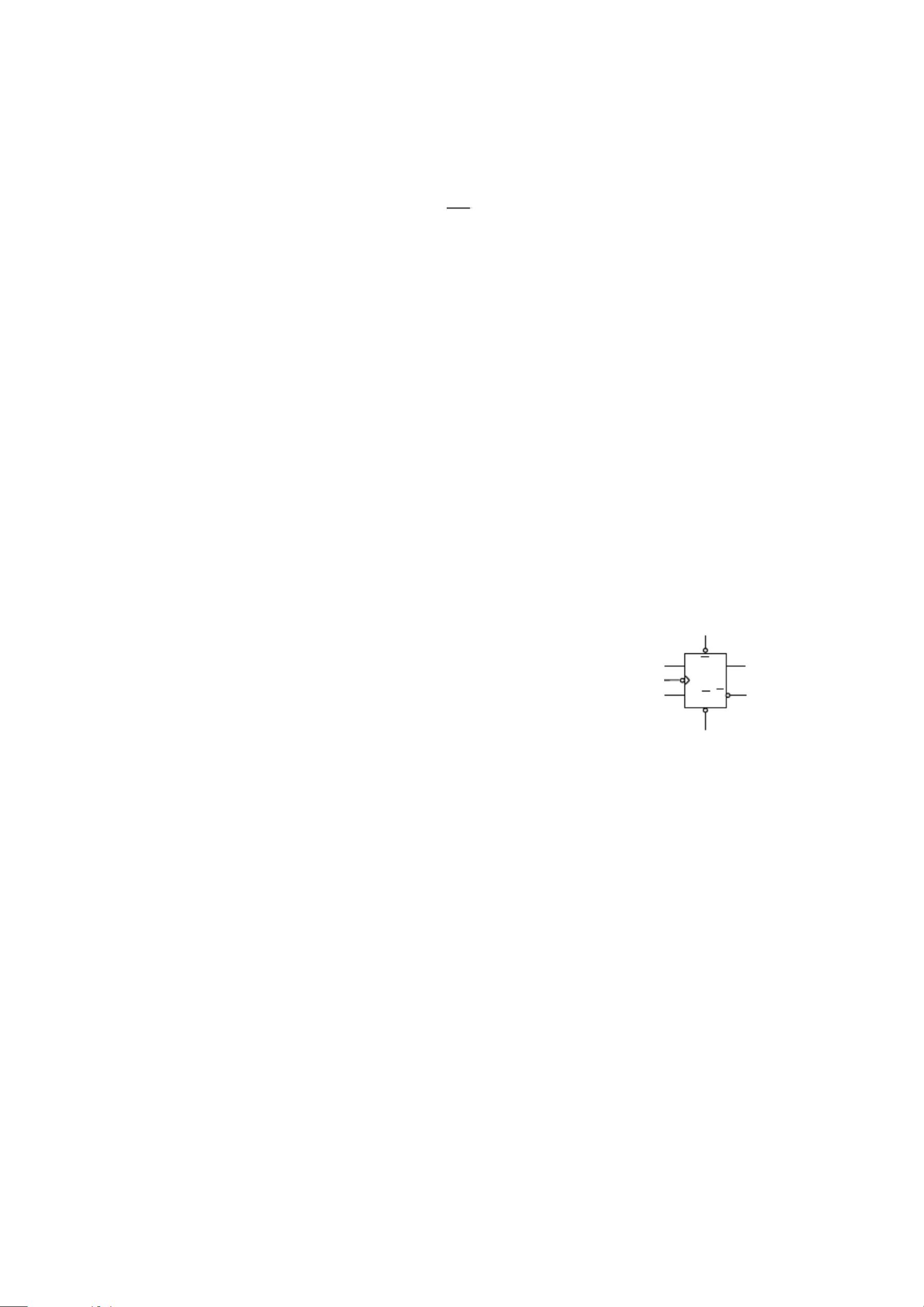

1.在图 3-1 中经过一个 CP 脉冲后,JK 触发器为何种状态?

2.用 74LS76 的 JK 触发器转换成的 D 触发器与 74LS74 的

D 触发器在工作中有什么不同之处?

答:前者在时钟脉冲后沿触发翻转,后者在时钟脉冲前沿触发翻转。

3.移位寄存器如果采用串行输出方式应从哪里输出?需送几个脉冲才能把“1101”取出?

答:移位寄存器如果采用串行输出方式应从Q 输出。需送八个脉冲才能把“1101” 取出。

1.将图 4-1 作什么样的改变,即可构成四位异步二进制减法计数器?

答: 将低位触发器的输出端 Q 接到高位触发器的时钟输入端即可。

2.图 4-2 中由 JK 触发器构成的计数器是几进制计数器?

3.以 74LS74 为核心构成九进制计数器,至少要用几片74LS74?

答:至少要用两片 74LS74 集成片。

评论0

最新资源