xilinx PCIE2.0接口 EP端设计总结.pdf

2.虚拟产品一经售出概不退款(资源遇到问题,请及时私信上传者)

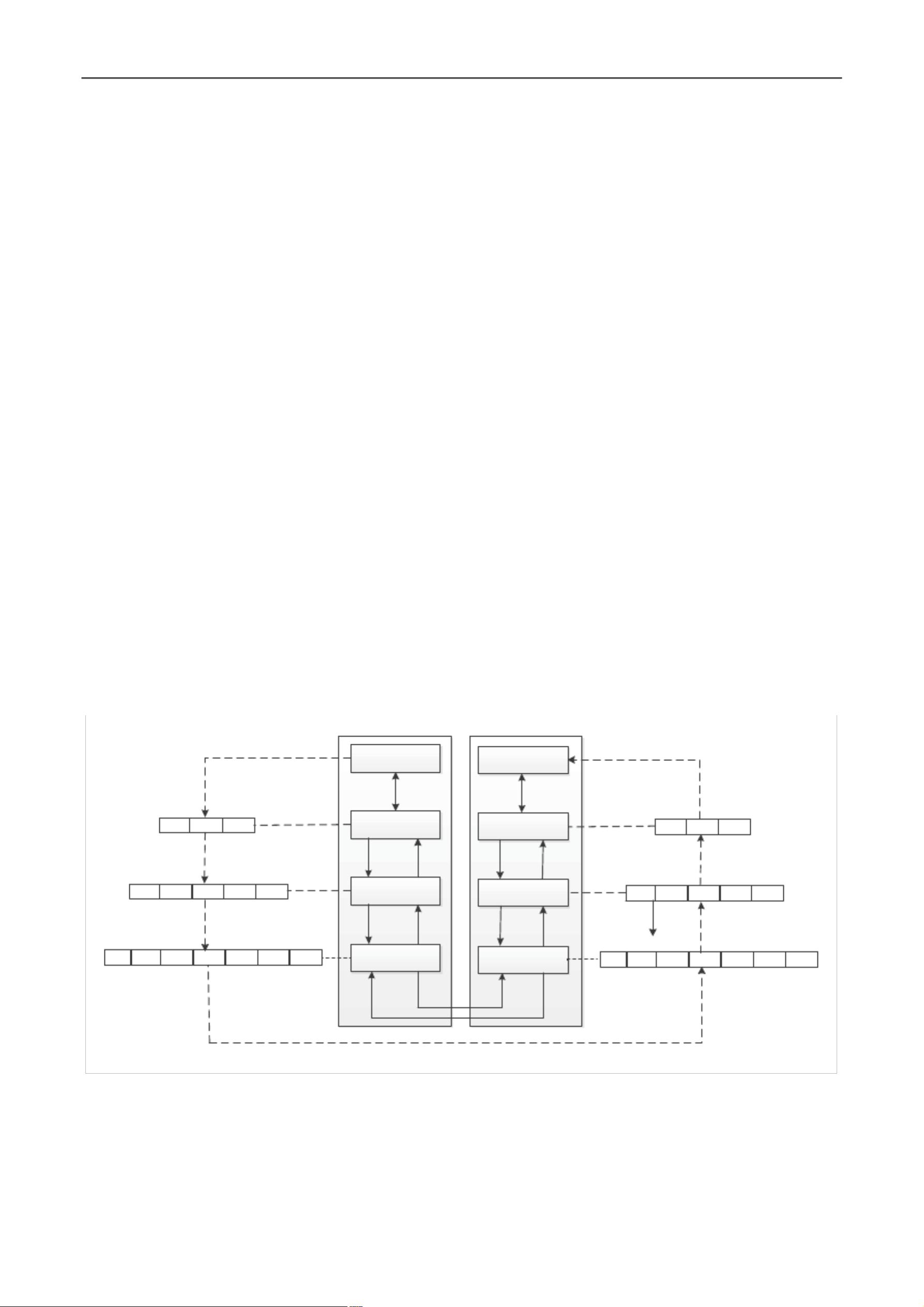

【PCI Express(PCIe)简介】 PCI Express(PCIe)是一种高速接口标准,用于计算机系统中的内部设备连接,如显卡、网卡、硬盘等。它由PCI-SIG(Peripheral Component Interconnect Special Interest Group)组织定义,旨在替代传统的PCI和PCI-X总线,提供更高的数据传输速率和更低的延迟。 在PCIe架构中,主要有以下组件: 1. 根复合体(Root Complex):作为系统的核心,连接CPU和主内存,发起PCIe事务并访问主存储器。 2. 交换器(Switch):用于多设备间的通信,通过ID路由、地址路由或隐含路由来分配数据。 3. 端点(Endpoint):实际的设备,作为数据请求者或完成者。 4. 端口(Port):设备与PCIe链路之间的接口。 5. 桥(Bridge):用于PCIe设备与PCI/PCI-X设备间的通信,实现协议转换。 【PCIe协议层次结构】 PCIe协议分为三个主要层次: 1. 事务层(Transaction Layer):位于协议的最上层,负责生成和解析事务层包(TLP)。TLP包含应用层信息,如读/写请求、配置信息等,通过事务层发送给数据链路层,并处理来自该层的响应。 2. 数据链路层(Data Link Layer):处理TLP的错误检测和纠正,以及流量控制。数据链路层包(DLLP)在此层生成,附加了CRC校验等信息。 3. 物理层(Physical Layer):负责TLP的编码、解码,以及通过物理介质(如铜线或光纤)的实际传输。 在FPGA中实现PCIe功能,主要关注事务层包的处理。数据的移动由CPU发起,例如,当CPU通过存储器映射的输入/输出(MMIO)地址执行命令时,数据会沿着PCIe链路向下流动。根复合体生成存储器写TLP,而端点接收并更新本地寄存器。反之,当CPU读取MMIO地址的寄存器时,数据向上游回传,端点生成包含数据的完成型TLP,发送给根复合体。 【PCIe核接口】 PCIe核的接口主要包括系统接口和PCIe接口两部分: 1. 系统接口:包括异步复位信号`Sys_rst_n`和系统时钟`Sys_clk`。`Sys_rst_n`在上电和热复位期间需保持低电平至少1500ns,`Sys_clk`则为可选的100MHz、125MHz或500MHz时钟。 2. PCIe接口:由多个发送(TX)和接收(RX)差分对组成,每个差分对包括一个正信号和一个负信号。例如,对于4线PCIe核心,会有4对TX和RX信号。这些信号是串行差分的,用于在链路上传输数据。 总结来说,PCIe 2.0接口在EP(Endpoint)端的设计涵盖了协议的理解、信号的处理以及在FPGA中实现的细节,涉及CPU与设备之间的数据传输、协议层的交互以及物理层的电气特性。理解这些概念对于构建高效、可靠的PCIe系统至关重要。

剩余46页未读,继续阅读

weixin_387162052023-03-11终于找到了超赞的宝藏资源,果断冲冲冲,支持!

weixin_387162052023-03-11终于找到了超赞的宝藏资源,果断冲冲冲,支持! 顾印钞2023-09-15资源简直太好了,完美解决了当下遇到的难题,这样的资源很难不支持~

顾印钞2023-09-15资源简直太好了,完美解决了当下遇到的难题,这样的资源很难不支持~ lzgjxh2023-11-21资源有很好的参考价值,总算找到了自己需要的资源啦。

lzgjxh2023-11-21资源有很好的参考价值,总算找到了自己需要的资源啦。 2301_769757912023-08-22非常有用的资源,有一定的参考价值,受益匪浅,值得下载。

2301_769757912023-08-22非常有用的资源,有一定的参考价值,受益匪浅,值得下载。

- 粉丝: 8582

- 资源: 2万+

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- DeepSeek自学手册:从理论到实践.pdf

- DeepSeek中小学生使用手册.pdf

- 把握DeepSeek时刻,携手同行 华为昇腾AI解决方案汇报.pdf

- 如何用DeepSeek打造抖音内容营销铁三角.pdf

- 计算机行业:DeepSeek+DeepResearch应用.pdf

- 快速配置各种程序支持环境

- 《3D打印基础实务》毕业设计之3D打印成型原理写字字帖.ppt

- ai大模型应用案例.pdf

- 《SQLServer数据库应用基础教程》第五章SQLServer的数据完整性.ppt

- deepseek使用教程-Deepseek 高效使用指南.pdf

- 电力电子硬件在仿真技术中运用.pdf

- 一文读懂Elasticsearch之单机模式搭建

- 计算机考证理论全.pdf

- 微控制器固件包_STM32CubeU5_开发工具_1741142576.zip

- 电路设计_Kicad-STM32_库_开发工具_1741144465.zip

- atihkoseoglu_STM32F4-DISCOVE_1741144102.zip

信息提交成功

信息提交成功