没有合适的资源?快使用搜索试试~ 我知道了~

西工大_数电实验_第二次实验_实验报告.pdf

1.该资源内容由用户上传,如若侵权请联系客服进行举报

2.虚拟产品一经售出概不退款(资源遇到问题,请及时私信上传者)

2.虚拟产品一经售出概不退款(资源遇到问题,请及时私信上传者)

版权申诉

0 下载量 183 浏览量

2022-07-09

06:23:07

上传

评论

收藏 1.24MB PDF 举报

温馨提示

试读

14页

西工大_数电实验_第二次实验_实验报告.pdf西工大_数电实验_第二次实验_实验报告.pdf西工大_数电实验_第二次实验_实验报告.pdf西工大_数电实验_第二次实验_实验报告.pdf西工大_数电实验_第二次实验_实验报告.pdf西工大_数电实验_第二次实验_实验报告.pdf西工大_数电实验_第二次实验_实验报告.pdf西工大_数电实验_第二次实验_实验报告.pdf西工大_数电实验_第二次实验_实验报告.pdf

资源推荐

资源详情

资源评论

;

数电实验 2

一.实验目的

1.学习并掌握硬件描述语言(VHDL 或 Verilog HDL);熟悉门电路的逻辑功能,

并用硬件描述语言实现门电路的设计。

2.熟悉中规模器件译码器的逻辑功能,用硬件描述语言实现其设计。

3.熟悉时序电路计数器的逻辑功能,用硬件描述语言实现其设计。

4.熟悉分频电路的逻辑功能,并用硬件描述语言实现其设计。

二.实验设备

1.Quartus 开发环境

2.ED0 开发板

三.实验内容

要求 1:编写一个异或门逻辑电路,编译程序如下。

1)用 QuartusII 波形仿真验证;

2)下载到 DE0 开发板验证。

要求 2:编写一个将二进制码转换成 0-F 的七段码译码器。

1)用 QuartusII 波形仿真验证;

2)下载到 DE0 开发板,利用开发板上的数码管验证。

要求 3: 编写一个计数器。

1)用 QuartusII 波形仿真验证;

2)下载到 DE0 开发板验证。

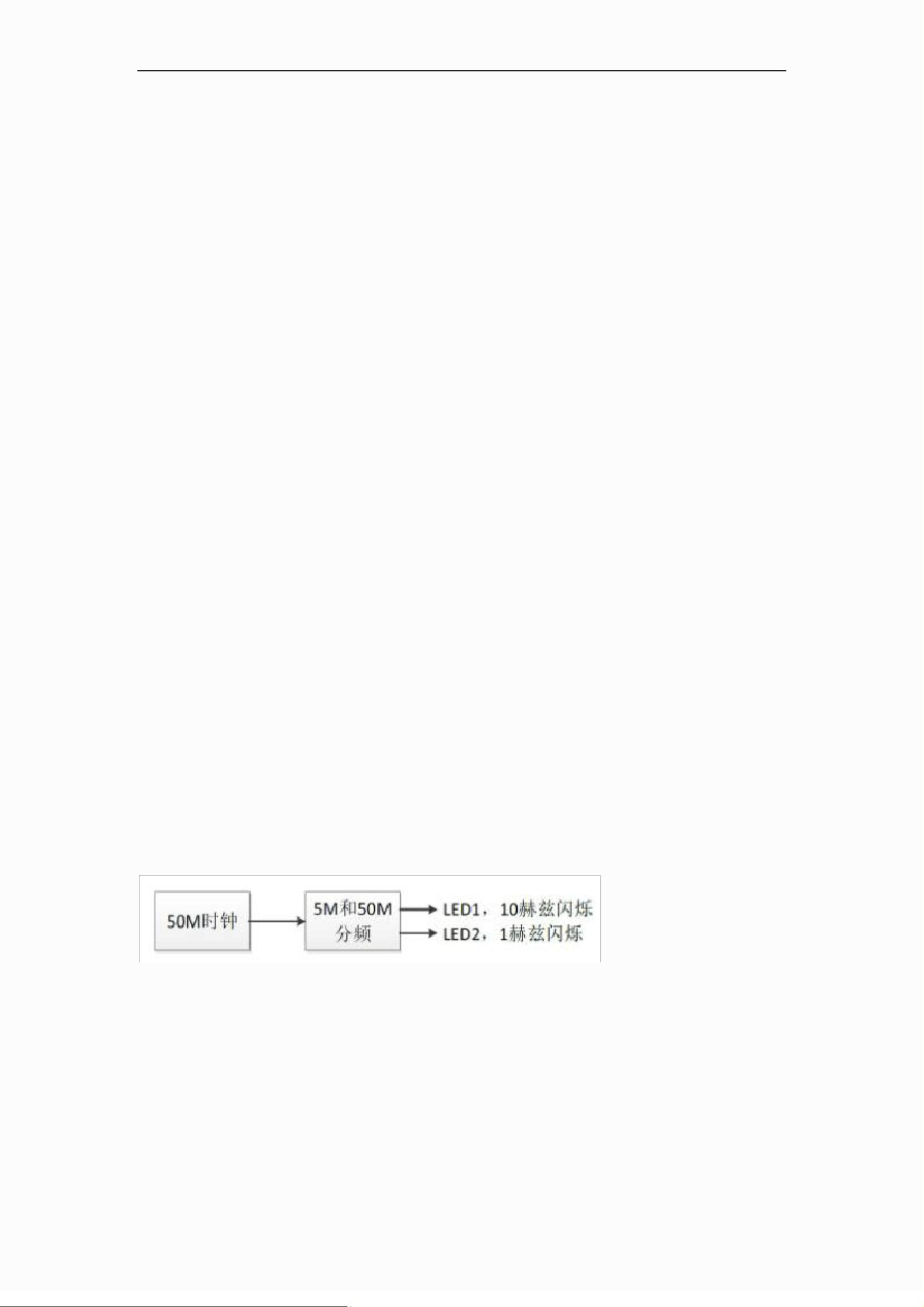

要求 4:编写一个能实现占空比 50%的 5M 和 50M 分频器即两个输出,输出信号

频率分别为 10Hz 和 1Hz。

1) 下载到 DE0 开发板验证。(提示:利用 DE0 板上已有的 50M 晶振作为输入

信号,通过开发板上两个的 LED 灯观察输出信号)。

2) 电路框图如下:

扩展内容:利用已经实现的 VHDL 模块文件,采用原理图方法,实现 0-F 计数

自动循环显示,频率 10Hz。(提示:如何将 VHDL 模块文件在逻辑原理图中应用,

参考参考内容 5)

四.实验原理

1.实验 1 实现异或门逻辑电路,VHDL 源代码如下:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

’.

;

ENTITY EXORGATE IS

PORT(A,B:IN STD_LOGIC;

C:OUT STD_LOGIC);

END EXORGATE;

ARCHITECTURE fwm OF EXORGATE IS

BEGIN

C<=A XOR B;

END;

2.实验 2 实现一个将二进制码转换成 0-F 的七段译码器,VHDL 源代码如下:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY sevendecoder IS

PORT (data_in:IN STD_LOGIC_VECTOR(3 DOWNTO 0);

dis_out:OUT STD_LOGIC_VECTOR(6 DOWNTO 0));

END sevendecoder;

ARCHITECTURE fwm OF sevendecoder IS

BEGIN

PROCESS(data_in)

BEGIN

CASE data_in IS

WHEN"0000"=>dis_out<="1000000";--显示 0

WHEN"0001"=>dis_out<="1111001";--显示 1

WHEN"0010"=>dis_out<="0100100";--显示 2

WHEN"0011"=>dis_out<="0110000";--显示 3

WHEN"0100"=>dis_out<="0011001";--显示 4

WHEN"0101"=>dis_out<="0010010";--显示 5

WHEN"0110"=>dis_out<="0000010";--显示 6

WHEN"0111"=>dis_out<="1111000";--显示 7

WHEN"1000"=>dis_out<="0000000";--显示 8

WHEN"1001"=>dis_out<="0010000";--显示 9

WHEN"1010"=>dis_out<="0001000";--显示 A

WHEN"1011"=>dis_out<="0000011";--显示 b

WHEN"1100"=>dis_out<="1000110";--显示 C

WHEN"1101"=>dis_out<="0100001";--显示 d

WHEN"1110"=>dis_out<="0000110";--显示 E

WHEN"1111"=>dis_out<="0001110";--显示 F

WHEN OTHERS=> dis_out<="1111111";--灭灯,不显示

END CASE;

END PROCESS;

END fwm;

3.实验 3 完成一个计数器,VHDL 源代码如下:

’.

;

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY counter IS

PORT ( clk,RST : IN STD_LOGIC;

DOUT : OUT STD_LOGIC_VECTOR (3 DOWNTO 0); --四位计数

COUT : OUT STD_LOGIC); --进位位

END counter;

ARCHITECTURE fwm OF counter IS

SIGNAL Q1 : STD_LOGIC_VECTOR (3 DOWNTO 0);

BEGIN

PROCESS(clk,RST)

BEGIN

IF RST = '0' THEN Q1<=(OTHERS => '0'); COUT<= '0';

ELSIF clk'EVENT AND clk='1' THEN

Q1<=Q1+1;

COUT<= '0';

IF Q1 >= "1001" THEN Q1<=(OTHERS => '0'); COUT<= '1';

END IF;

END IF;

END PROCESS;

DOUT<=Q1 ;

END fwm;

4.实验 4 编写一个能实现占空比 50%的 5M 和 50M 分频器即两个输出,输出信

号频率分别为 10Hz 和 1Hz,VHDL 源代码如下:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY fpq IS

PORT(clk:IN STD_LOGIC;

clk_out,clk_out1:OUT STD_LOGIC);

END fpq;

ARCHITECTURE fwm OF fpq IS

CONSTANT m : INTEGER:= 25000000; --50M 分频到 1Hz 时=25000000。

CONSTANT m1 : INTEGER:= 2500000; --5M 分频到 10Hz 时=2500000。

SIGNAL tmp :STD_LOGIC;

SIGNAL tmp1 :STD_LOGIC;

BEGIN

PROCESS(clk, tmp)

VARIABLE cout : INTEGER:=0;

BEGIN

IF clk'EVENT AND clk='1' THEN

cout:=cout+1; --计数器+1

IF cout<=m THEN tmp<='0'; --计数小于等于 25000000,输出 0

’.

剩余13页未读,继续阅读

资源评论

不吃鸳鸯锅

- 粉丝: 8253

- 资源: 2万+

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功