没有合适的资源?快使用搜索试试~ 我知道了~

毕业设计外文翻译--89C51单片机.docx

0 下载量 180 浏览量

2023-06-30

04:03:38

上传

评论

收藏 42KB DOCX 举报

温馨提示

试读

12页

毕业设计外文翻译--89C51单片机.docx

资源推荐

资源详情

资源评论

中北大学 2010 届毕业设计中英文翻译

1

The Description of AT89S51

1 General Description

The AT89S51 is a low-power, high-performance CMOS 8-bit microcontroller with

4K bytes of In-System Programmable Flash memory. The device is manufactured using

Atmel’s high-density nonvolatile memory technology and is compatible with the

industry-standard 80C51 instruction set and pinout. The on-chip Flash allows the

program memory to be reprogrammed in-system or by a conventional nonvolatile

memory programmer. By combining a versatile 8-bit CPU with In-System

Programmable Flash on a monolithic chip, the Atmel AT89S51 is a powerful

microcontroller which provides a highly-flexible and cost-effective solution to many

embedded control applications.

The AT89S51 provides the following standard features: 4K bytes of Flash, 128

bytes of RAM, 32 I/O lines, Watchdog timer, two data pointers, two 16-bit

timer/counters, a five-vector two-level interrupt architecture, a full duplex serial port,

on-chip oscillator, and clock circuitry. In addition, the AT89S51 is designed with static

logic for operation down to zero frequency and supports two software selectable power

saving modes.

The Idle Mode stops the CPU while allowing the RAM, timer/counters, serial port,

and interrupt system to continue functioning. The Power-down mode saves the RAM

contents but freezes the oscillator, disabling all other chip functions until the next

external interrupt or hardware reset.

2 Ports

Port 0 is an 8-bit open drain bi-directional I/O port. As an output port, each pin can

sink eight TTL inputs. When 1s are written to port 0 pins, the pins can be used as

high-impedance inputs. Port 0 can also be configured to be the multiplexed low-order

address/data bus during accesses to external program and data memory. In this mode, P0

has internal pull-ups. Port 0 also receives the code bytes during Flash programming and

中北大学 2010 届毕业设计中英文翻译

2

outputs the code bytes during program verification. External pull-ups are required during

program verification.

Port 1 is an 8-bit bi-directional I/O port with internal pull-ups. The Port 1 output

buffers can sink/source four TTL inputs. When 1s are written to Port 1 pins, they are

pulled high by the internal pull-ups and can be used as inputs. As inputs, Port 1 pins that

are externally being pulled low will source current (I

IL

) because of the internal pull-ups.

Port 1 also receives the low-order address bytes during Flash programming and

verification.

Port 2 is an 8-bit bi-directional I/O port with internal pull-ups. The Port 2 output

buffers can sink/source four TTL inputs. When 1s are written to Port 2 pins, they are

pulled high by the internal pull-ups and can be used as inputs. As inputs, Port 2 pins that

are externally being pulled low will source current (I

IL

) because of the internal

pull-ups.Port 2 emits the high-order address byte during fetches from external program

memory and during accesses to external data memory that use 16-bit addresses (MOVX

@ DPTR). In this application, Port 2 uses strong internal pull-ups when emitting 1s.

During accesses to external data memory that use 8-bit addresses (MOVX @ RI), Port 2

emits the contents of the P2 Special Function Register. Port 2 also receives the

high-order address bits and some control signals during Flash programming and

verification.

Port 3 is an 8-bit bi-directional I/O port with internal pull-ups. The Port 3 output

buffers can sink/source four TTL inputs. When 1s are written to Port 3 pins, they are

pulled high by the internal pull-ups and can be used as inputs. As inputs, Port 3 pins that

are externally being pulled low will source current (I

IL

) because of the pull-ups. Port 3

receives some control signals for Flash programming and verification. Port 3 also serves

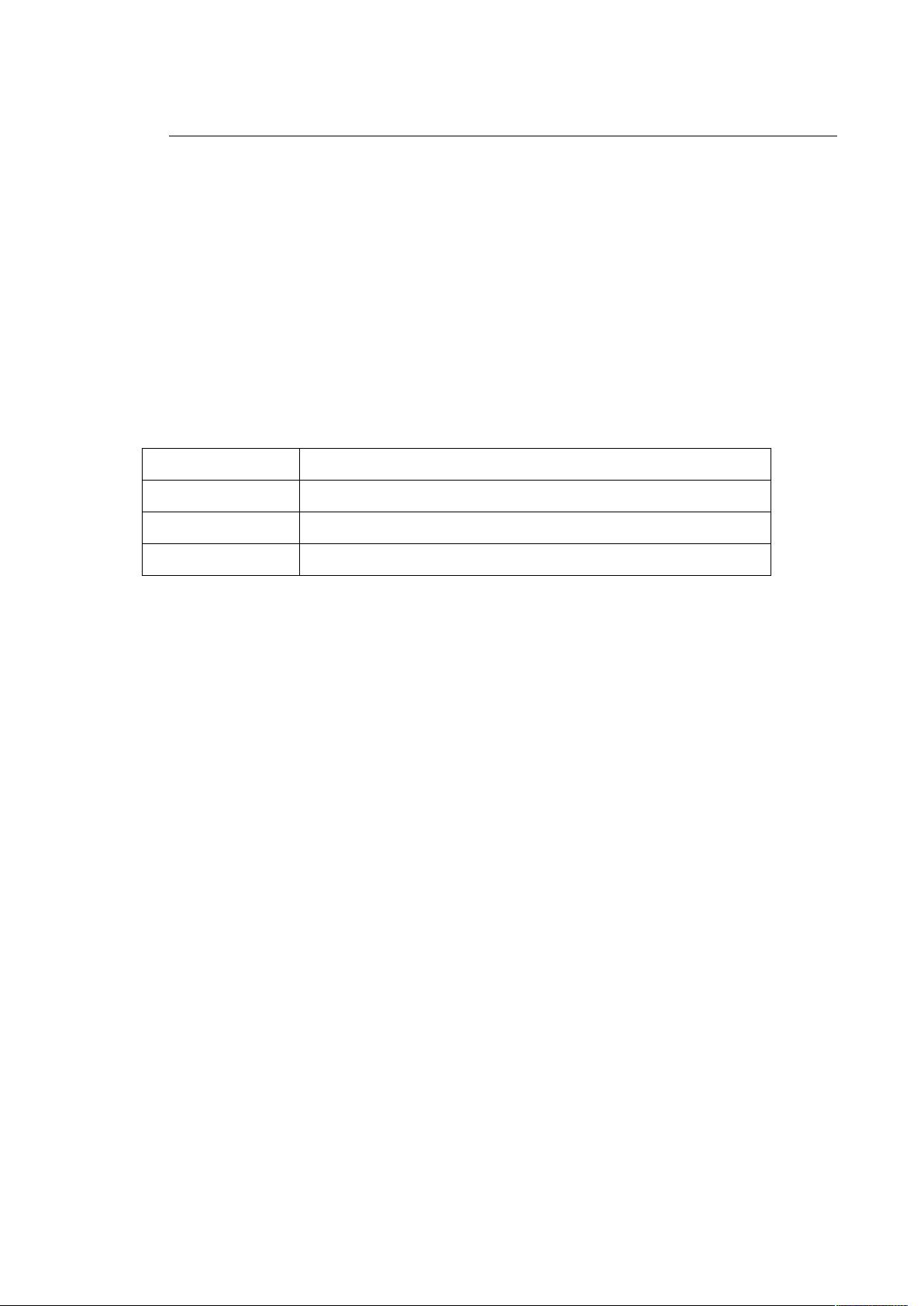

Port Pin

Alternate Functions

P1.5

MOSI (used for In-System Programming)

P1.6

MOSO (used for In-System Programming)

P1.7

SCK(used for In-System Programming)

中北大学 2010 届毕业设计中英文翻译

3

the functions of various special features of the AT89S51, as shown in the following

table.

3 Memory Organization

MCS-51 devices have a separate address space for Program and Data Memory. Up

to 64K bytes each of external Program and Data Memory can be addressed.

3.1 Program Memory

If the EA pin is connected to GND, all program fetches are directed to external

memory. On the AT89S51, if EA is connected to V

CC

, program fetches to addresses

0000H through FFFH are directed to internal memory and fetches to addresses 1000H

through FFFFH are directed to external memory.

3.2 Data Memory

The AT89S51 implements 128 bytes of on-chip RAM. The 128 bytes are accessible

via direct and indirect addressing modes. Stack operations are examples of indirect

addressing, so the 128 bytes of data RAM are available as stack space.

4 Watchdog Timer (One-time Enabled with Reset-out)

The WDT is intended as a recovery method in situations where the CPU may be

subjected to software upsets. The WDT consists of a 14-bit counter and the Watchdog

Timer Reset (WDTRST) SFR. The WDT is defaulted to disable from exiting reset. To

enable the WDT, a user must write 01EH and 0E1H in sequence to the WDTRST

Port Pin

Alternate Functions

P3.0

RXD(serial input port)

P3.1

TXD(serial output port)

P3.2

INT0(external interrupt 0)

P3.3

INT1(external interrupt 1)

P3.4

T0(timer 0 external input)

P3.5

T1(timer 1 external input)

P3.6

WR(external data memory write strobe)

P3.7

RD(external data memory read strobe)

剩余11页未读,继续阅读

资源评论

zzzzl333

- 粉丝: 674

- 资源: 7万+

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功