eda复习要点全.pdf

2.虚拟产品一经售出概不退款(资源遇到问题,请及时私信上传者)

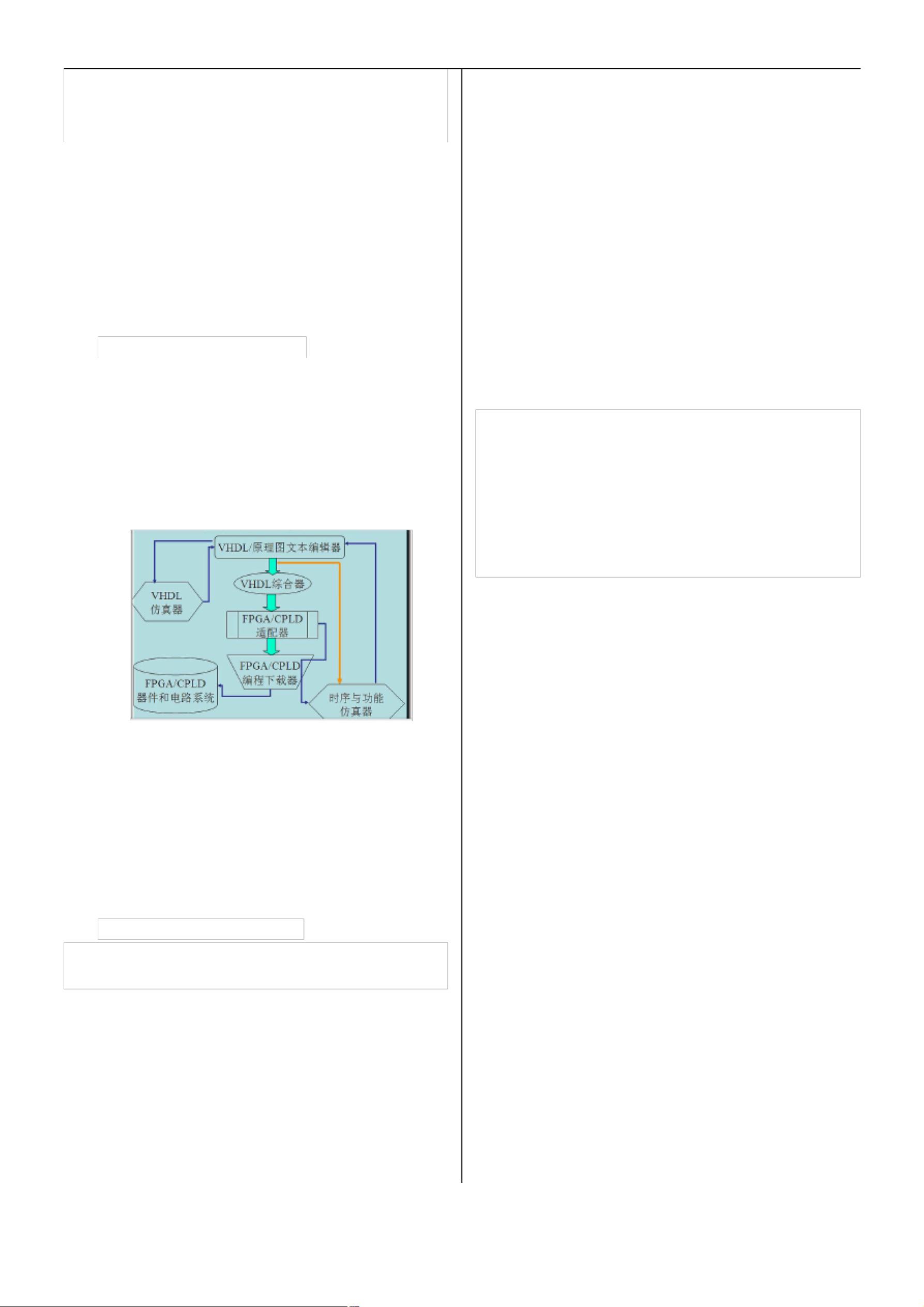

【EDA技术复习要点】 EDA(Electronic Design Automation)是电子设计自动化技术,主要用于集成电路设计和系统级设计。在EDA中,VHDL(Very High Speed Integrated Circuit Hardware Description Language)是一种广泛使用的硬件描述语言,用于描述数字系统的结构和行为。 1. **VHDL描述语句类型**:VHDL的描述语句分为顺序执行语句(Sequential)和并行执行语句(Parallel)。顺序执行语句遵循传统的编程语法规则,如过程和函数,而并行执行语句描述并行发生的行为,如进程(Process)。 2. **硬件描述语言**:除了VHDL,常见的硬件描述语言还包括ABEL-HDL, AHDL, Verilog-HDL。VHDL和Verilog-HDL被IEEE标准化,并广泛应用于现代数字系统设计。 3. **MAX+PLUS2文件扩展名**:在MAX+PLUS2工具中,设计文件的扩展名包括.vhd(VHDL源代码)、.sym(符号表)、.gdf(图形设备文件)和.scf(配置文件)。 4. **基于MAX+PLUS2的设计流程**:涵盖了设计输入、编译处理、功能仿真、时序仿真、定时分析和器件编程等步骤。 5. **流行EDA设计软件**:ALTERA公司的MAX+PLUS II和QUARTUS II,LATTICE莱迪思公司的ispEXPERT和DesignExpert,以及XILINX公司的FOUNDATION ISE都是重要的EDA工具。 6. **可编程逻辑器件分类**:分为SPLD、CPLD、FPGA和ISP器件。按照编程工艺又可以分为熔丝开关型、可编程低阻电路元件、EPROM型、E PROM型和基于SRAM的编程元件。 7. **VHDL程序设计的库**:主要包括IEEE库、STD库、WORK库、VITAL库和用户定义库。其中,IEEE库、用户定义库和VITAL库是显示库,而STD库和WORK库是隐式库。 8. **程序包的组成部分**:程序包由程序包首和程序包体两部分组成,前者定义接口,声明类型、元件、函数和子程序,后者实现实际功能。 9. **预定义程序包**:如STD_LOGIC_1164、STD_LOGIC_ARITH、STD_LOGIC_UNSIGNED、STD_LOGIC_SIGNED、STANDARD和TEXTIO等,可以通过包含语句进行调用。 10. **大型EDA器件制造商**:ALTERA、LATTICE和XILINX是国际上知名的EDA器件供应商。 11. **VHDL预定义数据类型**:包括布尔型(BOOLEAN)、位型(BIT)、位矢量型(BIT_VECTOR)、字符型(CHARACTER)等,这些类型在对应的程序包中定义,通过包含相应库进行调用。 12. **数据类型转换**:可通过函数转换、类型标记转换和常数转换法实现。 13. **标识符规则**:标识符由英文字母、数字和下划线组成,必须以字母开头,且不能与VHDL保留字冲突。 14. **PLD分类**:根据编程特性,PLD可分为一次编程和重复编程两类。 15. **标准逻辑位数据类型**:包括'U'(未初始化)、'X'(强未知)、'0'(强0)、'1'(强1)、'Z'(高阻态)、'W'(弱未知)、'L'(弱0)、'H'(弱1)和'-'(忽略)。 16. **条件语句电路**:完整的条件语句产生组合逻辑电路,而不完整的条件语句产生时序逻辑电路。 17. **信号与变量的区别**: - 信号具有延迟,变量则无延迟。 - 信号存储历史信息,变量仅存储当前值。 - 进程对信号敏感,不对变量敏感。 - 信号可作为多个进程间通信的全局信号,而变量仅在其定义域内可见(除非是共享变量)。 - 信号模拟硬件连线,变量用于高级建模的计算。 - 信号赋值使用"<=",变量赋值使用":"=”。 18. **VHDL标准制定**:VHDL由IEEE(电气和电子工程师协会)制定并公布,是集成电路设计的工业标准。 以上是EDA技术及VHDL的关键知识点,涵盖了语言特性、设计流程、工具应用以及硬件描述语言的基本概念。了解并掌握这些内容对于进行数字系统设计至关重要。

剩余11页未读,继续阅读

- 粉丝: 1w+

- 资源: 6万+

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

信息提交成功

信息提交成功