《EDA 与数字系统设计》实验报告

实验二 7 段数码显示译码器

【实验目的】

1. 设计七段显示译码器,并在实验板上验证

2. 学习Verilog HDL文本文件进行逻辑设计输入;

3. 学习设计仿真工具的使用方法;

【实验内容】

1. 实现 BCD/七段显示译码器的“ Verilog ”语言设计。

说明:7 段显示译码器的输入为:IN0…IN3 共 5 根, 7 段译码器的逻辑表同学自行

设计,要求实现功能为:输入“ 0…15 ”(二进制),输出“ 0…9…F ”(显示数码),

输出结果应在数码管(共阴)上显示出来。

2. 使用工具为译码器建立一个元件符号

3. 设计仿真文件,进行验证。

4.编程下载并在实验箱上进行验证。

【实验原理】

7 段数码是纯组合电路,通常的小规模专用 IC,如 74 或 4000 系列的器件只能作十

进制 BCD 码译码,然而数字系统中的数据处理和运算都是 2 进制的,所以输出表达都是

16 进制的。为了满足 16 进制数的译码显示,利用 Verilog 译码程序在 FPGA/CPLD 中来

实现。首先要设计一段程序,该程序可用 case 语句表述方法,根据真值表写出程序。

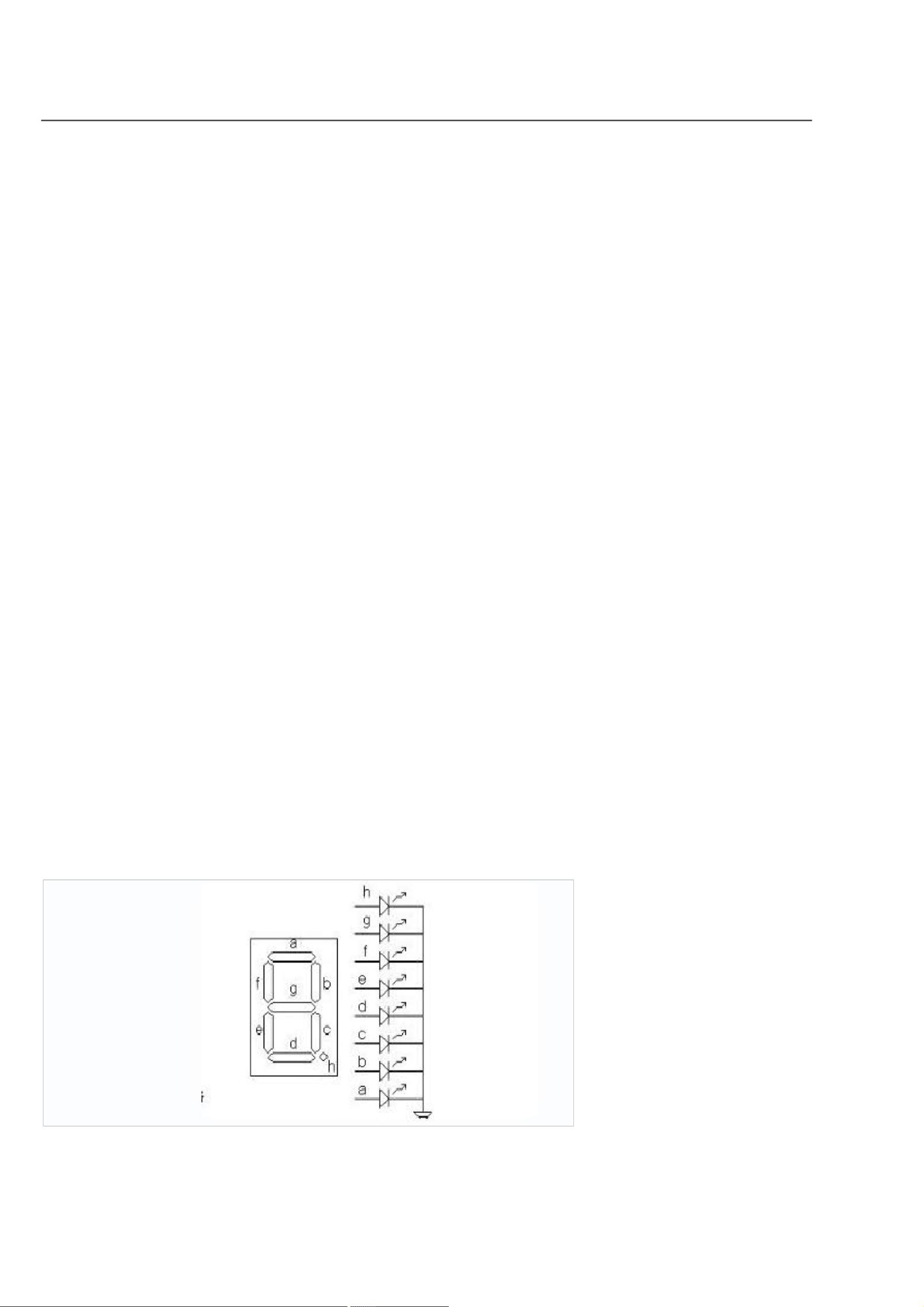

设输入的 4 位码为 IN[3:0],输出控制 7 段共阴数码管的七位数据为 led7[6:0]。首先完

成 7 段 BCD 码译码器的设计。本实验中的 7 段译码管输出信号 led7 的 7 位分别接数码

管的 7 个段,高位在左,低位在右。如当 LED7 输出为“1101111”时,数码管的 7 个段:

a,b,c,d,e,f,g 分别接 1、1、1、1、0、1、1;接有高电平的段发亮,于是数码管显示

“9”。

【共阴数码管】

第 - 1 - 页 共 5 页

评论0

最新资源