没有合适的资源?快使用搜索试试~ 我知道了~

NXP公司LPC32x0系列user manual(用户设计手册)

温馨提示

试读

723页

NXP公司LPC32x0系列芯片用户设计手册,PDF文档,761页,包含LPC3220,LPC3230,LPC3240,LPC3250芯片。是设计LPC32x0系列芯片依据。

资源推荐

资源详情

资源评论

UM10326

LPC32x0 User manual

Rev. 1 — 18 February 2009 User manual

Document information

Info Content

Keywords LPC3220, LPC3230, LPC3240, LPC3250, ARM9, 16/32-bit ARM

microcontroller.

Abstract User manual for LPC32x0.

UM10326_1 © NXP B.V. 2009. All rights reserved.

User manual Rev. 1 — 18 February 2009 2 of 723

Contact information

For more information, please visit: http://www.nxp.com

For sales office addresses, please send an email to: salesaddresses@nxp.com

NXP Semiconductors

UM10326

LPC32x0 User manual

Revision history

Rev Date Description

1 20090218 Initial LPC32x0 user manual release.

UM10326_1 © NXP B.V. 2009. All rights reserved.

User manual Rev. 1 — 18 February 2009 3 of 723

1. Introduction

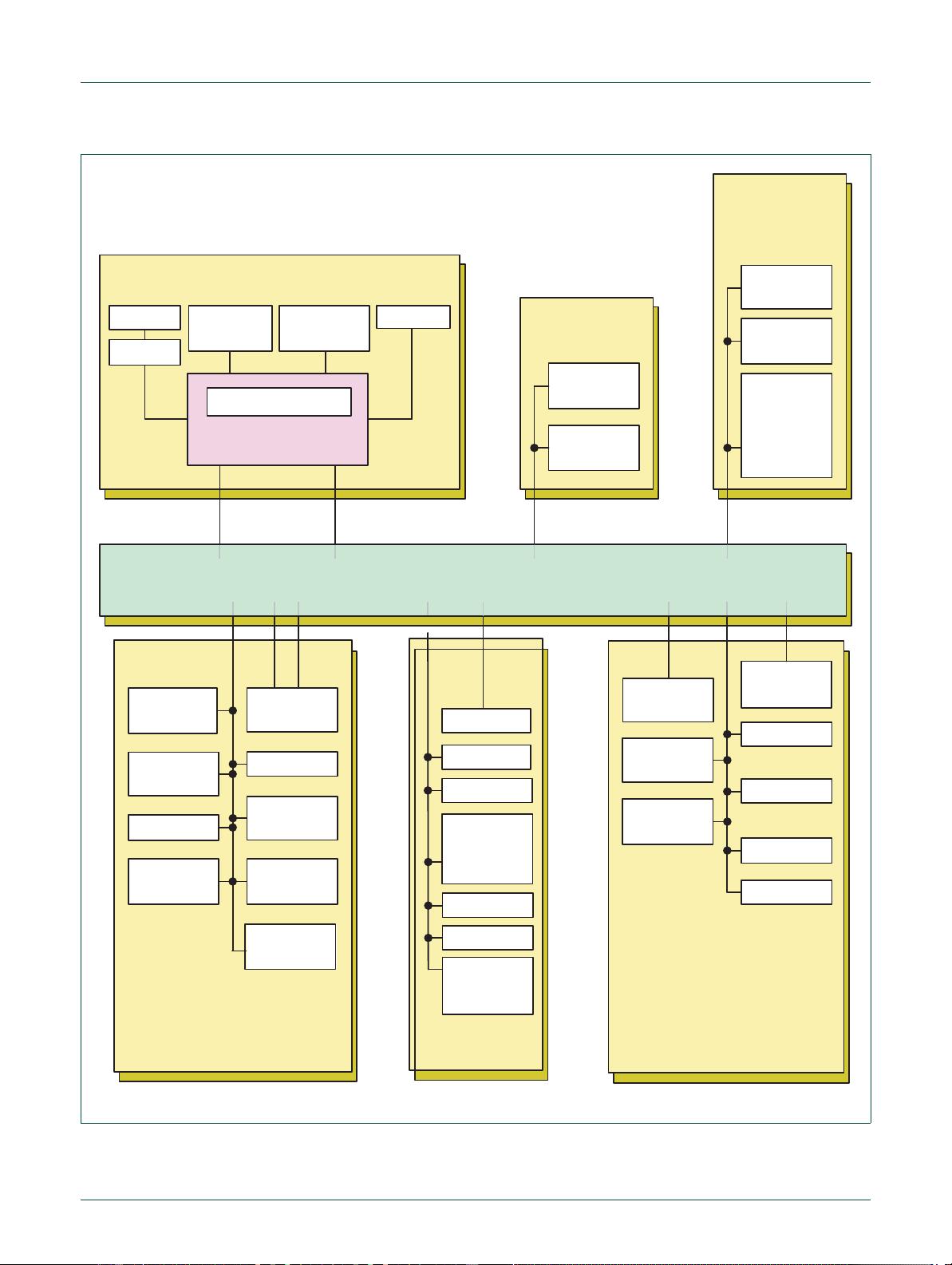

NXP Semiconductor designed the LPC32x0 for embedded applications requiring high

performance and low power consumption.

NXP achieved their performance objectives using an ARM926EJ-S CPU core with a

Vector Floating Point co-processor and a large set of standard peripherals, including USB

On-The-Go. Figure 1 shows a block diagram of the LPC32x0. The LPC32x0 operates at

CPU frequencies up to 266 MHz. The basic ARM926EJ-S CPU Core implementation uses

a Harvard architecture with a 5-stage pipeline. The ARM926EJ-S core also has an

integral Memory Management Unit (MMU) to provide the virtual memory capabilities

required to support the multi-programming demands of modern operating systems. The

basic ARM926EJ-S core also includes a set of DSP instruction extensions including single

cycle MAC operations and native Jazelle Java Byte-code execution in hardware. The NXP

implementation has one 32 KB Instruction Cache and one 32 KB Data Cache.

For low power consumption, the LPC32x0 takes advantage of NXP Semiconductor's

advanced technology development expertise to optimize Intrinsic Power, and software

controlled architectural enhancements to optimize Power Management.

The LPC32x0 also includes 128 to 256 KB of on-chip static RAM, a NAND Flash interface,

an Ethernet MAC, an LCD controller that supports STN and TFT panels, and an external

bus interface that supports SDR and DDR SDRAM as well as static devices. In addition,

the LPC32x0 includes a USB 2.0 Full Speed interface, seven UARTs, two I2C interfaces,

two SPI/SSP ports, two I2S interfaces, two single output PWMs, a motor control PWM,

four general purpose timers with capture inputs and compare outputs, a Secure Digital

(SD) interface, and a 10-bit A/D converter with a touch screen sense option.

UM10326

Chapter 1: LPC32x0 Introductory information

Rev. 1 — 18 February 2009 User manual

UM10326_1 © NXP B.V. 2009. All rights reserved.

User manual Rev. 1 — 18 February 2009 4 of 723

NXP Semiconductors

UM10326

Chapter 1: LPC32x0 Introductory information

Fig 1. LPC32x0 diagram

External

Memory

Interfaces

System Functions

CPU subsystem

ARM926EJ

Instr Data

I-Cache

32kB

D-Cache

32kB

ETB VFP9

DMA

Controller

ETM9

On-Chip

Memory

ROM

256 kB

SRAM

Other

Peripherals

Bus matrix (Multi-layer AHB)

Watchdog

High Speed

Timer

Millisecond

Timer

Power

Control

PLLs

System

Control

Interrupt

Controller

PWM 1, 2

Touch

Screen/

10-bit A/D

Keyscan

GPIO

Motor

Control

PWM

Communication

Peripherals

USB OTG

UART6

IrDA

UART

1-5, 7

I2C 1, 2

I2S 0, 1

SPI 1, 2

SSP 0, 1

NAND

Flash

SRAM and

SDRAM

(SDR/

DDR)

control

SD Card

Timer

LCD

Ethernet

MAC

RTC

0,1,2,3,4,5

UM10326_1 © NXP B.V. 2009. All rights reserved.

User manual Rev. 1 — 18 February 2009 5 of 723

NXP Semiconductors

UM10326

Chapter 1: LPC32x0 Introductory information

2. Features

• ARM926EJS processor, running at CPU clock speeds up to 266 MHz

• A Vector Floating Point coprocessor.

• A 32 KB instruction cache and a 32 KB data cache.

• Up to 256 KB of internal SRAM.

• Selectable boot-up from various external devices: NAND Flash, SPI memory, USB,

UART, or static memory.

• A Multi-layer AHB system that provides a separate bus for each AHB master,

including both an instruction and data bus for the CPU, two data busses for the DMA

controller, and another bus for the USB controller, one for the LCD and a final one for

the Ethernet MAC. There are no arbitration delays in the system unless two masters

attempt to access the same slave at the same time.

• An External memory controller for DDR and SDR SDRAM, as well as static devices.

– The address bus provides up to 16 MB for each of the 4 static chip selects.

– The controller provides two dynamic memory chip selects addressing up to

512 MB each.

• Two NAND Flash controllers. One for single level NAND Flash devices and the other

for multi-level NAND Flash devices.

• An Interrupt Controller, supporting 73 interrupt sources.

• An eight channel General Purpose AHB DMA controller (GPDMA) that can be used

with the SD card port, the 14-clock UARTs, I2S ports, and SPI interfaces, as well as

memory-to-memory transfers.

• Serial Interfaces:

– A 10/100 Ethernet MAC with dedicated DMA Controller.

– A USB interface supporting either Device, Host (OHCI compliant), or On-The-Go

(OTG) with an integral DMA controller and dedicated PLL to generate the required

48 MHz USB clock.

– Four standard UARTs with fractional baud rate generation and 64 byte FIFOs. One

of the standard UART’s supports IrDA.

– Three additional 14-clock UARTs intended for on-board communications that

support baudrates up to 921,600 bps when using a 13 MHz main oscillator.All

14-clock UARTs provide 64-byte FIFOs

– Two SPI controllers.

– Two SSP controllers

– Two I2C-bus Interfaces with standard open drain pins. The I2C-bus Interfaces

support single master, slave and multi-master I2C configurations.

– Two I2S interfaces, each with separate input and output channels. Each channel

can be operated independently on 3 pins, or both input and output with one I2S

interface can be done on only 4 pins.

• Additional Peripherals:

– LCD controller supporting both STN and TFT panels, with dedicated DMA

controller. Programmable display resolution up to 1024x768.

– Secure Digital (SD) memory card interface.

剩余722页未读,继续阅读

资源评论

wuhaiyunyiyi2012-11-20是2008年的,下载的时候注意下

wuhaiyunyiyi2012-11-20是2008年的,下载的时候注意下 奈斯吆西2012-12-29还行 标准的资料

奈斯吆西2012-12-29还行 标准的资料 robincsu2012-05-22不错,找了好久才找到,是官方的用户手册

robincsu2012-05-22不错,找了好久才找到,是官方的用户手册 quick2202014-02-17虽然不是最新的,可以参考

quick2202014-02-17虽然不是最新的,可以参考 gilbertbit2012-12-19目前最新的到2010年,不过变化不大

gilbertbit2012-12-19目前最新的到2010年,不过变化不大

Kevin-Lee

- 粉丝: 17

- 资源: 87

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功