2

TAS5720A-Q1

SLOS989B –NOVEMBER 2017–REVISED NOVEMBER 2019

www.ti.com

Product Folder Links: TAS5720A-Q1

Submit Documentation Feedback Copyright © 2017–2019, Texas Instruments Incorporated

Table of Contents

1 Features.................................................................. 1

2 Applications ........................................................... 1

3 Description ............................................................. 1

4 Revision History..................................................... 2

5 Pin Configuration and Functions......................... 3

6 Specifications......................................................... 5

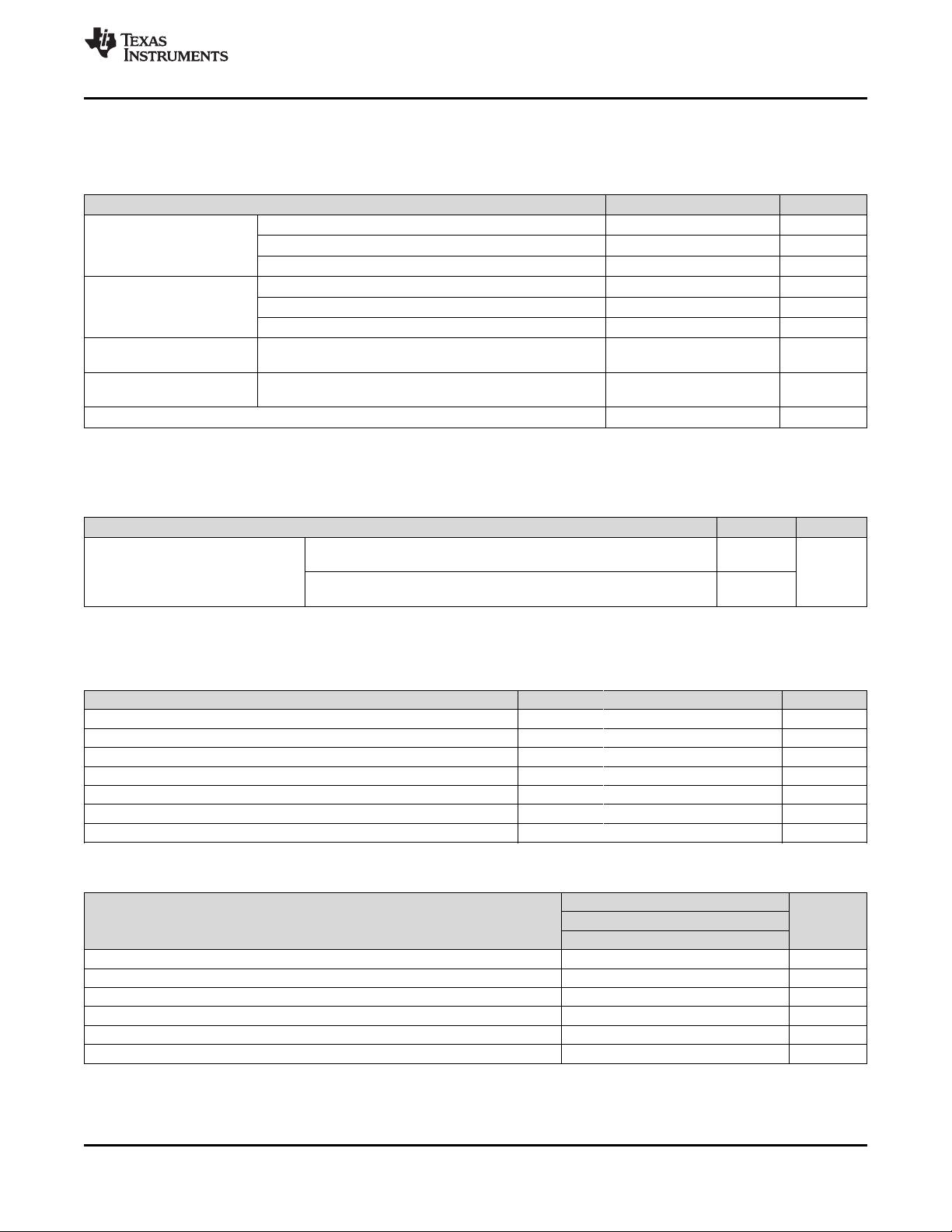

6.1 Absolute Maximum Ratings ..................................... 5

6.2 ESD Ratings.............................................................. 5

6.3 Recommended Operating Conditions....................... 5

6.4 Thermal Information.................................................. 5

6.5 Digital I/O Pins .......................................................... 6

6.6 Master Clock ............................................................. 6

6.7 Serial Audio Port....................................................... 6

6.8 Protection Circuitry.................................................... 7

6.9 Speaker Amplifier in All Modes................................. 8

6.10 Speaker Amplifier in All Modes............................... 9

6.11 I²C Control Port..................................................... 10

6.12 Typical Idle, Mute, Shutdown, Operational Power

Consumption............................................................ 10

6.13 Typical Characteristics (Mono Mode): f

SPK_AMP

=

384 kHz.................................................................... 11

7 Parameter Measurement Information ................ 11

8 Detailed Description............................................ 12

8.1 Overview ................................................................. 12

8.2 Functional Block Diagram ....................................... 12

8.3 Feature Description................................................. 12

8.4 Device Functional Modes........................................ 17

8.5 Register Maps......................................................... 25

9 Application and Implementation ........................ 33

9.1 Application Information............................................ 33

9.2 Typical Applications ................................................ 33

10 Power Supply Recommendations ..................... 38

10.1 DVDD Supply........................................................ 38

10.2 PVDD Supply ........................................................ 38

11 Layout................................................................... 38

11.1 Layout Guidelines ................................................. 38

11.2 Layout Example .................................................... 41

12 Device and Documentation Support ................. 42

12.1 Documentation Support ........................................ 42

12.2 Support Resources ............................................... 42

12.3 Trademarks........................................................... 42

12.4 Electrostatic Discharge Caution............................ 42

12.5 Glossary................................................................ 42

13 Mechanical, Packaging, and Orderable

Information ........................................................... 42

4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

Changes from Revision A (July 2018) to Revision B Page

• Added Feature: Temperature grade 1: –40°C to +125°C....................................................................................................... 1

• Added Junction Temperature, T

J

to the Absolute Maximum Ratings..................................................................................... 5

• Added HBM and CDM classification levels to the ESD Ratings ........................................................................................... 5

• Changed Note 2 From: JEDEC Standard 4 Layer Board To: JEDEC Standard 2 Layer Board in the Thermal Information. 5

• Changed the OCE

THRES

parameter From: Overcurrent Error (OCE) Threshold for each output To: Overcurrent Error

(OCE) Threshold in Protection Circuitry ................................................................................................................................. 7

• Changed Figure 24, removed the PVDD pin connection to Speaker output ....................................................................... 33

Changes from Original (November 2017) to Revision A Page

• Released as Production Data................................................................................................................................................. 1

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜

信息提交成功

信息提交成功