### EDA技术基础及VHDL语言

#### EDA技术基础知识及VHDL硬件描述语言概览

**电子设计自动化(EDA)技术**是现代集成电路设计的重要组成部分,它通过计算机辅助设计工具帮助工程师进行电路设计、模拟仿真以及验证等工作。在EDA领域中,**VHDL(Very High Speed Integrated Circuit Hardware Description Language)**是一种广泛使用的硬件描述语言,用于描述数字系统的结构和行为,并能够被转换成实际的硬件电路。

#### VHDL语言的基本结构

VHDL程序的设计遵循一套特定的结构,主要包括以下几个方面:

1. **实体(ENTITY)**: 实体定义了电路模块的外部接口,包括输入和输出端口。它是VHDL设计实体的最外层封装,用于描述硬件模块的接口特性。例如,在设计一个加法器时,实体会定义其输入(如两个加数)和输出(和)的端口。

2. **构造体(ARCHITECTURE)**: 构造体描述了实体内部的具体逻辑行为。一个实体可以有多个构造体,每个构造体代表不同的实现方法。构造体包含了设计实体的行为描述、数据流描述或者结构描述。

3. **配置(CONFIGURATION)**: 配置用来指定特定构造体的使用方式,尤其是在使用多个构造体的情况下,可以通过配置指定哪个构造体被采用。

4. **包集合(PACKAGE)**: 包集合是一组数据类型、常数、子程序等的集合,可以被多个设计实体共享。这有助于代码的重用性和模块化。

5. **库(LIBRARY)**: 库是存储预定义的数据类型、包集合、实体等的集合。库允许用户访问标准的VHDL库或自定义库中的组件。

#### VHDL程序设计基本单元及其构成

##### 实体说明

实体定义了设计实体与外界交互的接口。实体语句结构如下:

```vhdl

ENTITY 实体名 IS

[GENERIC(类属表);] -- 类属参数,用于传递配置信息

PORT(端口表); -- 输入输出端口定义

END ENTITY 实体名;

```

其中:

- **类属参数说明** (`GENERIC`): 可以用来传递配置信息,如数据宽度等。

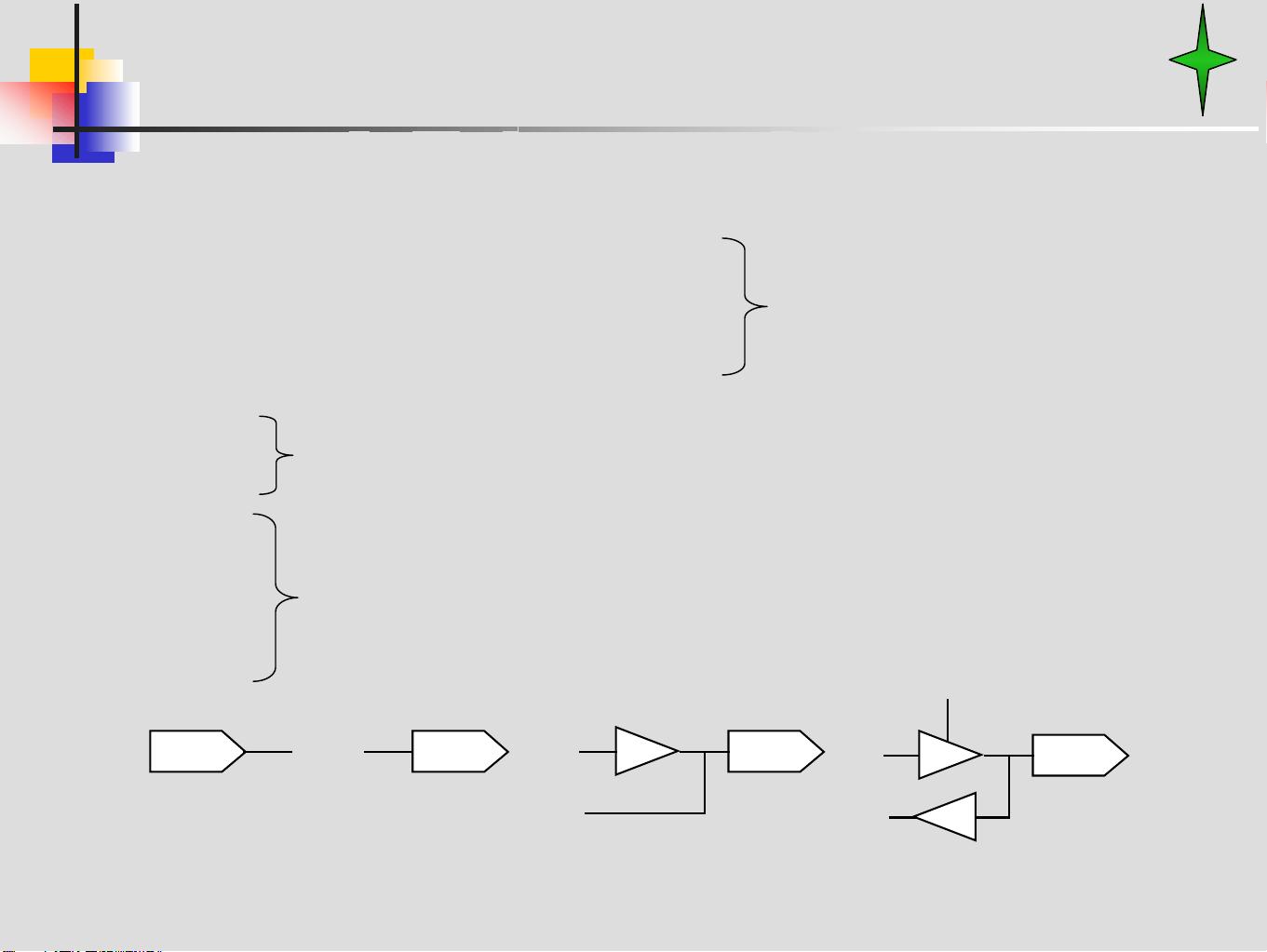

- **端口说明** (`PORT`): 描述设计实体的输入输出接口。端口的方向包括 `IN` (输入),`OUT` (输出),`INOUT` (双向),`BUFFER` (具有读出功能的输出模式)。

##### 构造体

构造体描述了实体内部的逻辑结构和行为。构造体的基本结构如下:

```vhdl

ARCHITECTURE 构造体名 OF 实体名 IS

-- 定义语句

BEGIN

-- 功能描述语句

END ARCHITECTURE 构造体名;

```

构造体中的主要组成部分包括:

- **定义语句**:用于定义信号、常数、数据类型和子程序等。

- **功能描述语句**:包括块语句、进程语句、信号赋值语句、子程序调用语句和元件例化语句等,这些语句描述了设计实体的具体行为。

##### 子结构描述

子结构是VHDL中用于模块化设计的重要概念,主要包括以下几种:

1. **BLOCK语句结构**:用于将一组相关的语句组织起来,形成一个单独的逻辑单元。BLOCK语句本身属于并行语句,可以在其他并行语句中使用。

2. **PROCESS语句结构**:是VHDL最具特色的一种结构,用于描述顺序执行的行为。一个进程可以包含顺序语句,并且可以被触发执行。

3. **SUBPROGRAM语句结构**:指的是子程序(函数和过程),它们可以被其他部分调用,用于实现更高级别的抽象和模块化。

通过这些基本结构和子结构的组合,VHDL提供了强大的设计能力,使得设计者能够高效地描述复杂的数字系统,并将其转换为实际的硬件电路。